UNIVERSITY OF OSLO Department of Informatics

Detection of Junk Instructions in Computer Viruses

Master thesis

Egil Aspevik Martinsen

June 2nd 2008

## Abstract

The techniques employed by viruses to avoid detection by antivirus scanners are becoming increasingly advanced. One technique commonly used by viruses to evade detection is *polymorphism*. The level of polymorphism in a virus indicates its ability to create different forms of itself. The use of *junk instructions* is a common technique to increase the level of polymorphism in a virus. Junk instructions are machine code instructions with no other function than to alter the appearance of a virus. Junk instructions do not contribute to the function of the virus, only the form.

This master thesis focuses on the problem of separating junk instructions from nonjunk instructions in computer viruses. To assail the problem, a junk instruction detection (JID) framework has been developed, capable of detecting junk in viruses created for the Intel IA-32 Architecture (x86). JID relies on the *static instruction information* produced by a disassembler. Static instruction information describes the static information found in an instruction: the number of input/output operands and their accesses. Because JID only depends on the static instruction information, JID can possible be ported to other processor architectures. As long as there exist a disassembler for the architecture capable of producing static instruction information, JID is portable.

The results of testing JID on polymorphic viruses are promising. Tests show that JID manages to detect junk instructions found in the polymorphic virus Zmist. It is believed that JID would work as a tool to detect and remove junk instructions from future polymorphic viruses, thus reducing the time spent analysing the virus. Additionally in this thesis, the virus Zmist is analysed as a case study, and a detection algorithm devised. The detection algorithm manages to detect 100% of the polymorphic version of Zmist, although shortcomings in the disassembler algorithm reduces this number to 94%.

**Keywords:** Polymorphism, metamorphism, polymorphic, metamorphic, computer virus, malware, worm, junk instruction, garbage instruction, junk code, garbage code, Zmist

## Preface

This report presents the results of my master thesis "Detection of Junk Instructions in Computer Viruses". The report is a part of my Master's Degree in Computer Science at the Department of Informatics, University of Oslo. The contents of this report has its origin from a problem presented by the Norwegian antivirus company Norman ASA.

First of all, I would like to thank my supervisor Leif Nilsen at UNIK. His supreme ability to give constructive, detailed and mathematical precise guidance, has helped me a lot during my thesis work. Without his advices, the quality of the thesis would have been significantly lower and I am truly grateful for his patience and support in the finishing stages of the thesis.

I would like to thank Norman ASA who has provided me with a foundation for creating this thesis. Specially, I would like to thank Snorre Fagerland, my main contact at Norman, for answering numerous questions, steering me away from common pitfalls and providing me with the tools necessary to perform virus analysing. I would also like to thank Gunnar A. Johansen and Steve for helping me with the testing environment at Norman ASA. My fellow students Arne Hanssen and Sverre Krohn Tennøe deserve a big thanks for providing excellent technical input and for reviewing my thesis. Also, their social input have been of great value to me.

I would also like to thank my family and my in-laws for interrupting their daily duties to babysit our precious Lotte, while I and my wife Åshild attended to our theses. They have also provided us with shelter, food and many laughs and I look forward to spending more time with them again.

The person who has helped me the most is my wife Åshild, and I owe her huge thanks. She has been my primary support when lacking motivation, and I could never have completed this without her. Åshild has taken care of Lotte, sacrificing her own work to give me time to devote myself to the thesis. She has also reviewed my thesis and provided me with many constructive suggestions.

Finally, I look forward spending more time with my daughter Lotte, who has had to put up with her fathers tedious work.

Oslo, June 2nd 2008 Egil Aspevik Martinsen

# Contents

| 1 | Intr | oductio | n                                     | 15 |

|---|------|---------|---------------------------------------|----|

|   | 1.1  | Motiva  | ation                                 | 15 |

|   | 1.2  | Proble  | m Statement                           | 16 |

|   | 1.3  | Thesis  | outline                               | 17 |

| 2 | Bacl | kground | d                                     | 19 |

|   | 2.1  | PE File | e format                              | 19 |

|   |      | 2.1.1   | PE File Structure and Headers         | 19 |

|   |      | 2.1.2   | Sections                              | 21 |

|   |      | 2.1.3   | Relocation Section                    | 22 |

|   |      | 2.1.4   | Import Section                        | 22 |

|   |      | 2.1.5   | Summary                               | 23 |

|   | 2.2  | x86 As  | ssembler Language                     | 23 |

|   |      | 2.2.1   | Intel Syntax and Examples             | 23 |

|   |      | 2.2.2   | Instruction Format                    | 24 |

|   |      | 2.2.3   | About the Basic Execution Environment | 25 |

|   |      | 2.2.4   | Instruction groups                    | 27 |

|   |      | 2.2.5   | Summary                               | 28 |

|   | 2.3  | Disass  | embling Algorithms                    | 28 |

|   |      | 2.3.1   | Linear sweep                          | 29 |

|   |      | 2.3.2   | Recursive traversal                   | 29 |

|   |      | 2.3.3   | Summary                               | 31 |

|   | 2.4  | Compu   | uter Viruses                          | 31 |

|   |      | 2.4.1   | Definitions                           | 31 |

|   |      | 2.4.2   | History                               | 32 |

|   |      | 2.4.3   | Encrypted Viruses                     | 35 |

|   |      | 2.4.4   | Polymorphic Viruses                   | 36 |

|   |      | 2.4.5    | Metamorphic Viruses                              | 36 |

|---|------|----------|--------------------------------------------------|----|

|   |      | 2.4.6    | Notation usage for poly- and metamorphic viruses | 37 |

|   |      | 2.4.7    | Achieving Polymorphism                           | 37 |

|   |      | 2.4.8    | Summary                                          | 39 |

|   | 2.5  | Compu    | Iter Virus Detection                             | 40 |

|   |      | 2.5.1    | Algorithmic Approaches                           | 41 |

|   |      | 2.5.2    | Emulation                                        | 43 |

|   |      | 2.5.3    | Heuristic Methods                                | 43 |

|   | 2.6  | Summa    | ary                                              | 45 |

| 3 | Case | e Study  |                                                  | 47 |

|   | 3.1  | Case S   | tudy Discussion                                  | 47 |

|   |      | 3.1.1    | Choosing a Case                                  | 47 |

|   |      | 3.1.2    | Methodology                                      | 48 |

|   |      | 3.1.3    | Tools used in Case Study                         | 49 |

|   |      | 3.1.4    | Gdasm                                            | 50 |

|   | 3.2  | Introdu  | action to Zmist                                  | 51 |

|   |      | 3.2.1    | Zmist Versions                                   | 52 |

|   |      | 3.2.2    | Code Integration                                 | 52 |

|   |      | 3.2.3    | Infection Mechanisms                             | 54 |

|   |      | 3.2.4    | Detection of JMP and Unencrypted Engine          | 55 |

|   | 3.3  | About    | the Polymorphic Decryptor Infection type         | 56 |

|   |      | 3.3.1    | Analysis of the Polymorphic Decryptor            | 56 |

|   |      | 3.3.2    | Code Examples of Decryptor                       | 59 |

|   |      | 3.3.3    | Polymorphic Techniques Employed                  | 59 |

|   | 3.4  | Detecti  | ion of the Polymorphic Decryptor                 | 62 |

|   |      | 3.4.1    | Geometric Properties                             | 62 |

|   |      | 3.4.2    | Detection by Instruction Statistic               | 63 |

|   |      | 3.4.3    | Detection by Decryptor Properties                | 66 |

|   | 3.5  | Summa    | ary                                              | 69 |

| 4 | Ana  | lysis an | d Lessons Learnt                                 | 71 |

|   | 4.1  | Case S   | tudy Aftermath                                   | 71 |

|   |      | 4.1.1    | Comparison Program                               | 71 |

|   | 4.2  | Motiva   | tion for Junk Instruction Detection              | 72 |

|   |      | 4.2.1    | Independence                                     | 73 |

|   |     | 4.2.2   | Other Uses                                                     | 73  |

|---|-----|---------|----------------------------------------------------------------|-----|

|   |     | 4.2.3   | Similar work                                                   | 73  |

|   |     | 4.2.4   | Conclusion                                                     | 74  |

| 5 | The | JID Fra | amework                                                        | 75  |

|   | 5.1 | Metho   | dology                                                         | 75  |

|   |     | 5.1.1   | General Limitations                                            | 75  |

|   |     | 5.1.2   | Assumptions                                                    | 75  |

|   |     | 5.1.3   | Method for Junk Instruction Detection                          | 76  |

|   |     | 5.1.4   | Conclusion                                                     | 76  |

|   | 5.2 | Introdu | action to JID                                                  | 77  |

|   |     | 5.2.1   | Framework Overview                                             | 77  |

|   |     | 5.2.2   | Classification                                                 | 78  |

|   |     | 5.2.3   | Elements of the Framework                                      | 80  |

|   |     | 5.2.4   | Summary                                                        | 80  |

|   | 5.3 | Definit | ions, Rules and properties of the Framework                    | 81  |

|   |     | 5.3.1   | Basic Terminology                                              | 81  |

|   |     | 5.3.2   | Information Flows                                              | 82  |

|   |     | 5.3.3   | Instruction Chains and Current Instruction                     | 82  |

|   |     | 5.3.4   | Flow set, FL                                                   | 84  |

|   |     | 5.3.5   | Entities                                                       | 85  |

|   |     | 5.3.6   | J and NJ Classifications of an Entity                          | 86  |

|   |     | 5.3.7   | J Classification Resolving                                     | 89  |

|   | 5.4 | x86 As  | ssembler Language and JID                                      | 90  |

|   |     | 5.4.1   | Immediate Operands                                             | 91  |

|   |     | 5.4.2   | Memory Operands                                                | 91  |

|   |     | 5.4.3   | 32-, 16- and 8-bit General-Purpose Registers                   | 92  |

|   |     | 5.4.4   | Segment-, FPU-, MMX-, XMM-, Control-, Debug- and MSR-registers | 94  |

|   |     | 5.4.5   | ESP Register (Stack)                                           | 94  |

|   |     | 5.4.6   | EFLAGS Register                                                | 95  |

|   | 5.5 | EIP Re  | gister and Control Transfer Instructions                       | 96  |

|   |     | 5.5.1   | Framework Limitations                                          | 96  |

|   |     | 5.5.2   | JMP, CALL, RET, IRET and End Of Disassembling                  | 97  |

|   |     | 5.5.3   | Conditional Jumps                                              | 98  |

|   | 5.6 | Instruc | tion Groups                                                    | 100 |

|   |       | 5.6.1    | Design of JID summary                           |

|---|-------|----------|-------------------------------------------------|

|   | 5.7   | Static S | Single Assignment                               |

|   |       | 5.7.1    | SSA/DCR                                         |

|   |       | 5.7.2    | Algorithm for Dead Code Elimination             |

|   |       | 5.7.3    | Use of SSA/DCR as a method for JID              |

| 6 | Testi | inσ      | 105                                             |

| Ū | 6.1   | 0        | oundation                                       |

|   | 0.11  | 6.1.1    | The Reason for Testing JID                      |

|   |       | 6.1.2    | How to measure J instructions                   |

|   | 6.2   |          | gJID                                            |

|   |       | 6.2.1    | Setup                                           |

|   |       | 6.2.2    | Gdasm and R                                     |

|   |       | 6.2.3    | Results                                         |

|   |       | 6.2.4    | Choosing a Statistical Method                   |

|   |       | 6.2.5    | Applying the Welch t-test                       |

|   | 6.3   | Testing  | g for NJ as J, and J as NJ                      |

|   |       | 6.3.1    | Junk Percentage Distribution                    |

|   |       | 6.3.2    | Manual Disassembling                            |

|   |       | 6.3.3    | Infected Files                                  |

|   |       | 6.3.4    | Evaluation                                      |

|   | 6.4   | Testing  | g of Zmist Decryptor Detection on Zmist Samples |

|   |       | 6.4.1    | Setup                                           |

|   |       | 6.4.2    | Results                                         |

|   |       | 6.4.3    | Evaluation                                      |

| 7 | Con   | clusion  | and Future Work 119                             |

| , | 7.1   |          | ary                                             |

|   | 7.2   |          | s                                               |

|   |       | 7.2.1    | Research Goal 1                                 |

|   |       | 7.2.2    | Research Goal 2                                 |

|   |       | 7.2.3    | Problem Statement                               |

|   |       | 7.2.4    | Similar Work                                    |

|   | 7.3   | Other I  | Results                                         |

|   |       | 7.3.1    | Libdisasm Patches                               |

|   | 7.4   | Future   | Work                                            |

|              | le, Zmist Listings and Files 1 | 23 |

|--------------|--------------------------------|----|

| A Source Cod | do Zmiet Lietings and Files    | 25 |

| 7.4.3        | Comparison Program             | 23 |

| 7.4.2        | Applying JID on Other Viruses  | 23 |

| /.4.1        | Detection of Zmist             | 22 |

| 7 4 1        |                                |    |

# **List of Tables**

| 2.1  | x86 Assembler Language Example 1                                            | 24  |

|------|-----------------------------------------------------------------------------|-----|

| 2.2  | x86 Assembler Language Example 2                                            | 24  |

| 2.3  | Example illustrating an instruction containing an unresolvable control flow | 30  |

| 2.4  | Instruction Equivalence                                                     | 37  |

| 2.5  | Instruction Reordering                                                      | 38  |

| 2.6  | Register Renaming                                                           | 38  |

| 2.7  | Reordering Data                                                             | 38  |

| 2.8  | Jump Islands                                                                | 39  |

| 2.9  | Junk Code                                                                   | 39  |

| 3.1  | Differences between Zmist versions                                          | 52  |

| 3.2  | Zmist receiving- and passing-control transfer instructions                  | 54  |

| 3.3  | Unusual conditional control transfer                                        | 58  |

| 3.4  | Code example of 3 Zmist decryptors                                          | 60  |

| 3.5  | Number of instruction (NOI) in two Zmist.A samples                          | 64  |

| 3.6  | Constructed example of an invalid decryptor considering register saves      | 67  |

| 5.1  | Junk instructions utilising memory                                          | 79  |

| 5.2  | Example illustrating NJ Classification and NJ recursion rule                | 86  |

| 5.3  | Example illustrating J rule                                                 | 87  |

| 5.4  | Expanded example illustrating J rule                                        | 88  |

| 5.5  | Instructions classified as J when opcode function is ignored                | 92  |

| 5.6  | AL treated as EAX                                                           | 93  |

| 5.7  | Example of junk instructions utilising the ESP register                     | 94  |

| 5.8  | Flag usage                                                                  | 95  |

| 5.9  | Deterministic Jcc                                                           | 98  |

| 5.10 | Example of regular code vs SSA treated code                                 | 102 |

| 5.11 | UD- and DU-chains for example 5.10 on page 102                              | 102 |

| 6.1 | Common sequences containing J                         | 113 |

|-----|-------------------------------------------------------|-----|

| 6.2 | libdisasm error                                       | 114 |

| 6.3 | Code example of 3 Zmist decryptors after applying JID | 116 |

# **List of Figures**

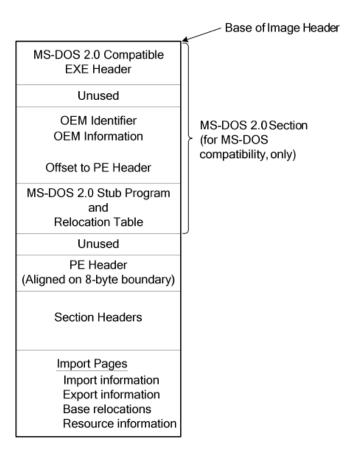

| 2.1 | Figure illustrating the Microsoft PE Executable format                                   | 20  |

|-----|------------------------------------------------------------------------------------------|-----|

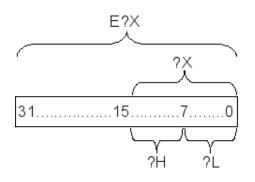

| 2.2 | The layout of E?X, ?X, ?H and ?L                                                         | 26  |

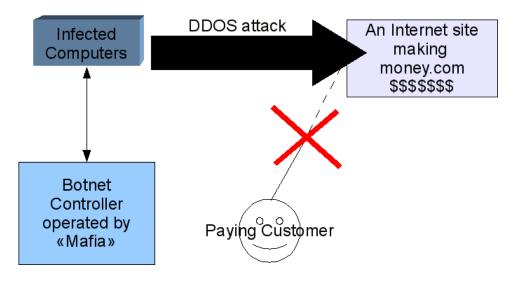

| 2.3 | Blackmailing scheme                                                                      | 33  |

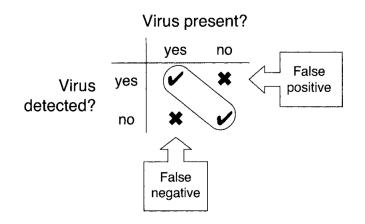

| 2.4 | Figure illustrating FP, FN, TP and TN                                                    | 40  |

| 2.5 | Example of term rewriting                                                                | 42  |

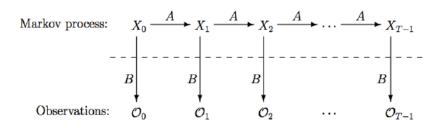

| 2.6 | Generic Hidden Markov Model figure                                                       | 44  |

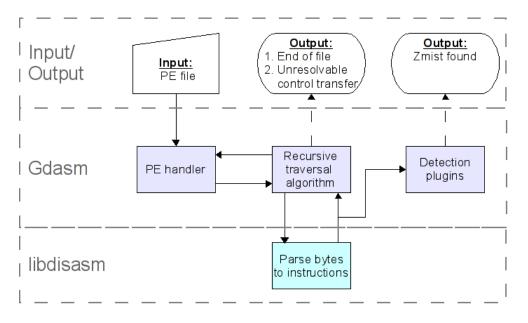

| 3.1 | Flow chart illustrating the Gdasm program                                                | 51  |

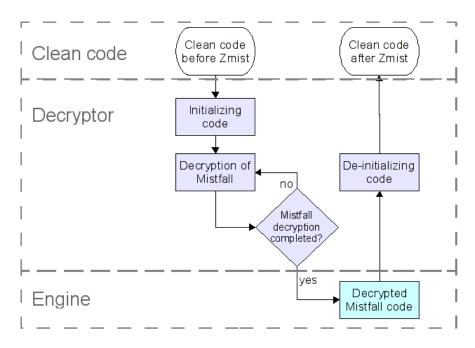

| 3.2 | pd-infection type flow chart                                                             | 57  |

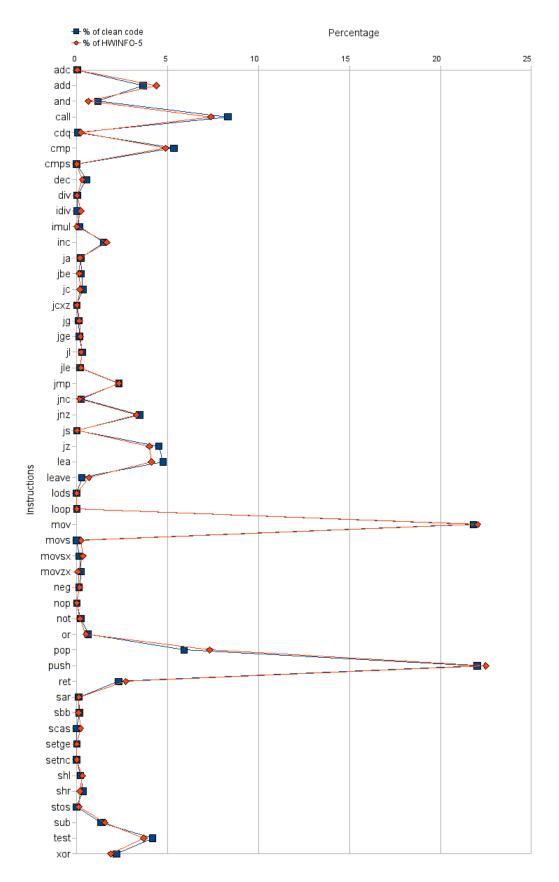

| 3.3 | Percentage of instructions found in HWINFO-5.VXE, plotted together clean code percentage | 65  |

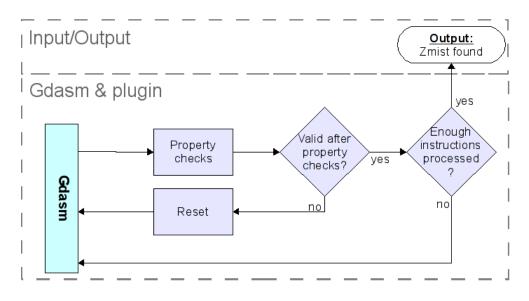

| 3.4 | Flow chart illustrating detector plugin for Gdasm                                        | 68  |

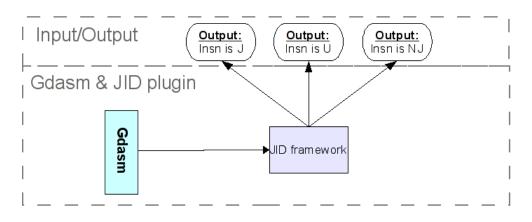

| 5.1 | Illustrating the general flow of the junk detecting framework                            | 77  |

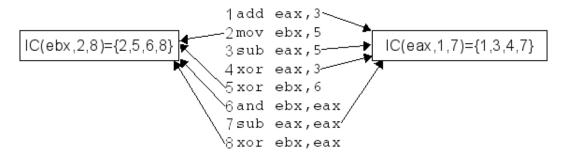

| 5.2 | Illustrating example instructions with corresponding IC's                                | 83  |

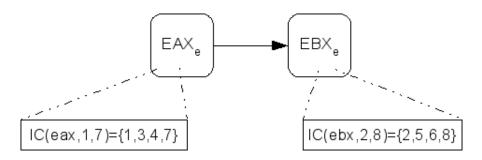

| 5.3 | Illustrating corresponding entities to the IC created in figure 5.2 on page 83           | 86  |

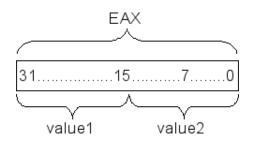

| 5.4 | The layout of EAX from the example in table 5.5 on page 92                               | 92  |

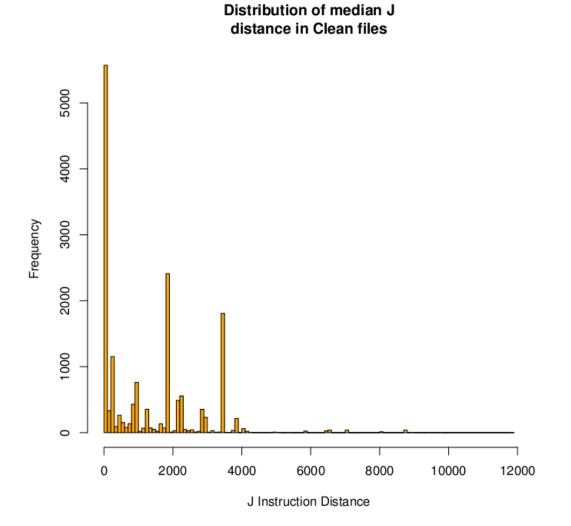

| 6.1 | J median distribution in Clean files                                                     | 109 |

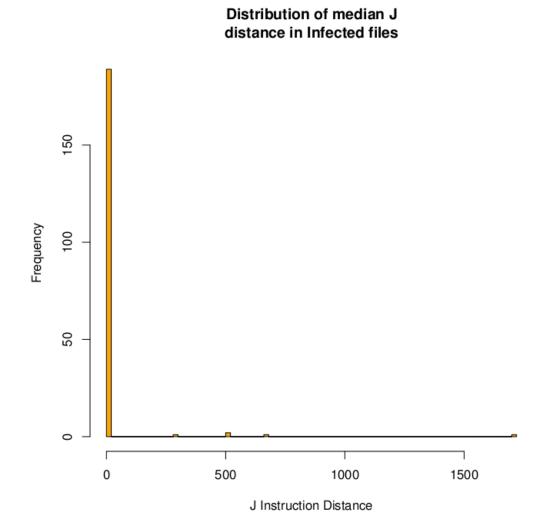

| 6.2 | J median distribution in Infected files                                                  | 110 |

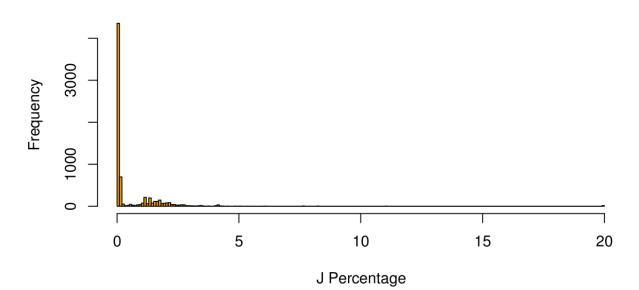

| 6.3 | Figure illustrating junk percentage distribution                                         | 113 |

## LIST OF FIGURES

## Chapter 1

## Introduction

The topic of this thesis is detection of junk instructions found in computer viruses. Junk instructions are one of many techniques used to increase the level of *polymorphism* in viruses. The expression polymorphism stems from Latin. Poly translates to "many" and morph translates to "form". The level of polymorphism in a virus indicates its ability to create different forms of itself. The higher the level of polymorphism, the greater variety between the forms. The traditional detection method is based on byte-signature scanning. The variety found in polymorphic viruses implies that each form requires an individual byte-signature. This leads to that the byte-signature approach in the context of polymorphic virus detection, is considered deprecated. Polymorphism is therefore a problem for the antivirus companies.

#### **Preliminary Notation**

The terms *metamorphic* and polymorphic computer viruses are often used promiscuously. Meta is Latin and translates to "change". Metamorphism is used to describe viruses *changing* themselves, instead of producing new forms. The two terms and their differences when used to describe computer viruses, are explained in section 2.4.5 on page 36. Until then, the term polymorphism is used to describe both types.

The initial case study done in the thesis was focused on a computer virus and the term computer virus has been used since. Where the correct term would perhaps be malware, the term computer virus or virus is therefore used. Only when the context require separate identification, the different terms are used.

## 1.1 Motivation

Virus writers have commonly been thought of as "computer nerds" seeking to increase their reputation in underground subcultures by writing viruses. From article "The Generic Virus Writer" [25] written in 1994, the motivation for writing viruses between the studied groups of virus writers varied. Writing viruses for economical benefits is not stated as a motivation. From "Hackers/Crackers" [51] written in 2006, the motivation for writing malicious programs or *malware* has changed. The quote is translated from Norwegian.

The annual report of SIS (Senter for Informasjonssikring) describes the current threat picture. The report shows that there is an increased development in the use of security holes to gain profits. It is not the "computer nerds" which are responsible for malware production anymore; organized crime is behind and large amounts of money is involved.

Mikko Hypponen of antivirus company F-Secure stated the following in 2006 [22].

The most significant change has been the evolution of virus writing hobbyists into criminally operated gangs bent on financial gain.

Symantec confirms this trend in [37]. Fortinet writes extensively about how the virus business is organised using mafia-like terms: the members are divided into *coders*, *kids*, *mobs and drops* [26]. Each group has dedicated tasks in the virus production cycle and there are large sums of money involved. Valerie McNiven, US Treasury advisor on cybercrime stated the following in 2005 [26].

Last year was the first year that proceeds from cybercrime were greater than proceeds from the sales of illegal drugs, and that was, I believe, over \$105 billion.

The concept of virus-writing has evolved from vandalism to organised crime. Following from this evolution, the amount of new complex viruses written are higher every year. Spinellis has devised a proof stating that general detection of evolving, bounded length viruses is NP-complete [34]. This is not necessarily true when a detection algorithm is allowed to produce *false positives*. False positives are clean files erroneously reported as containing a virus. Many articles on detection of both known and unknown polymorphic viruses are written and because of the increased cybercrime, there is an increased interest in the field. However, no unified method of detecting polymorphic viruses has been elected, and the different methods have their strengths and weaknesses.

## **1.2 Problem Statement**

In October 2006, I contacted the Norwegian antivirus company Norman ASA with an enquiry about writing a master thesis on the subject of computer viruses. The selected field of interest was "Detection of polymorphic viruses". Because this is a rather broad field, two research goals were defined to aid the process of determining a final problem statement.

- 1. Learn about polymorphic viruses through a case study.

- 2. Examine if there is possible to infer any knowledge from the case study which could be used in general detection of polymorphic viruses.

The first research goal had the following implications. To analyse the case study, the PE file format, the x86 assembly language and diverse reverse engineering tools had to be mastered. The virus selected for the case study were *Zmist*, written in 2001. Because detecting Zmist would give a better foundation for the second research goal, the first goal were extended to include detection of Zmist.

After 8 months, the first research goal were reached and the focus was placed on the second research goal. When analysing Zmist, most of the time were spent *comparing* the different forms. The comparison foundation acquired lead to a working detection algorithm and conforming to the second goal, the following question was posed: "Is it possible to automatise or semi-automatise this comparison process?"

The first step in such an automatised comparison, would be to remove the detectable elements that are <u>not</u> common patterns in the different forms of a polymorphic virus. Junk instructions are an example of such detectable elements, and it was decided that junk instructions should be removed as the first step in the process of creating a automatised comparison program.

#### **Problem Statement**

As a result of the research conducted related to the second goal, the following problem statement was formulated.

Is it possible to separate junk instructions from non-junk instructions in an executable file?

The contents of this thesis are therefore a product of the studies made, and the tools and techniques developed, to be able to produce an answer to the problem statement.

## **1.3** Thesis outline

The thesis is comprised of the following chapters.

- Chapter 1 (Introduction) is an introduction to the thesis, describing the motivation, research goals and problem statement.

- Chapter 2 (Background) contains background information necessary to know when analysing viruses. Further, computer virus history, polymorphic viruses and detection methods are explained in this chapter.

- Chapter 3 (Case Study) provides the results of the first research goal. In this chapter Zmist is discussed and analysed, and two detection attempts are described. Most of the Zmist analysis and both the detection attempts are results of my own findings. A disassembler termed *Gdasm* was specifically developed to aid the research conducted in this thesis and Gdasm is presented in this chapter.

- Chapter 4 (Analysis and Lessons Learnt) describes the analysis and outcome related to the second research goal.

- Chapter 5 (The JID Framework) contains the discussion and design of a junk instruction detection framework. This chapter tries to answer the problem statement and the results developed in this chapter are of my own findings.

- Chapter 6 (Testing) describes the different tests conducted and the results. The tests are related to the Zmist detection algorithm developed in chapter 3 and the JID framework developed in chapter 5.

- Chapter 7 (Conclusion and Future Work) contains a summary of the thesis, the contributions made and suggestions for future work.

## Chapter 2

## Background

Most computer viruses today infects one or more of the Microsoft Windows operating systems. To investigate viruses, it is crucial to have a basic understanding of Windows' executable file format (PE). The PE files contains executable binary machine code, created to run on a CPU.

The 32-bit x86 architecture has been the most common processor architecture used for development world wide and most computer viruses are written for x86. It is therefore necessary to understand the x86 assembler language which is the programming language for the x86 CPU architecture.

The binary machine code found in the PE files must be reversed (disassembled) into meaningful x86 instructions when analysing viruses. It is therefore necessary to learn about common disassembling techniques. Finally, computer viruses and detection methods are described.

## 2.1 PE File format

PE is an acronym for *Portable Executable* and is described in the PE file format specification from Microsoft [19]. A PE file is an executable file for the Microsoft Windows family of operating systems. PE files often have the file extension *.EXE* and a more popular term is "EXE-files", short for executable files. Because binary viruses can exist inside PE files, it is necessary to have a thoroughly understanding of the PE file format.

## 2.1.1 PE File Structure and Headers

A PE file contains many types of headers and several fields inside each header. Figure 2.1 on the following page illustrates the PE layout and is reproduced from [19, page 6]. MS-DOS doesn't support the PE file format, but for backwards-compatibility the MS-DOS header is placed first in a PE file. This header contains *stub* code compatible

Figure 2.1: Figure illustrating the Microsoft PE Executable format

with MS-DOS, such that when the file is executed in MS-DOS the stub is executed. The stub typically displays "This program cannot be run in DOS mode" message, before exiting. Because valid MS-DOS executables start with the characters 'MZ', the MS-DOS header is often termed "MZ header".

When an OS executing the PE file supports the PE file format, the PE loader of the OS locates the PE header using the "Offset to PE header" field found at position 0x3c in the MZ header. It is within the PE header and the subsequent *sections* the code and data constituting the actual executable file is found. It it is therefore necessary to have a fundamental understanding of the PE header and the sections. The terms VA and RVA are used extensively in the PE file format and must be described prior to explaining the PE header and sections.

## VA and RVA

All the OSes capable of loading PE files also have support for virtual memory enabling each PE file to be loaded on the same address in memory. The address each PE file is loaded to is termed the *imagebase*, and is a field found in the PE header described next.

- **VA** A *VA* is a *virtual address*. VA is the imagebase + the offset of the item in question loaded in memory (for example an instruction). The VA completely describes the location of one item in memory.

- **RVA** An *RVA* is a *relative virtual address*. This is the VA the imagebase, in short terms the offset of the item in question loaded in memory.

#### **Important PE header Fields**

There are a total of 53 header fields in the PE header. The following list enumerates the fields necessary to recognise in the thesis.

- **Characteristics** Information about the attributes of the file. Examples are "the file is executable", "relocation information has been removed from the file" and "the file is a system file, not a user program".

- AddressofEntrypoint When the OS executes a PE file, it needs to know where the code should begin its execution. The instruction at the *entry point* address is the first instruction executed by the CPU when the PE file is run. Usually the entry point is within the code section. The entry point address is stored in the PE header as an RVA.

- **Imagebase** The *imagebase* is the memory address of where the first byte of the executable image is loaded. Default imagebase for Windows 95/98/Me/NT/2000/XP is 0x400000.

### 2.1.2 Sections

A *section* is described in Microsoft's PE specification as the "*basic unit of code or data within a PE file*". Each section have a *section header*, and the header contains 10 fields. The 5 most characteristic fields are listed here.

- **Name** The name of the section. The names themselves do not identify the sections and different compilers can produce different names. For instance, Borland uses the name "CODE" while GCC use the name ".text" to describe the executable section. The sections are identified by the characteristics.

- **Raw size** The size of the section in the PE file.

- Virtual size The size of the section when loaded in memory.

- **Pointer to raw data** Pointer to the raw data in file (where does the section begin in the file).

- **Characteristics** Information about the section. Examples are if it is executable, if it can be read from, if it can be written to, and more.

There can be many types of sections. Present in all PE files is a section containing executable code, often named .text. If the program has uninitialised data, this is often found in a section named .bss. Initialised data, such as global variables, are found in a section often named .data.

Having introduced a executable code section in a PE file, it will from now on be referred to as .text.

## 2.1.3 Relocation Section

Sometimes the OS cannot load the given PE file at the wanted imagebase. All memory addresses found in instructions in the PE file assumes the use of the default imagebase (0x400000). Unless the program is loaded at this default imagebase, the execution of the program would be erroneous. The relocation section, or relocation table, contains pointers to each instruction's RVA/VA. The pointers are called *fixups* and must be updated when executed at a non-default imagebase address. Each fixup points to the memory offset in the instruction, not the instruction itself. The PE loader can then loop through each fixup, adjusting the memory address to the new imagebase before the PE file is executed. The relocation section is often named .reloc.

## 2.1.4 Import Section

Practically all executable files uses one or more functions from shared libraries. The shared libraries on the Microsoft Windows platform often have the extension *DLL*. The *import section* contains references to the DLLs and the corresponding functions imported from each DLL. Only the functions used in the PE file are imported. The import section is split in two tables:

- 1. The *import table*. Each entry in this table contains the DLL reference (for instance kernel32.dll) and a pointer to the import lookup table.

- 2. The *import lookup table*. Each entry in this table contains a function reference within a given DLL (for instance the function GetModuleHandleA of kernel32.dll)

Since a PE file should execute on all systems it was compiled for (for instance Windows 2000 and Windows XP), the entries in the import lookup table cannot contain specific memory addresses for each imported function. This is because different OSes can load the DLL functions to different memory addresses. When a PE file is executed, the PE loader resolves the imported functions' memory addresses in the OS. Therefore, it doesn't matter if the function GetModuleHandleA resides in memory address 0x7C573DFC or 0xBFF77716. The PE loader resolves the correct memory address each time the PE file is run.

### 2.1.5 Summary

This chapter were started by pointing out that most binary viruses are written for the Microsoft Windows platform. The PE file format is used to structure the executable code designed to run on the Microsoft Windows platform and an introduction to the PE file format were therefore given in this section.

To understand how a virus works, it is necessary to master the language the executable code found in .text is expressed in. This is described in the next section.

## 2.2 x86 Assembler Language

All the information in this section is based on Intel's Architecture Manual Vol 1 [18], Vol 2 A-M [16] and Vol 2 N-Z [17].

The 32-bit Intel processor architecture, commonly known as "x86", has been the most common processor architecture used for software development worldwide. Because of the popularity of the x86 architecture, most viruses are written for x86. To be able to read virus code, the x86 assembler language must be mastered.

Assembler language is the low-level symbolic representation of the binary machine codes understandable by a CPU. It is more or less a one to one mapping between the machine codes and a symbolic representation. Because the machine codes are highly processor-dependent, a program written in assembler language is not portable between different processor architectures. The process of converting assembler language source code into binary machine code is called *assembling*. The process of reversing a block of binary machine code into assembler language representation is called *disassembling*. In most cases the virus source code is not available to a virus analyst. A disassembling of the binary file infected with the virus is therefore the best method of transforming the virus into human understandable operations.

### 2.2.1 Intel Syntax and Examples

This section describes the assembler language dialect used in this thesis. Further, this section gives two examples of assembler language code. These are provided as a motivation for further reading, and to illustrate the main features of the dialect used.

In this thesis, all assembler language listings use the dialect termed *Intel syntax*. A typical instruction in the Intel syntax has the following form:

instruction destination, source. Another common dialect is the *AT/T syntax*. This is not used or discussed any further in this thesis.

| # | Instruction |      |     |

|---|-------------|------|-----|

| 1 | mov         | EAX, | 2   |

| 2 | mov         | EBX, | 3   |

| 3 | add         | EAX, | EBX |

Table 2.1: x86 Assembler Language Example 1

| # | Instruction                    |  |

|---|--------------------------------|--|

| 1 | mov EAX,[input1]               |  |

| 2 | add EAX, [input2]              |  |

| 3 | <pre>mov [output+4], EAX</pre> |  |

Table 2.2: x86 Assembler Language Example 2

Table 2.1 contains an example of Intel syntax assembler code. In instruction 1, the value 2 is copied into the register EAX. A register can be viewed as a temporary storage unit. In instruction 2, the value 3 is copied into the register EBX. In the third instruction, the value contained in EBX is added to the value in EAX. After instruction 3 has executed on the processor, EAX holds the value 5 and EBX the value 3.

Table 2.2 contains another example of Intel syntax assembler code. In instruction 1, the value found at memory address input1 is copied into EAX. In instruction 2, the value found at memory address input2 is added to EAX. Finally in instruction 3, the value in EAX is stored at memory address output+4. The square bracket: [ptr] found in x86 assembler language is equivalent to pointers in C: \* (ptr).

## 2.2.2 Instruction Format

An instruction consist of possible 6 parts: Prefix byte, Opcode bytes, ModR/M byte, SIB byte, Displacement bytes and Immediate bytes. The disassembler converts the six parts into a symbolic representation. To understand the material presented in this thesis it is not necessary to have a complete understanding of the different parts. When an instruction is represented symbolically, the instruction has the following format: mnemonic operand1, operand2, operand3.

A mnemonic is a reserved name for a class of instruction opcodes which have the same function. For instance the opcode mnemonic MOV has several different opcode byte encodings depending on what should be moved where, but the function is identical. From the symbolical representation, there can be from zero to three explicit *operands*. The instruction act on the operands, and operands can be viewed as arguments to the instruction. In addition to the explicit operands, there can also be several implicit operands. The instruction push EAX pushes the content of the register EAX onto the stack. EAX is an explicit operand and the stack pointer register esp is an implicit

#### 2.2. X86 ASSEMBLER LANGUAGE

operand. Each operand in an instruction is a source, a destination or both. A source operand can be any of the following listed here.

- an immediate operand or value encoded in the instruction itself

- a register

- a memory location

- an IO port (direct communication with hardware through a hardwired input/output port)

A destination operand can be any of the following listed here.

- a register

- a memory location

- an IO port

Immediate operands are values given as an operand to the instruction. In the instruction sub EAX, 13, the value 13 is an example of an immediate operand.

## 2.2.3 About the Basic Execution Environment

A *basic execution environment* is the resources available for executing instructions found in application- and OS-code. The components of the basic execution environment provides the foundation for executing instructions on a processor and they are listed here.

- Address space The *address space* is the amount of memory the processor can address. There are possible  $2^{32}$  addressable memory bytes in the x86 32-bit architecture.

- **Basic program execution registers** Registers are the basic storage units in a processor. There are eight general-purpose registers, one control flag register and one program counter register.

- **x87 FPU registers** The floating point unit (FPU) registers are used to do floating point operations.

- **MMX registers** The multimedia extension (MMX) registers exist to perform "singleinstruction multiple-data" (SIMD) instructions on 64-bit data and are often used in multimedia applications.

- **XMM registers** The XMM (extension to MMX) registers are similar to the MMX registers, but are used on 128-bit data.

The registers constituting the *basic program execution registers* are used in all executable files and are explained on the next pages.

Figure 2.2: Substitute the question mark (?) with A,B,C or D.

#### **The General Purpose Registers**

The general-purpose registers are provided for storing pointers and results from general operations. The general-purpose registers are the 32-bit registers: EAX, EBX, ECX, EDX, ESI, EDI, EB and ESP. Each of the 32-bit registers 16 least significant bits (lsb), can be addressed by the corresponding 16-bit registers: AX, BX, CX, DX, SI, DI, BP and SP. The 8 most significant bits (msb) of AX, BX, CX and DX, can be separately addressed by the following corresponding 8-bit registers: AH, BH, CH and DH. Also, the 8 lsb of the same 16-bit registers can be addressed by the following corresponding 8-bit registers: AL, BL, CL and DL. Figure 2.2 illustrates the addressing possibilities of EAX, EBX, ECX and EDX.

The Intel manual describes the following uses for each register [18].

- EAX Accumulator for operands and results data.

- EBX Pointer to data.

- ECX Counter for string and loop operations.

- EDX I/O pointer.

- ESI Source pointer for string operations.

- EDI Destination pointer for string operations.

- **ESP** Stack pointer. This register contains the location in memory where the last element pushed onto the stack is found.

Note that this is the *intended* usage of each register. Each register can be used freely by the programmer in any type of operation.

#### 2.2. X86 ASSEMBLER LANGUAGE

#### **EFLAGS** register

The EFLAGS register contains several *flags*. Each flag is of size 1 bit, and has a fixed position in the EFLAGS register. A flag can be *set*, meaning that it receives the value 1, or *cleared*, meaning that it receives the value 0. Amongst all the flags found in the EFLAGS register, there are seven flags used in regular applications. The flags are listed here.

- **Carry Flag** The CF flag is set/cleared depending on different results in arithmetic instructions.

- Parity Flag The PF flag is set/cleared depending on parity of result.

- Adjust Flag The AF flag is set/cleared depending on binary-coded decimal arithmetic.

- Zero Flag The ZF flag is set if result is zero, cleared if not.

- Sign Flag The SF flag is set if sign of an integer result is negative, cleared if positive.

**Overflow Flag** The OF flag is set if integer result overflowed, cleared if not.

**Direction Flag** The DF flag is used in string operations to tell if loop should process memory addresses in low-high (cleared) or high-low (set) order.

#### **EIP** register

The EIP register contains a memory pointer to the next instruction to be fetched and executed by the processor. EIP cannot be addressed explicitly, but is manipulated implicit through the following *control transfer instructions*: JMP, CALL, RET, IRET and the group of conditional jumps. Conditional jumps, or short *Jccs*, are a collective term for the different opcodes which transfers the execution flow to the target given in the Jcc instruction when certain conditions are met. Examples are JZ (jump if zero flag is equal to 1), JECXZ (jump if ECX is equal to 0), JNO (jump if overflow flag is equal to 0). There are two possible outcomes when a Jcc is executed: The flow of execution is set to the *fall through branch* (jump not taken) or the *taken branch* (jump taken).

### **2.2.4** Instruction groups

There are a vast number of different instructions, but when grouped the number becomes manageable. The Intel manual [18] unify the instructions in 13 different groups. The following list describes each group.

Data transfer Move data between operands.

**Binary arithmetic** Basic binary integer computations on operands.

- Decimal arithmetic Decimal adjusting.

- Logical AND, OR, NOT, XOR operations on operands.

- Shift and rotate Shift and rotate bits in operands.

- **Bit and byte** Bit instructions test and modify individual bits in operands. Byte instructions set the value of a byte operand, based on flag status in the EFLAGS register.

- **Control transfer** Provide jump, conditional jump, call and return to control the program flow.

- String Move strings of bytes to and from memory.

- I/O Move data between the processor's I/O ports and operands.

- Enter and leave High level procedure entry and exit.

- Flag control Instructions operating on the EFLAGS register.

- Segment register Instructions loading pointers into segment registers.

- **Miscellaneous** Instructions which cannot be placed in the other groups, such as NOP (no operation) and CPUID (identify processor).

- Each group contains mnemonics performing various tasks, related to their grouping.

### 2.2.5 Summary

This section described the layout of the x86 processor architecture, and gave an introduction to the x86 assembler language. Mastering the x86 assembler language is essential when analysing viruses, because most viruses are written for the x86 architecture.

As previously described, the .text section contains the executable code of a program. Converting the bytes in the .text section into instructions is done by the disassembler, but the *sequence* the disassembler should process the bytes in, is not necessarily evident. The next section describes the two most common disassembler algorithms: linear sweep and recursive traversal.

## 2.3 Disassembling Algorithms

The process of converting a sequence of bytes into meaningful instructions is called disassembling. A *disassembling algorithm* describes the sequence the bytes should appear in, when given as input to the disassembler. There are two well-established disassembling algorithms: Linear sweep and recursive traversal [33].

#### 2.3.1 Linear sweep

Linear sweep (LS) disassembles the byte stream sequentially. LS typically starts at the beginning of the code section and proceeds to the end. LS runs in O(n). The following pseudocode illustrates LS.

Algorithm 2.3.1: DISASSEMBLE(Addr)

while Addr is a valid section address do  $\begin{cases} i=DecodeInstr(Addr) \\ output(i) \end{cases}$

#### Advantages

Compared to recursive traversal, LS's main advantage is simplicity. There is no need to parse the instruction disassembled, and there is no need for an input buffer to store the instructions. Another advantage is that <u>all</u> code within an executable code section is disassembled, because all the bytes in the code section is processed by the disassembler.

#### Disadvantages

LS doesn't provide any logical structure in the instruction output. This is a drawback when an analysis method requires the disassembled instructions to appear in the same order as when executed on a CPU.

Misinterpretation is another disadvantage. If code and data are mixed together in a section, misinterpretation is likely to occur: All the bytes used for data stored in an executable code section, is misinterpreted as code. Without utilising any information about the placement of data and code, it is only possible to detect misinterpretation when an invalid opcode byte sequence, termed *bad instructions*, is encountered. As seen in the Intel instruction manuals, the x86 architecture has many byte patterns decoding into valid instructions and few byte sequences yield bad instructions.

#### 2.3.2 Recursive traversal

Recursive traversal (RT) follows the designated flow of the program. RT starts the disassembling at a program's entry point, and follows the flow from there. If a control transfer instruction is encountered, the transfer is followed if possible. RT runs in O(n).

#### Algorithm

The basic algorithm for recursive traversal given in [33] is reproduced here.

| # | Instruction  |           |  |

|---|--------------|-----------|--|

| 1 | mov EAX,     | 0x4000320 |  |

| 2 | add EAX,     | 0x10      |  |

| 3 | xor EAX,     | 0x14      |  |

| 4 | call [EAX+6] |           |  |

Table 2.3: Example illustrating an instruction containing an unresolvable control flow

#### Algorithm 2.3.2: DISASSEMBLE(Addr, instrList)

```

if (Addr.visited)

then return

do

do

do

finstr = DecodeInstr(Addr)

Addr.visited = true

add instr to instrList

output(instr)

if (instr is a branch or function call)

then

for each possible target t of instr

do Disassemble(t, instrList)

else Addr += instr.length

```

while Addr is a valid instruction address;

#### Advantages

RT's main advantage is correct disassembling of a code section with both code and data mixed together. Also, the decoded instructions appear in the same order as when the instructions are executed on a CPU.

#### Disadvantages

The disadvantage of RT is when control transfers cannot be resolved. The x86 assembler language contains many addressing forms, and some are only resolvable when executing the instructions. Table 2.3 illustrates the concept of *unresolvable control flow* instructions. The instruction sequence illustrated is a valid x86 instruction sequence. Unless the sequence is emulated or executed on a CPU, it is not possible to determine the value of EAX in instruction 4. Instruction 4 is therefore an instruction containing an unresolvable control flow. Because the destination of the control transfer instruction cannot be resolved, the RT algorithm cannot disassemble the byte stream found at the destination. Schwarz et al. lists the two possible consequences when this situation occurs. *failure to disassemble some reachable code* (if control transfer instruction is not followed) or *erroneous disassembling of data* (if some algorithm makes an erroneous guess of the jump destination).

### 2.3.3 Summary

In this section, the two most common disassembling algorithms have been explained and their advantages and disadvantages have been discussed. The tools needed to understand polymorphic viruses have now been acquired, and the following section is devoted to computer viruses.

## 2.4 Computer Viruses

This section is about computer viruses. The layout is structured as follows. First, terms used in this and subsequent sections are defined. Second, a brief history illustrating the evolution of both virus technology and the motivation for writing the viruses is given. Finally, polymorphic viruses are introduced and techniques for achieving polymorphism are discussed.

## 2.4.1 Definitions

Peter Szor defines a computer virus in his book "The Art of Computer Virus Research and Defence" as follows [38].

A computer virus is a program that recursively and explicitly copies a possibly evolved version of itself.

The definition disagrees with the common belief that a program needs to do unwanted, explicit damage to be termed a virus. The definition contains <u>all</u> programs intentionally spreading themselves without any acknowledgement from the user.

There are many different types of malware. Aycock lists several types in his book "Computer Viruses and Malware" [13]. Amongst the types listed are: Viruses, worms, trojans, backdoors. Viruses and worms are two types of malware often confused with each other, and the two types are explained here.

#### **Computer viruses**

Computer viruses, or viruses, hide inside hosts the same way biological viruses hide inside cells. To replicate, viruses need new hosts. Viruses infect files on the host machine, and they spread when users exchange files, for instance through USB-pens or a shared directory in a P2P application. Note that mapped network drives, for instance an NFS mount or a mapped UNC path in Windows, might provide the virus an entrance through the network. Harley et al list in "Viruses Revealed" [24] three parts a computer virus consists of.

1. Infection mechanism - How the virus spreads.

- 2. Trigger If the virus is to deliver the payload or not.

- 3. Payload What the virus does except from spreading. Payloads can be intentional or accidental (bugs in virus code, damaged in network transport, etc).

#### **Computer worms**

Computer worms, or worms, are often confused with viruses. Worms are similar to viruses except for two main differences. The differences are listed here.

- 1. A worm is <u>not</u> parasitic, i.e. it doesn't require a host to infect a new target. It is a *stand-alone application* performing self-replication. This is often done by exploiting buffer overflows in different Internet applications.

- 2. Worms spread to new hosts through the network via different network protocols (for instance the TCP/IP protocol).

As stated in the introduction to chapter 1, the term "virus" is used for describing computer viruses, trojans, worms and other types of malware in the thesis. The specific terms are only used when the context requires separate identification of the terms.

## 2.4.2 History

The term "computer virus" as it is used today, is attributed Len Eidelmen who defined the term in 1983 [48]. However, as early as in 1949, John Von Neumann devised a theory of a program capable of replicating itself as long as a computer can hold information in "memory" [31].

The first acknowledged computer virus appearing on regular users computers (often termed "in the wild"), was "Elk Cloner" [44]. Elk Cloner was written for the Apple II computer and displayed a poem on every 50th boot. In 1986, "(c) Brain" appeared. Brain is considered the first virus compatible with the IBM PC. It was written by two brothers from Pakistan, and it spread over the whole world [42].

Later, more malicious viruses appeared. "CIH" also known as "Chernobyl" was one of the most direct damage-dealing viruses known [43]. The first version was seen in the wild in 1998. CIH fills the first megabyte of the hard drive with zeroes, and it also tries to write to Flash BIOS. If the latter is successful, the Flash BIOS needs to be replaced/rewritten for the computer to work.

Isolated, most other viruses do not cause an equal amount of damage to the computer as the CIH virus did. However, they can cause more damage world-wide because of their ability to spread. The damage can be anything. For instance, the amount of spam is something regarded as damage because spam contributes to slowing the Internet down. In 1999 the "Melissa" worm caused a damage estimated to \$80 million dollars. In 2001, the "Code Red" worm caused a damage estimated to \$2 billion dollars [31]. In

#### 2.4. COMPUTER VIRUSES

Figure 2.3: Blackmailing scheme

2003, the estimated amount reaches an even higher level. A UK-based digital risk firm called "mi2g" estimates the worm MyDoom to have caused a damage equal to \$38.5 billion dollars. However, the correctness of this estimate and others are discussed by Vmyths, "a site dedicated to erase the computer virus hysteria" [11].

#### **Change of Motivation**

Regarding viruses, the situation of today has changed. There has been a massive explosion in the number of viruses created and released in the wild. The reason for this increase lies in the change the Internet has undergone for the last decade. The Internet has changed from being an information provider, to the world's biggest marketplace. As mentioned in the introduction, the virus business is organised in mafia-like structures. The reason for organised crime to enter the virus scene is simple: money. The scheme in figure 2.3 illustrates another reason to why the mafia-analogy has been introduced. Assume a "mafia" has control over a vast number of infected computers, termed a botnet (net of robots). First, a virus is written to gather bots to the botnet. When enough bots are under the mafia's control, the owners of the site making legitimate money are contacted by the mafia. The mafia threaten them to pay protection money. If they do not comply, a distributed denial of service (DDOS) attack is launched on the site. The reason for launching a DDOS attack on the site, is that paying customers and others will in the worst case be unable to use the site at all, because it is too busy serving the bots requests. If the DDOS attack lasts for days, the paying customers grow tired of not being able to use the service they are paying for, and head over to other sites providing similar services instead. The number of infected computers vary between the researchers estimating the sizes of botnets [40]. Some researchers estimate the size to be at maximum a few thousand bots, while others estimate a botnet to reach 350000 bots. It is however clear that botnets exist, and are used in organised crime.

The scheme illustrated in the figure is only one of many money-making schemes requiring viruses to be installed on computers. *Spamming* and *phishing* are other techniques used to make money. For instance, the *Bagle* worm opens TCP port 6777, providing remote access to the infected computer [21]. This can be used to install various programs on the infected computer and harvest sensitive information such as VISA card numbers. Another "interesting" extortion scheme is *ransomware* [45]. When the virus is executed, it encrypts files present on the computer, such as DOC and JPG files. The user receives a message stating that in exchange for money, the user will receive a decryption tool which recovers the previously encrypted files. "Gpcode" is an example of such a virus [41].

All the organised crime business models require viruses infecting computers without being detected. The virus writers are therefore constantly developing techniques for avoiding detection. One of the major techniques for making a virus "undetectable" is code changing.

#### **Code Changing viruses**

The first polymorphic virus appeared in 1990, and was called "1260" [12]. It was created by Mark Washburn as a research virus to demonstrate for the antivirus companies that string-based pattern scanners fail, when such viruses are encountered. Each infected file increases with 1260 bytes (hence the name). The payload is encrypted with two sliding keys different in each infection. The decryptor contains do-nothing instructions inserted between the real decryptor instructions. The virus was never released in the wild.

The "Marburg" and "HPS" viruses were the first to use 32-bit polymorphic engines [23]. "Appariton" was the first metamorphic virus (See section 2.4.5 on page 36 for definition). In 2001, Simile and Zmist made their entrance. These are two of the most complex poly- and metamorphic viruses known. The metamorphic engine of Simile contains over 12000 lines of Intel x86 assembly code[13]. Zmist is chosen as the case study in this thesis and chapter 3 on page 47 contains a thorough analysis of Zmist.

#### Server-side Polymorphism

Today, the amount of new file-infecting viruses is low compared to other types of malware such as worms and trojans. The polymorphic techniques established in the file-infecting polymorphic viruses are however still valid. Commtouch's "Malware outbreak trends" for the first quarter of 2007 [15] reports of an increase in "server-side polymorphic malware". This type of malware is created by a metamorphic engine residing on one or more servers. When enough worms have been created, they are launched simultaneously on the Internet. The following quote is taken from Comm-

touch's report.

Rapid simultaneous release of massive amounts of distinct variants allows each variant to do maximum damage before a suitable signature or heuristic can provide protection.

The type of attack described in the quote is known as a "zero-hour" attack, because of the rapid spread before it is detected by antivirus software. Because the worms are pre-mutated, there is no need for mutation engines present in the worm-files. When the mutation engine is not present, the virus analysts cannot reliably analyse the algorithm which produced the mutated worms. The virus analyst can only acquire samples and construct a detection algorithm based on the samples. The "Storm Worm" is an example of malware effectively utilising server-side polymorphism. Between 18th January 2007 and 31th January 2007, there were observed at average 3824 distinct variants of the Storm Worm per day. On 28th January the maximum of 7893 distinct variants were observed [14]. The payload of the Storm Worm is to generate bots that can be used to send spam emails and participate in botnets.

Having illustrated the use of polymorphism, polymorphic viruses and techniques for achieving polymorphism will be described. Polymorphic viruses are built upon mechanisms developed in *encrypted viruses* and this type is therefore described prior to polymorphic viruses.

## 2.4.3 Encrypted Viruses

A host with an *encrypted virus* infection contains two parts: a *decryptor* and an encrypted *engine* [13]. When the host is executed, the decryptor receives control in some fashion, decrypts the encrypted engine and runs it. The decrypted engine is responsible for delivering the payload and infecting new hosts. Because the encryption key vary for each new infection, a static signature cannot be used to detect the encrypted engine. Except for the key used, the decryptor is static in each infection, revealing itself for traditional *signature-based scanning*. Signature-based scanning will be explained in 2.5.1 on page 41.

#### About the Decryptor

The decryptor's main task is to decrypt an encrypted engine, transfer control to the engine and possibly control back to the host code after the engine has infected new hosts. It is typically implemented as a loop inside the host with a control transfer instruction to the engine after the loop. The size of the decryptor can range from under ten to theoretically an infinitely number of instructions.

## About the Engine

The engine is the main part of the virus. The engine is responsible for finding new hosts, encrypt itself, create a decryptor which successfully manage to decrypt the engine, and inserts the engine and decryptor into the hosts.

## 2.4.4 Polymorphic Viruses

A *polymorphic* virus contains the same two parts as an encrypted virus: a decryptor and an encrypted engine [13]. The difference between a regular encrypted virus and a polymorphic virus lies in the decryptor: The decryptor of a polymorphic virus is syntactically different for each infection. The engine is capable of constructing a seemingly unlimited amount of different decryptor versions. The decrypted engine is the same each time, i.e. the length and syntax of the engine code is constant in each infection. Because of the "unlimited" amount of decryptors, the traditional signature-based scanning cannot be used since that would require an "unlimited" amount of signatures.

Webster & Malcolm uses the term *allomorphic* in [27]. An *allomorph* is any two generations of the same code-changing virus that differ syntactically. Two allomorphic code segments are semantically equal, but not syntactically equal. Polymorphic viruses have allomorphic decryptors. There are many ways of creating allomorphic code and section 2.4.7 on the facing page explains common methods for achieving polymorphism.

## 2.4.5 Metamorphic Viruses

*Metamorphic* viruses are code changing viruses similar to polymorphic viruses. The difference is that there is *no encryption* of the virus engine, and hence no decryptor. The engine itself avoids detection by changing each time it replicates. Two engines of the same metamorphic virus is therefore allomorphic

## About the Engine

The engine of a metamorphic virus is by Harleys definition similar to the polymorphic engine. The techniques needed to create new instances of itself, are the same as the techniques used in polymorphic viruses when creating new decryptors (see section 2.4.7 on the next page for a description of the most used methods). The difference is that the methods are applied on the whole engine, instead of constructing a new decryptor each time the virus infects a new host. This self-modifying code should be allomorphic for each time the virus infects, and a small coding error could cause an early death of the virus when the error evolves into new variants.

## 2.4.6 Notation usage for poly- and metamorphic viruses

Polymorphic and metamorphic viruses are similar considering detection methods. Both types change appearances for each new infection. It is therefore reasonable to continue using "polymorphic viruses" to describe both polymorphic and metamorphic viruses, unless the context requires separate identification of the two types.

## 2.4.7 Achieving Polymorphism

In this section, the most common techniques used to achieve polymorphism are explained. The essence in all the types listed, is to change the syntax and not the semantics, i.e. make allomorphic code segments. The techniques listed here, are a summary from techniques listed in Aycock [13].

**Instruction Equivalence** This technique is based on the fact that different sequences of instructions achieve the same. Consider the following code.

| # | Instruction Seq 1 | Instruction Seq 2 |

|---|-------------------|-------------------|

| 1 | mov EAX, 8        | sub EAX, EAX      |

| 2 | add [mem], EAX    | xor EAX, 4        |

| 3 |                   | add [mem], EAX    |

| 4 |                   | add [mem], EAX    |

Table 2.4: Instruction Equivalence

In sequence 1, the value 8 is added to the content of memory address mem. In sequence 2, the value 4 is added twice to the content of mem, achieving the same as sequence 1. The two code segments are therefore allomorphic.

**Instruction Reordering** If two or more instructions do not have any dependencies, their execution order do not impose on the overall program state. Consider the following code.

| # | <b>Instruction Seq 1</b> | Instruction Seq 2 |

|---|--------------------------|-------------------|

| 1 | mov EAX, 8               | mov EBX, 4        |

| 2 | mov EBX, 4               | mov EAX, 8        |

| 3 | add EAX,EBX              | add EAX, EBX      |

The instruction reordering must take into account the dependencies between the registers. For instance, the two sequences would not be allomorphic if the add instruction appeared before one of the mov instructions in only one of the sequences.

**Register Renaming** This technique changes the registers used in the instruction sequence. Consider the following code.

| # | <b>Instruction Seq 1</b> | Instruction Seq 2 |

|---|--------------------------|-------------------|

| 1 | mov EAX, 8               | mov EDX, 8        |

| 2 | mov EBX, 4               | mov ECX, 4        |

| 3 | add EAX,EBX              | add EDX, ECX      |

| Table 2.6: | Register | Renaming |

|------------|----------|----------|

|------------|----------|----------|

The two code sequences are allomorphic, but the instruction encoding is different because of the different registers used.

**Reordering Data** This technique changes the location of memory variables. Consider the following code.

| # | Instruction Seq 1   | Instruction Seq 2   |

|---|---------------------|---------------------|

| 1 | mov EAX, 8          | mov EAX, 8          |

| 2 | add [0x402008], EAX | add [0x403004], EAX |

Table 2.7: Reordering Data

The memory location is changed and the instruction encoding is different.

**Jump Islands** Jump islands are linked together with unconditional jumps (JMP). Consider the following example.

38

#### 2.4. COMPUTER VIRUSES

| # | Instruction Seq 1 | Instruction Seq 2 |

|---|-------------------|-------------------|

| 1 | mov EAX, 8        | mov EAX, 8        |

| 2 | mov EBX, 4        | jmp insn 3        |

| 3 | add EAX,EBX       | mov EBX, 4        |

| 4 |                   | jmp insn 5        |

| 5 |                   | add EAX, EBX      |

#### Table 2.8: Jump Islands

Because the instructions are scattered in sequence 2, the syntax is changed compared to sequence 1.

**Junk Code** Junk code is code inserted to obfuscate and confuse without altering the semantic of the program. The state of the original code is equal to the state from the original + junk code. Consider the following example.

| # | Instruction Seq 1 | Instruction Seq 2 |

|---|-------------------|-------------------|

| 1 | mov EAX, 8        | mov EAX, 8        |

| 2 | mov EBX, 4        | mov ECX, EAX      |

| 3 | add EAX,EBX       | mov EBX, 4        |

| 4 | mov ECX, 2        | xor ECX, EAX      |

| 5 |                   | add EAX, EBX      |

| 6 |                   | sub ECX, EBX      |

| 7 |                   | mov ECX, 2        |

In sequence 2, the ECX register is used for junk code. Note that in sequence 2, instructions 2,4 and 6 do not contribute to the output of the program. Sequence 1 and 2 are therefore allomorphic.

All the different techniques listed can be combined, increasing the level of polymorphism employed in a virus.

## 2.4.8 Summary

This section gave an introduction to computer viruses and their history from the beginning to the present situation. The main focus has been on polymorphic viruses and to describe the techniques for achieving polymorphism.

Polymorphic viruses are advanced and so are their detection methods. The next chapter is devoted to explaining the established detection methods.

Figure 2.4: Figure illustrating FP, FN, TP and TN

## 2.5 Computer Virus Detection

Aycock [13] divides antivirus detection techniques into two parts: static and dynamic methods. The static methods attempt to detect the presence of a virus without executing any code. Vice-versa, the dynamic methods execute the code and attempt to detect the presence of a virus by properties only present when executing the virus. Szor [38] separates antivirus detection into algorithmic methods (static), emulation methods (dynamic) and heuristic methods (both static and dynamic).

#### **Outcomes in Virus Detection**

Figure 2.4 (reproduced from Aycock [13, page 54]) illustrates the four possible results considering virus detection. The outcomes are independent of the method used for detection. In the figure, a perfect detection method would always return with results laying within the circle on the diagonal. The terms false positive, false negative, true positive and true negative are used to describe the different results.

The term *true positive* (TP) is used to describe a virus is present in a file which is detected. If a virus is absent in a file and the virus is not detected, the term is *true negatives* (TN). The term *false negatives* (FN) is used when a scanner reports a file as clean, but there is a virus present. To describe a file reported by a scanner as infected but the file is clean, the term *false positives* (FP) is used. All algorithms strive to reduce the number of false negatives and false positives, and to decrease the time spent verifying true negatives. If a file actually contains an infection (true positive), the time spent verifying the virus' presence is not critical to the user. It is the time spent on deciding whether a file is *clean* or not, that should be minimised. Unfortunately, there is a vast number of different viruses. Using elaborate detection methods on all files present on a computer, would result in unacceptable time delays. The use of filtering techniques such as *geometric properties* (GP), is a common method for sorting which viruses the antivirus product should scan for. The following paragraph describes GP.

#### 2.5. COMPUTER VIRUS DETECTION

GP can also be used as a static heuristic, reporting whether a file is "suspicious" and would require a more complex scan (often termed *deep scan*).

## **Geometric Properties**

Geometric properties are the alterations a virus does to the file structure. Szor lists common geometric properties found in viruses in [38]. Execution of code starting in the last section in the PE file is an example of a geometric property. This would imply that a virus has prefixed its code to the PE file. This is detected by following the entry point in the PE header and examine if it points to an address found in the last section defined in the PE header. Another common geometric property is the use of not-normal names for code section. For instance, it is suspicious that a section named .reloc has the EXECUTABLE characteristic set. Values considered not-normal in the PE header is another geometric property used to indicate the presence of a virus. For instance, there is a "checksum" PE header field containing a checksum of the PE file. If this checksum is not correct (i.e. the virus doesn't update this checksum), this can be used to classify a file as suspicious.

## Layout

It exists far to many detection approaches to describe all in this section. Selected detection methods from the different categories are provided instead, to illustrate the level of complexity and diversity employed by the different methods. The material is presented using Szor's categorisation. First, three algorithmic approaches are described. Then, detection using emulation is described. Last, one example of a static heuristic method and one example of a dynamic heuristic method are described.

## 2.5.1 Algorithmic Approaches

The Merriam-Webster's online dictionary [30] defines an algorithm as *a step-by-step procedure for solving a problem or accomplishing some end especially by a computer.* An algorithmic antivirus approach searches especially for a known virus with some knowledge of the virus' properties. How the search is conducted and what the properties of the virus are, are different with each algorithmic approach.

## Traditional antivirus methods

The established method for detecting viruses in the past has been *signature based scanning*[13]. The scan itself has been employed *on-demand*. A *signature* consist of the sequence of bytes necessary to identify a virus. As the viruses became more complex, the signature based scanning was not suited to detect the most advanced viruses. Signatures with *wildcard* support and *on-access* scanners (scanning on the fly) was

mov [edi], IMM → push ECX mov ECX, IMM mov [edi], ECX pop ECX

Figure 2.5: Example of term rewriting

developed to battle the new viruses. When polymorphic viruses started to appear, the antivirus companies were forced to find new techniques instead of upgrading the old ones. However, traditional signatures are still used and needed, for instance in emulation-based detection.

From now on in this thesis, the term *signature* is not necessarily related to bytescanning, but to something that defines a virus' property relative to the method. An example is the reduced engine-signature together with the language normalising detection method. This detection method is described after the part about X-raying.

## **X-raying**