**UNIVERSITY OF OSLO Department of Informatics**

Evaluation of Rectifiers & Voltage References for a Wireless Medical Implant

Master thesis

Svein Berg

**May 2008**

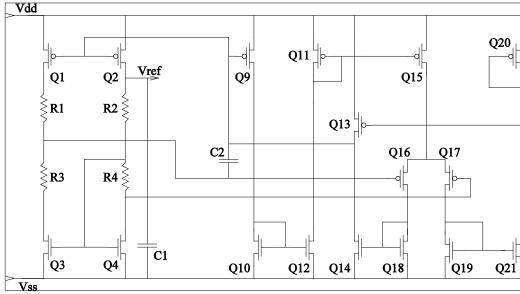

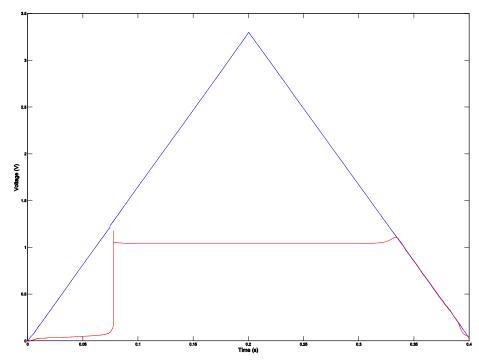

# **Abstract**

In the continuing hunt for better and more powerful monitoring and control, we see an increased interest for small and light electronic devices adapted for these tasks. This is seen both in tracking of goods, machinery, production and other parts of the industry as well as inside the human body. And every day, new areas of use are showing up. Following the IT-age is the enormous amount of information available. Common and revolutionizing for the devices now developed are their ability to deliver the exact information needed from an exact location.

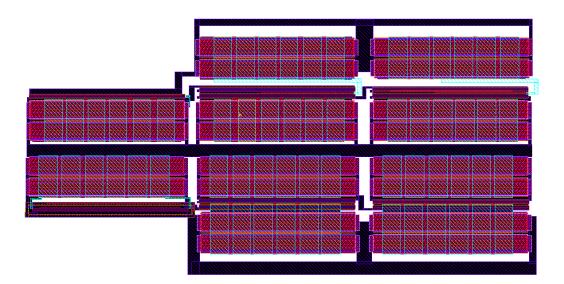

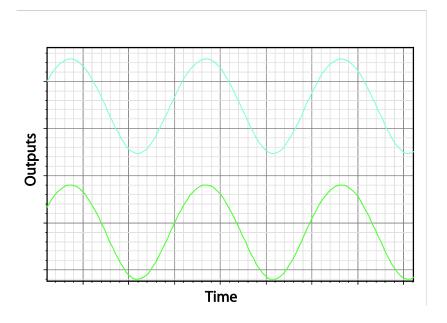

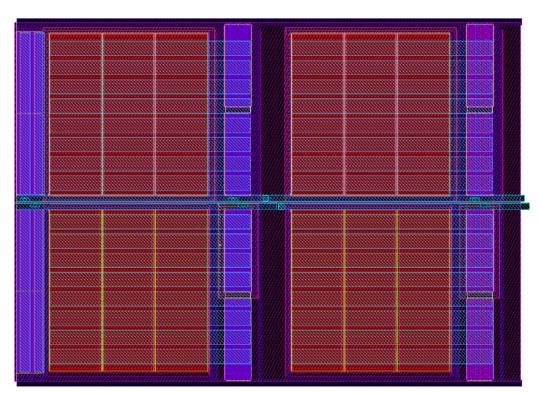

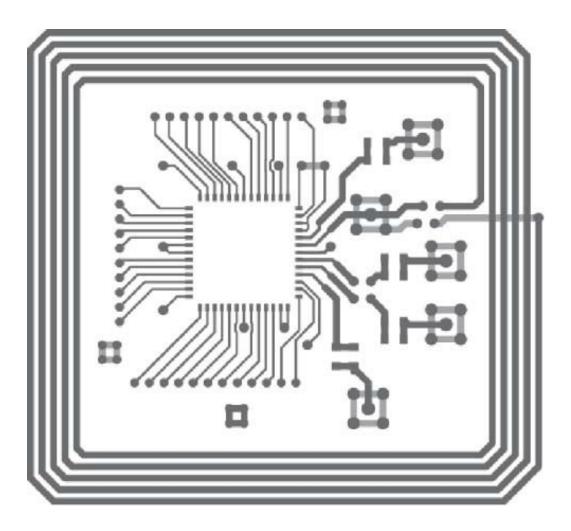

This master thesis discusses the different areas regarding development of a passive (without battery or any device of internal power source) medical implant from an electronic point of view. The introduction shortly presents the medical aspects of the diabetes disease and the reasons for this thesis. An overview of the wireless power transfer used in an inductive link application is given for understanding the physical aspects, environment and demands present for passive implants. This leads to identification of two parts that are essential in any kind of such a passive device, unrelated to the specific task of the implant: A rectifier to recover a DC-voltage from the AC-input signal, and a regulator for providing a stable V<sub>DD</sub> to the whole implant and its circuitry. These two circuits are fully presented in the last chapters and some different circuit solutions are presented. These solutions are developed for optimal adaption to the inductive link and other important parameters regarding this area. The circuit solutions are presented and produced in the STM CMOS 90nm ASIC<sup>1</sup> process, and the simulated and measured results are investigated and compared.

\_

<sup>&</sup>lt;sup>1</sup> Application Specific Integrated Circuit

# Acknowledgements

First of all I wish to thank Philipp Häfliger as supervisor for my work. I would like to thank him for the inspiration, encourage, support and guidance and for always having time to answer any question that came to my mind. Also, I want to thank Tor Sverre Lande as co-supervisor and for all valuable input he has given me.

Thanks to Trygve K. Halvorsen, Håvard P. Alstad and Kristin H. Løkken for our teamwork and discussion during the development and other aspects. And not to forget, providing a good atmosphere during the years and the long days at IFI.

This thesis could not have been accomplished without the support from Håvard Kolle Riis and Hans K. Otnes Berge. I wish to thank them for invaluable help with the production of ASIC chip and PCB, but also for their patient help with software support.

Also, a big thanks to everyone at the MES research lab including, but not limited to, Ole-Petter, Jenny, Henning, Øyvind, Olav, Bård, Dag, Kristian and Elias. Thanks for all the lunch breaks and the social environment.

# **Contents**

| 1 | Intro | oduction                                       | 1  |

|---|-------|------------------------------------------------|----|

|   | 1.1   | The main parts and focus of this thesis        | 2  |

|   | 1.2   | System solution guidelines                     | 3  |

| 2 | Diab  | etes and Monitoring Systems Today              | 7  |

|   | 2.1   | Short Description of Diabetes and its Treating | 7  |

|   | 2.2   | Glucose Monitoring Systems Available Today     | 10 |

|   | 2.3   | New Solutions under Development                | 14 |

|   | 2.4   | Sensor Technology                              | 15 |

| 3 | Syste | em Review and Energy transfer Theory           | 17 |

|   | 3.1   | System Review                                  | 17 |

|   | 3.2   | Inductance                                     | 19 |

|   | 3.3   | Mutual Inductance                              | 21 |

|   | 3.4   | The System                                     | 23 |

|   | 3.5   | Choice of Frequency                            | 30 |

|   | 3.6   | Considerations around coil design              | 32 |

| 4 | Rect  | ifier and Charge Pump                          | 35 |

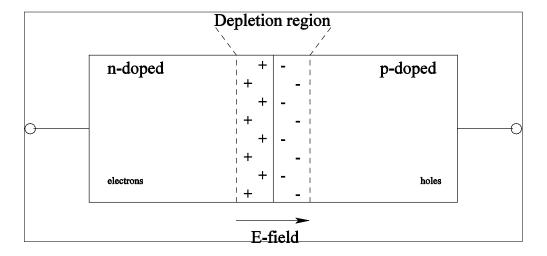

|   | 4.1   | pn-junction and diode                          | 35 |

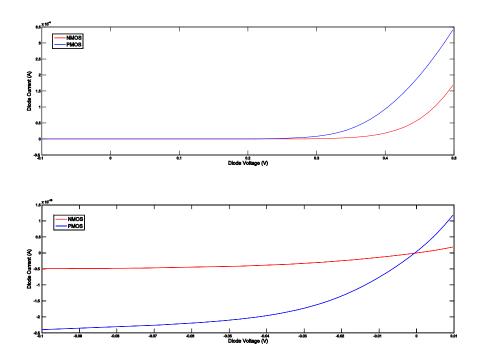

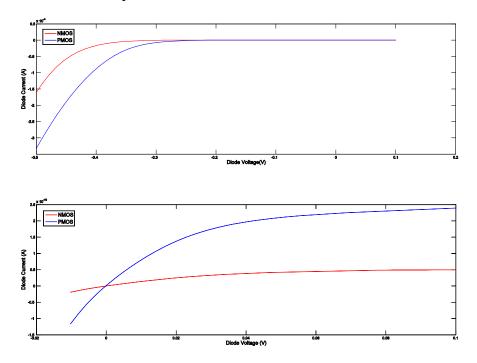

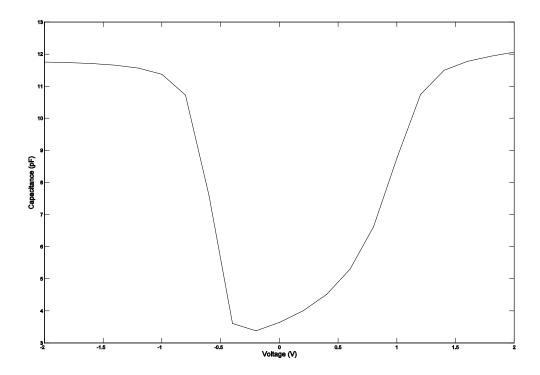

|   | 4.2   | Diode in CMOS                                  | 36 |

|   | 4.3   | Rectifying topologies and possibilities        | 41 |

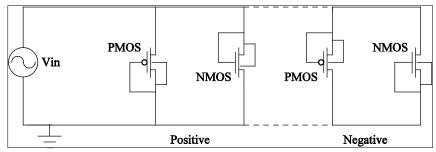

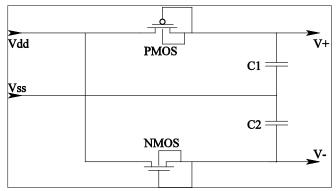

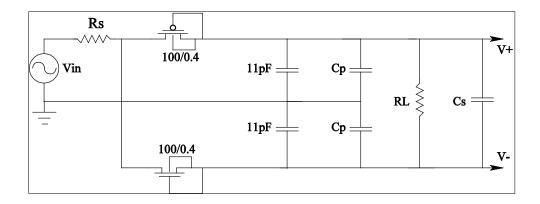

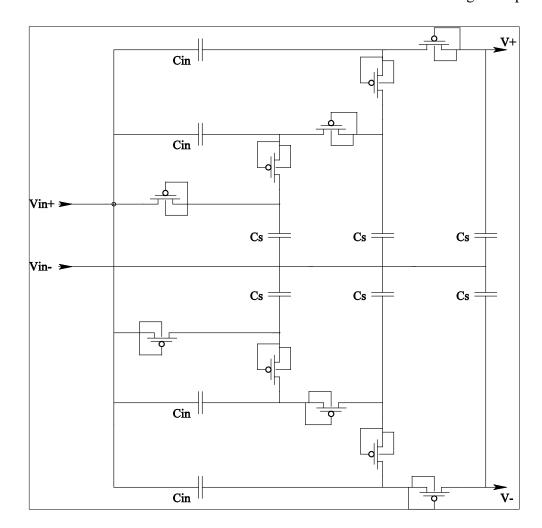

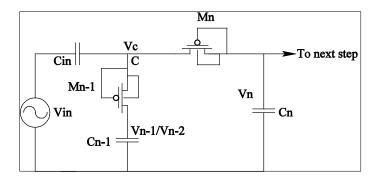

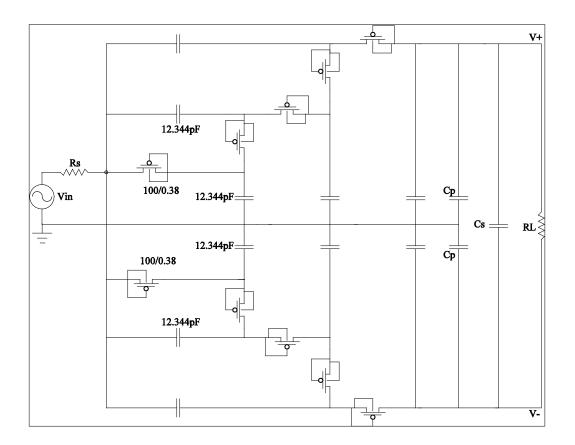

|   | 4.3.1 | Rectifying Circuit 1 – The Circuit             | 41 |

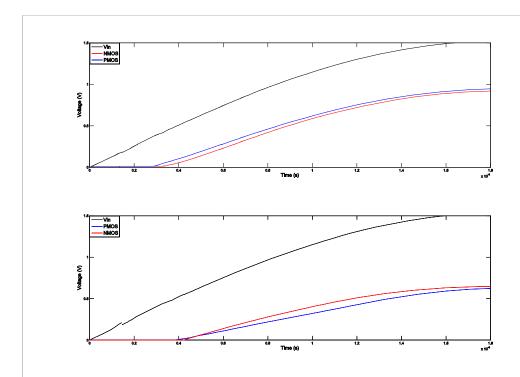

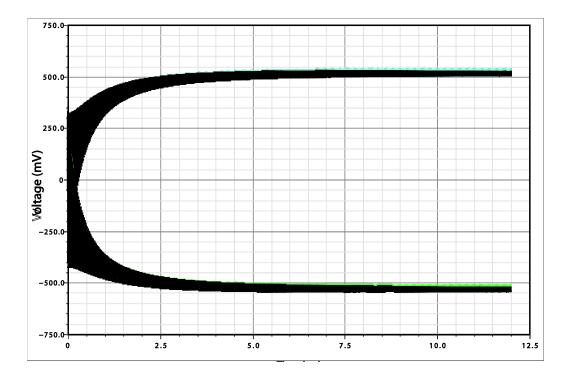

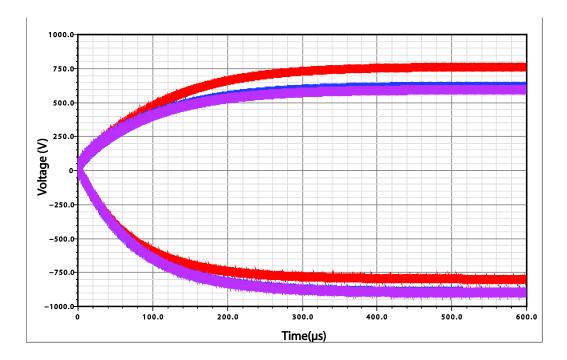

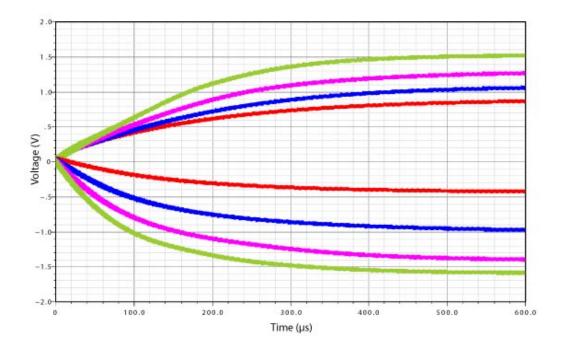

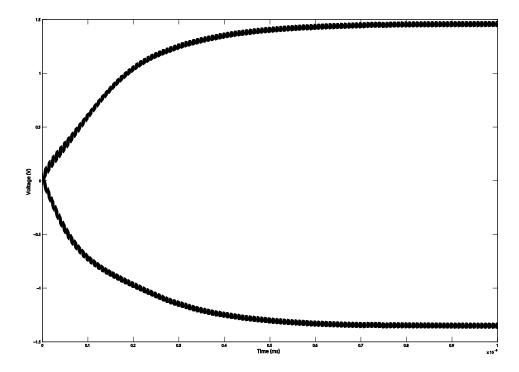

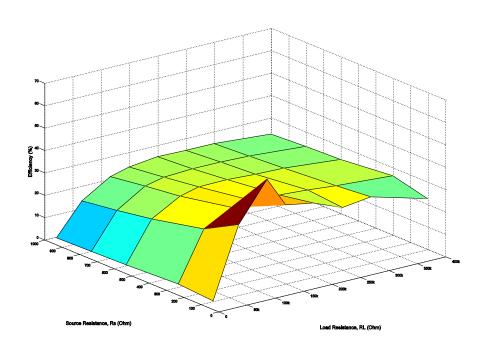

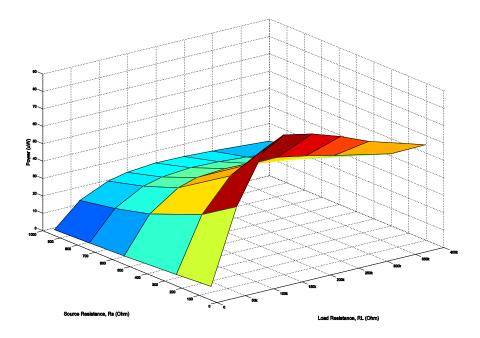

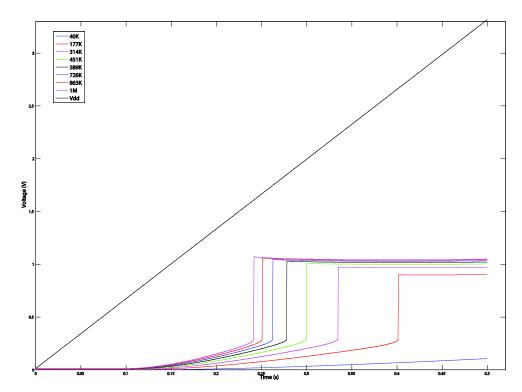

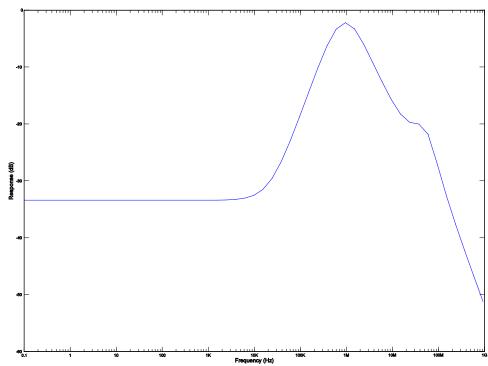

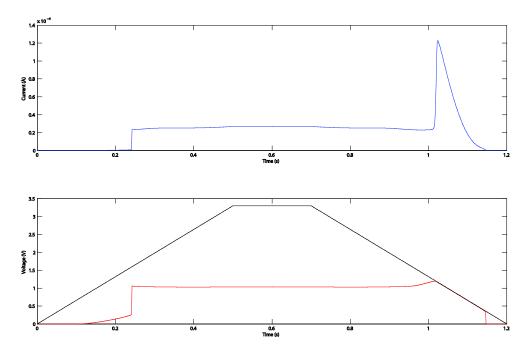

|   | 4.3.2 | Rectifying Circuit 1 – Simulation Results      | 45 |

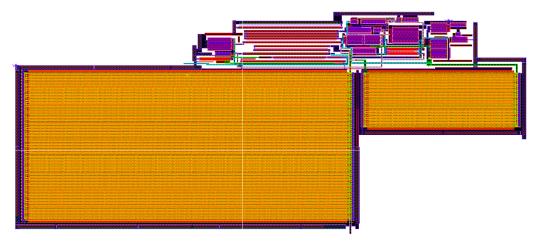

|   | 4.3.3 | Rectifying Circuit 1 – Production              | 53 |

|   | 434   | 1 Rectifying Circuit 2 – The Circuit           | 54 |

| 4.3   | 3.5 Rectifying Circuit 2 – Simulation Results | 59  |

|-------|-----------------------------------------------|-----|

| 4.3   | 3.6 Rectifying Circuit 2 – Production         | 67  |

| 4.3   | 3.7 Rectifying Circuit 3 – The Circuit        | 68  |

| 4.3   | 3.8 Rectifying Circuit 3 – Simulation Results | 74  |

| 4.3   | 3.9 Rectifying Circuit 3 – Production         | 80  |

| 5 Vo  | oltage Reference                              | 81  |

| 5.1   | Voltage references                            | 81  |

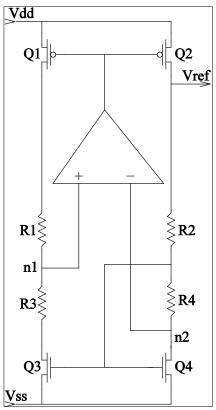

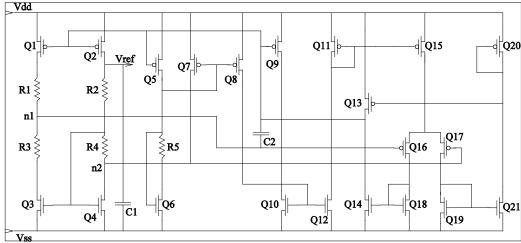

| 5.2   | Proposed Regulator One                        | 84  |

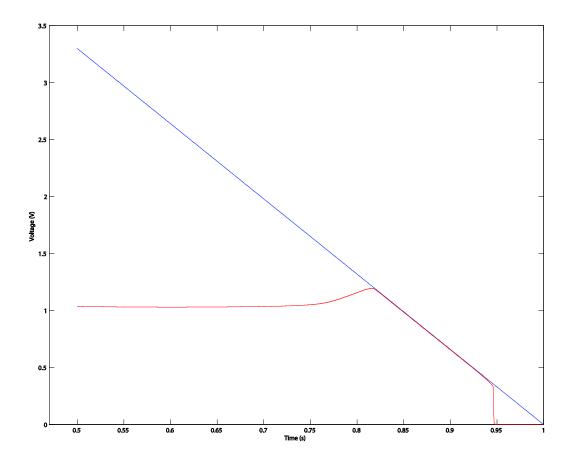

| 5.3   | Simulation                                    | 91  |

| 5.4   | Measurements                                  | 102 |

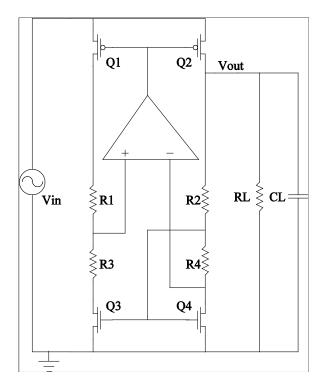

| 5.5   | Proposed Regulator Two                        | 115 |

| 6 Co  | onclusion                                     | 123 |

| 6.1   | Conclusion Rectifier and Chargepump           | 123 |

| 6.2   | Future work                                   | 125 |

| 6.3   | Conclusion Regulator                          | 125 |

| 6.4   | Future work                                   | 127 |

| 7 Bib | bliography                                    | 129 |

| 8 Ap  | pendix A                                      | 133 |

| 9 Ap  | pendix B                                      | 135 |

| 10    | Appendix C                                    | 150 |

| 11    | Appendix D                                    | 160 |

|       |                                               |     |

| 12    | Appendix E                                    | 161 |

# Chapter 1

# 1 Introduction

Many people today are taken ill of diabetes mellitus (shorted *diabetes*). In the latest passed years, this illness has become one of the most common lifestyle related diseases in the world, and is still growing. Diabetes is today an illness which the patient cannot be treated and recover fully from. It can only be controlled by measurements and injections of the hormone *insulin*, several times during a day. These measurements involve a blood sample which the patient must retrieve each time a measurement is performed, about 3-6 times per day. The pain during this procedure often keeps the patients from not performing all the recommended measurements every day, leading to an unstable hormone and glucose balance. People struck by diabetes *type one* as we shall see, is often in their younger years, and the measurements and pain associated with controlling the disease follows them throughout their life's.

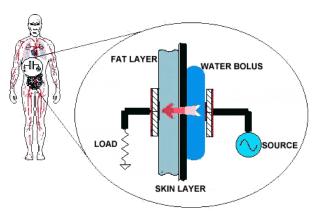

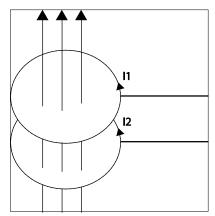

This project and thesis are meant to develop an alternative way to monitor and control this disease in a more comfortable way for the patient compared to what is done today. In this specific project, this means an implant containing a glucose sensor (LOAD), an external unit presenting the results (SOURCE), and power and communication between these two, see Figure 1.1. This can hopefully become a part of a fully automated glucose monitoring system for all diabetic patients.

Figure 1.1: The implant (LOAD) and the external unit (SOURCE) placed in the patient's abdomen

A lot of research is daily put into developing systems for monitoring and treating the diabetes disease. Many different approaches have been tried, and are still tried with more or less satisfying results as we shall see in chapter 2. This work is an investigation and development of a system for one of the methods described in V. S. Bertelsen master thesis and work done for Lifecare A/S and Sintef Oslo (1). He investigated and discussed the differences in communication between a *passive* (internal energy source not included) and an *active* (internal energy source included) form of implant for glucose monitoring. From this, the passive way of realizing the implant was chosen as the most suitable for such a monitoring system. In the following, we will present the frames and focus for this thesis based on the passive implant method.

#### 1.1 The main parts and focus of this thesis

The thesis will concentrate on the *wireless power transfer* between the internal and external part (electromagnetic fields), and the internal (implant) electronics. The implant is constructed without an internal energy source, therefore called passive, and the energy is transferred to the implant via an inductive link. The link is also used for communication, either single or dual directed but will not be particularly focused on as this is thoroughly presented in (1). The discussion focuses on reliable design solutions for on-chip, or ASIC<sup>2</sup>, realisations for the inductive link and the internal electronics. The later is both discussed and a circuit solution is presented.

It will be quit sensible to divide the glucose monitoring system into three subparts: (1) the external unit, (2) the transfer system with the inductive link, and finally (3) the internal unit or implant. Identifying and understanding the vital parameters for the inductive link is important for how the external and the internal unit should be made for best performance. Investigating the inductive link is therefore one of the first focuses.

Because of the passive way of powering the implant, an important property of the internal device is its power consumption. Because of the inductive link's limited maximum energy transfer, the amount of power consumed in the internal device is important. And not to forget, the external unit which powers the link and the internal circuitry should be portable and therefore battery driven. This means, low energy consumption is crucial for obtaining a satisfying lifetime of the battery/system. Thus, the focus will be devoted against making the electronics as efficient as possible, and therefore provide headroom for the needed energy transfer. This is important while designing medical kinds of

<sup>&</sup>lt;sup>2</sup> Application Specific Integrated Circuit

devices when reliability and flexibility is of high importance. Furthermore, the thesis will concentrate on the analogue building blocks which are necessary for many of these passive implants. These circuits are identified and investigated in the light of minimum power consume and maximum power efficiency. The aim will be to make proposals for circuits which can be implemented as these building blocks.

The energy- and measurement signals will have to travel some distance through the patient's tissue. Therefore, the electromagnetic properties of human tissue must be considered to obtain an optimal design of the communication system. The EM<sup>3</sup> fields from the power signals will interact with the tissue, and this interaction might in worst case affect the tissue itself. A medical implant is also surrounded by human tissue. Hence, its surface material must be biocompatible. This implies that the material does not cause harmful reactions in contact with biological tissue. Some materials will cause an immune reaction, other toxic. Making sure this interaction won't be harmful in any way is an area of investigation before the system can become commercial, but will not be considered further here.

The nature of the operating medium, the human body, is complex and causes challenges and care taking for other effects than for short range systems in more traditional and industrial environments. Although the discussion is based on the design of an energy and communication system for a glucose monitoring system, it will be of highly relevance for other applications for short range communication systems and medical implants together with other similar operating environments (RFID and so forth). In the following section we will see which approaches and limitations were taken the work presented in the following chapters was started.

#### 1.2 System solution guidelines

To best adjust the treatment of diabetes, a 24-7 monitoring of the blood glucose level is preferable. As we shall see in chapter 2, one of the most serious limitations of traditional glucose monitoring system today, is the pain associated with obtaining the needed blood every day. Besides of being painful, it also takes time and equipment and therefore makes it difficult to convince diabetics to do all of the necessary number of tests. A new system, besides of being painless for the patient, it also have to be comfortable to wear and not limit his or her overall life quality. The level of user involvement necessary for the system to operate properly is also important, and ideally, it should be zero. This

<sup>&</sup>lt;sup>3</sup> EM – Electro Magnetic

ideal system would be completely automated, only interfering with the user's daily business if something out of the ordinary is detected. For making this easy as possible for the user, an extensive data acquisition and processing system should be implemented, telling the user precise what have been detected. Furthermore, a communication link and software to a PC or another suitable device could help extract and keep large amount of data from the measuring system. For even more automation, a communication link from the monitoring system to an *insulin pump* would make the system complete. As described in chapter 2, insulin pumps are already developed and in use. This leaves us with a fairly easy task to make a fully automated diabetes treating system when the monitoring system first is at place.

The patient would have to undergo an invasive procedure<sup>4</sup> to get the implant placed inside the body. With such a procedure, it always follows a risk of infection where as the skin forms an outer barrier against foreign objects. The physical shape, size and material must be designed to ease handling and make the invasive procedure as simple as possible. The shape of the implant is especially important to ensure a perfect placement since the alignment to the outer unit is important. Furthermore, the implanted device should be as general and independent of differences in physical appearance of the users as possible, making it easy to mass produce. Individual adjustments always make production far more expensive.

As already mentioned, the monitoring system contains an outer part and an implanted inner part. A simple solution could be to place the implanted device in the lower arm near the wrist of a hand. The outer part could then be a wristwatch, allowing communication with the inner part placed right beneath this watch. This short distance between the two devices would ensure an easy establish of the energy and communication link. The wrist is also quite similar among humans and is not heavily exposed for fat if the patients are overweight. This result in easy energy transfer with a little loss through the tissue, and individual adjustments or costly flexibility would probably not be necessary.

Preliminary investigations undertaken by Lifecare indicated however that the area close to the wrist was unsuitable for glucose level measurements. The measured level in body fluid seemed to change too rapidly and was heavily dependent of muscular activity. This indicates doing the measurement in any limb, arms or legs, would increase the probability of error way above the accepted level. A solution where the patient would have to sit down and rest for some minutes before the reading could take place, are not acceptable and not in intention with this projects aim.

-

<sup>&</sup>lt;sup>4</sup> invasive procedure – the skin has to be cut in order to carry out the procedure

The tests done by Lifecare, indicated that the body fluid in the abdomen is more suitable for such measurements, as the conditions were more stable here. This leaves us with a bigger technical challenge. Like many other, type 2 diabetes is considered a lifestyle disease. Therefore, it would not be unreasonable to expect that many diabetics are overweight. A large abdomen implies a larger operating distance. The relatively large attenuation of EM fields in body tissue at radio frequencies, implies harder conditions for the inductive energy transfer. Although there are many possibilities for mounting the system around the abdomen, like putting the outer part in a belt buckle and so forth, caution have to be taken before placing the implant. If the operating distance is too long, a solution like the passive discussed in this thesis will no longer be feasible. Placing the implant at the side of the abdomen is a possibility. A solution like this leads to two obvious possibilities for placing the outer unit. The first is in a belt, like the one athletes use for monitoring the heart rate during exercise and competition. The disadvantages are probably too many and it will be difficult to convince a user for wearing such a belt 24 hours a day. The second solution is to involve the user more in the execution of a measurement. If the user could move a watch containing the external part of the system over the implanted device, he or she could hold it there to the measurement was complete. This solution demands a quick measurement and will solve the distance issue for the energy transfer. It would be a sensational improvement of the glucose measurement system compared to what's in use today, although it would not fully meet the requirements for the ultimate glucose monitoring system; a complete automated system that monitors the blood sugar 24 hours a day and warns of abnormal levels or changes in the blood glucose level.

After presenting the diabetes disease in chapter 2, chapter 3 will discuss power and communication transfer between the two units (external and implant). Chapter 4 and 5 will present the internal electronics on the implant and also present circuit solutions.

| 6 | Evaluation of Rectifiers & Voltage References for a Wireless Medical Implant |

|---|------------------------------------------------------------------------------|

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

|   |                                                                              |

## Chapter 2

# 2 Diabetes and Monitoring Systems Today

#### 2.1 Short Description of Diabetes and its Treating

Diabetes mellitus<sup>5</sup> is the most common form of metabolism disease today. Diabetes is a condition where regulation of the blood sugar is not functioning properly. Untreated, the condition leads to too high blood sugar levels. Diabetes is a chronic illness caused by lack of production of the hormone *insulin*, or body cells sensitivity towards insulin is reduced. Insulin is a hormone that stimulates the cells` absorption of nutrition. Together with a couple of other hormones, the body uses insulin to regulate this amount of nutrition. When a person digests food, the secretion of these hormones increase. This means, when a person eats, sugar is released into the blood flow from digestion. Because of the lack of the insulin hormone, this sugar will not be picked up and out from the bloodstream into the cells, leading to the person becomes to "sweet". The degree of which this effects, divides the diesis into two types.

Type 1 was formerly known as insulin dependent. Suffers from this condition does not produce insulin as a result of damage to the cells in the pancreas that normally would produce the hormone. The damage is often caused by an autoimmune reaction<sup>6</sup>. These patients are dependent upon regular injections of insulin. Some patients carry a pump that provides this continuous supply of insulin. Without, the body starts to break down fat for fuel (making weight reduction one of the symptoms) (2). A metabolic by-product of fat metabolism is referred to as a *ketone*. The presence of elevated blood ketones in this setting is known as diabetic ketoacidosis. In extreme and untreated cases, this can lead to coma and death.

<sup>&</sup>lt;sup>5</sup> The information about the diabetes disease and current treatment was mainly retrieved from the web sites of the Norwegian Diabetes Association (45), the American Diabetes Association (7) and the World Health Organization (44)

<sup>&</sup>lt;sup>6</sup> Autoimmune reaction – a malfunction in the body's immune system that causes it to attack body cells.

8

Type 2 was formerly called non-insulin dependent (or insulin independent). Despite the former name, about 70% need some kind of blood sugar reduction method. For type 2, insulin injection like in type 1, or blood glucose controlling tablets are used. For the remaining 30%, a change in diet, more exercise and weight reduction is enough for keeping the illness under control. Type 2 diabetes is caused by a complicated interplay of genes, environment, insulin and abnormalities, increased glucose production in the liver, increased fat breakdown, and possibly defective hormonal secretions in the intestine (3). The condition can develop over a long period of time. This is why many of type 2 patient are people past 40 years of age. The cells become resistant to insulin (4). This leads to lower absorption of glucose in these cells, and the pancreas increases production of insulin as a result. Because of this raise in insulin production, the liver starts to release more glucose from its glucose storage. Eventually, the pancreas becomes less able to produce insulin and the cells become even more resistant. As a result the blood glucose levels slowly start to rise. This process can go on for several years before symptoms of disease appear. Today, it is still no full understanding of how this condition arises, but scientists in Bergen, Norway, have conducted research for the cause of the disease (5). They found a connected with the digestion and are describing this condition as type 3 diabetes. This might be the first little step towards a better understanding of the arising of diabetes dieses.

As already mentioned, diabetes is treated with a strict diet with a low intake of carbohydrates. In some cases, patients are given anti diabetics which increases the effect of insulin and stimulates the insulin production. To keep the right balance between the blood sugar level and the insulin level, it is recommended that patients with diabetes monitor their own glucose level. This is done with a device called a glucose meter. A measurement means a pinprick in a fingertip to get a sample of blood. All fingertips have a large amount of pain receivers. Most patients do not think of it as a problem to carry out this procedure once or twice a day. But to be in full control of the blood sugar level, some diabetics should check their level four to five times a day. Some patients consider these repeated pinpricks quite difficult (6).

From the description above, diabetes type 1 is the worst case of the diabetes disease, and it often strikes young people, like children, youth and young grownups. If type 1 is detected, the person will be a diabetic patient the rest of his or her life. Long term complications of diabetes are more likely to occur if the patient is not given well adjusted treatment. Increased risk of heart disease, eye disorder, kidney failure and nerve damage are some of the complications a diabetic may have to face. Several studies have found a connection between the average blood sugar level and the risk of long term complication. According to the American Diabetes Association, the best known study is the Diabetes

Control and Complications Study conducted in the United States (7). The results were published in 1993 in the New England Journal of Medicine. This proved among other things that among type 1 patients, improved blood glucose control prevents or delays diabetic retinopathy<sup>7</sup>. Therapy that kept blood sugar levels as close to normal as possible reduced the damage to the eyes by 76 percent. Other studies have shown the best control of the glucose level is achieved by more frequent self-monitoring. Monitoring the blood sugar level continuously or at a sufficient rate, would give useful information for the required balancing between the intake of nutrition and the dosing of insulin.

In Norway today (June 2007), there are about 200.000 people suffering from diabetes, and around 25.000 of them from diabetes type 1. Around 600 Norwegians gets the diagnose diabetes type 1 every year, and about 250 of them are children under 15 years old. According to the World Health Organization (WHO) latest figures (June 2007), the number of people suffering from diabetes is approximately 180 million people worldwide (8). This number is likely to more than double by 2030. In 2005, an estimated 1.1 million people died purely of diabetes. The number of deaths per year where diabetes was a contributory condition was in 2005 estimated to 2.9 million. Type 2 is the most common of the types, constituting around 90 percent of the cases. Besides of the human suffering, the diabetes causes economical costs to individuals, families and the whole society worldwide. The disease often strikes people in their most productive years with depression, anxiety, pain and other discomfort (8). Some economical estimates have been made and the WHO gives examples of such estimates: China in the coming 10 years (2006-2015) will lose 558 billion USD in foregone national income due to heart disease, stroke and diabetes alone. Other calculations have been made and often show the cost of loss in production as a result of diabetes related sufferings equals or exceeds the direct health costs. Summarized in quick facts (8):

- 180 million people suffers from diabetes and it is likely to more than double by 2030

- Diabetes causes about 5% of all deaths globally each year

- 80% of people with diabetes live in low and middle income countries

- Most people with diabetes in these countries are middle aged (45-64)

- Diabetes deaths are likely to increase by more than 50% in the next 10 years

- Diabetes deaths are projected to increase by over 80% in upper middle income countries between 2006 and 2015

<sup>&</sup>lt;sup>7</sup> Retinopathy – disorder of the retina (the part of the eye where the light sensitive cells are found)

Diabetes *type* 2, the most common, is regarded as *a lifestyle* related disease. The best way to prevent problems related to it would be a change in lifestyle, from a passive life with fast food to a life with regular exercise and a more healthy diet. The next best solution would be to give the affected a good treatment so they can go on living a productive and none-affected life, contributing to society. If there is found a method for monitoring blood sugar levels at higher rates and still comfortable for the user than today's solutions, it would be decisive for its success that the solution is cost effective. This would make it profitable for society to invest in such a system as the mentioned diabetes related loss of production would decrease.

#### 2.2 Glucose Monitoring Systems Available Today

Most currently available glucose monitoring systems designed for self testing are based on measuring techniques that require blood samples. However, a lot of projects are now directed towards automated and painless systems. The Cygnus<sup>8</sup> GlucoWatch G2 Biographer and The MiniMed Paradigm REAL-Time System described at the end of this section are two systems that attempts to provide painless and automatic testing.

But first, the typical reading systems of today: This consists of a device called a sampler and a meter, in some cases also a test strip. The sampler is used to obtain a blood sample by a needle penetrating the skin when activated. Usually a fingertip, containing a lot of blood but also a lot of nerves, is the site used for tests. Some alternative meters offer the possibility of obtaining blood from other places of the body, like the upper and lower arm. However, users have reported problems and there are controversies among the expertise on how reliable these measurements are. Reports are given where differences between tests performed on the arms and tests performed on fingertips are detected (9). Research indicates an half an hour delay of the test results on the arm versus test in the fingertip. There are also more likely to get needle marks left on the arm as these sites are more sensitive. However, new testing sites can be a relief to sore fingers and used properly this might be a fairly good alternative.

When blood has been obtained, it is applied to the test spot, either on a test strip or directly into a meter. The actual measurement can now be carried out. The test spot has a coating of chemicals reacting with the blood and makes it possible to extract the glucose level. The extraction of this level is carried out in one of two ways, optical or electrochemical. They are discussed closer in section 2.4 together with this projects choice of measurement principle and sensor.

<sup>&</sup>lt;sup>8</sup> Cygnus was in 2005 bought by Animas Corporation

Glucose testing can be quite an elaborate procedure with today's system. Therefore, to reduce the user's workload, many systems have been developed trying to make measuring easier and less painful. This has led to devices where blood collection and glucose testing is done in one. Examples of these systems are the MediSense Sof-Tact from Abbot Laboratories and the One Touch Fast Take by Inverness Medical (10). These meters are easy to use, all in one procedure and can often be used other places than in the fingertip. Because it often uses a vacuum pump, pumping blood to right under the skin surface before lancing it, very small lances can be used leaving only a small mark on the skin. This makes these devices more suited for alternative site testing where there are less blood and fewer nerves. The device can also be pre-loaded with strips for some hours, making discrete measurement in public places possible. The amount of blood needed for a test is also getting smaller and smaller with newer devices. But some disadvantages follows. The process takes some time, although faster devices have entered the market. The accuracy is temperature dependent, making readings in cold and hot environment uncertain. It also has to be handled with care, often in own cases and housing, making sure the device is not exposed to anything that can un-calibre the measurement. Maintenance is also an issue. Cleaning after each test is required in some of the devices, making sure no remains affects the next result. Exposure to light, moisture and contamination often limits the lifetime of these devices.

The possibility to store results from tests taken over a longer period of time is a welcomed functionality. This makes important statistical parameters, like averages, trends, maximums and minimums over a longer period of time easily accessible, which again helps keep a better long term control. Many of the newer meters can store in the hundreds of tests. Some users still complains and would like even more storage capacity. If you perform 5 tests a day, you will have about 150 results in a month. This fills rather quickly up the limited space and the user would have to transfer the data over to a computer with a suited PC link. This is something to note when making an automated monitoring glucose system where a lot more than 5 tests per day are possible.

Two of the most promising and fairly automated systems available today are the *GlucoWatch G2 Biographer* from *Cygnus* and the *The MiniMed Paradigm REAL-Time System* from *Medtronic*, both companies located in California, USA. These are what we can call third generation monitoring system. The Glucowatch Biographer is one of the first systems attempting to fulfil the goal of a painless and automated system. The device is a non-invasive and automatic measurement for children from 7 to 17 and adults from 18 years of age (11). It is warn like a watch and made up by 2 pieces. A sensor pad called the AutoSensor is first attached to the skin. Then a watch is placed upon it and is thereby

connected to the AutoSensor. The system makes a reading every 10th minute and stores the result (up to 8,500 readings) in the memory of the watch. One AutoSensor can perform maximum 76 measurements, thus up to 13 hours wear in one sensor. Besides of showing the result, it also have an built-in alarm warning the patient for too high or too low measured values.

To work satisfactory, the system has to go through a two hour warm-up period. After this period, you have to calibrate the device with a regular meter (12). Despite this calibration, every reading has an overall 11% variation from the actual value, and every fourth reading will differ with more than 30% from the actual value. A glucose sample obtained with the GlucoWatch will also lag about 15 minutes behind a blood sample taken at the same time.

The GlucoWatch measures not on blood, but on interstitial fluid<sup>9</sup>. The sample is obtained by applying a small current across the skin. The glucose is then extracted from the sample and is drawn into hydrogel disks in the AutoSensor. Here it reacts with the enzyme glucose oxidase. This forms into hydrogen peroxide, and the sensor picks up the electric signal generated from this converting. This small electric signal is then translated into a blood glucose value and sent to the watch and displayed for the patient.

It is stressed from the FDA<sup>10</sup> that the GlucoWatch G2 Biographer is not a replacement of a regular glucose meter. Because of the many conditions under which it does not operate optimal and many sources of error, the probability of mall-function is too great. Because of this uncertainty associated with the measurements, it is not recommended to make large adjustments in the treatment or fully relay on the results from the GlucoWatch. Also, many users get skin irritations from wearing the sensor, and the system is easy to un-calibre under use, by not storing new AutoSensors in the right temperature, by too much movement on the device and so forth. Despite all the error sources, GlucoWatch was the first of a new generation meters allowing continuous testing over a period of time.

The MiniMed Paradigm REAL-Time System from Medtronic is another measuring system created for continuous monitoring for people down to seven years of age. Unlike the GlucoWatch, this system also includes an insulin pump (13). The monitoring unit together with the pump makes it the first complete and

<sup>&</sup>lt;sup>9</sup> Fluid between the cells

<sup>&</sup>lt;sup>10</sup> The American Food and Drug Administration

Figure 2.1 The three parts in the MiniMed Paradigm RealTime System© from Medtronic (13)

fully automated treating-system for a period of time for diabetes disease. The system is built up by two separate parts, monitoring device (C and D) and insulin pump (A and B), communicating with one another by an RF-link, see Figure 2.1. The monitoring system is also made up by two parts; a sensor pad (C) and a communication transmitter (D). The sensor pad is attached to the skin, and has a hypodermic needle mounted on. The needle is inserted through the skin for making measurements possible. The transmitter is then connected to the sensor pad, sending the results to the insulin pump which also presents the readings to the patient. The sensor pad can be inserted for three days at a time. After this you need a new sensor and a new location to insert it. The transmitter is rechargeable and can be used several times if treated carefully.

Like the GlucoWatch, the MiniMed needs an initialization period of two hours after insertion. It also needs calibration at least twice a day, once every 12 hours, but it is recommended that the system is calibrated three to four times a day. This calibration is provided by the patient's regular meter and the result needs to be entered into the insulin pump. The sensor is an electrode measuring glucose levels in the interstitial fluid and can be inserted by the patient himself. A hypodermic needle is used to insert the electrode and is then pulled out, leaving only the flexible electrode underneath the skin. The sensor pad has to be mounted at least two inches away from the insulin pump, avoiding errors in the measurement while insulin is inserted.

Experimental results and other functionality reports are, unlike the GlucoWatch, hard to find for the MiniMed Paradigm REAL-Time System. But, like the

GlucoWatch the FDA again stresses that the MiniMed system is not a replacement for the regular meter. It is only a supply for the regular measuring method and treatment cannot rely by measurements done by the monitoring system alone. Together with restrictions given for use, like places for insertion, the temperature dependent storage of sensors, need for calibrations and all the other cautions, it is likely to believe the accuracy of the measuring results of MiniMed is not far from the ones from the GlucoWatch. However, the MiniMed Paradigm REAL-Time System is one of the first and the most advanced automated monitoring- and treating system available today.

#### 2.3 New Solutions under Development

There are a lot of projects around the world in every continent concerning diabetes. Especially in the latest 5 years, a lot of attention has been given to this very common people disease. Large amounts of money are invested in research, both electronically and medically. Therefore, solving one of the diabetes many questions means a lot of attention and lot of earnings. This leads to competition between the researches and the researching companies, making information about coming solutions hard to find. Every firm is holding their cards close to their chest. But based on what we can see today, we can make some assumptions of what we can expect in the coming years.

Many different approaches are attempted. They span all the way from fully implanted to non-invasive. Some measures blood, some on interstitial fluid, some utilizes magnetic fields through an impedance spectroscopy. Also, we see that fully automated systems, measurement and treating in the same system, is the future. This combined with painless and continuous measurement and injection, is the ultimate goal for the electronically diabetes treating system. A brief view of some of the interesting ongoing projects is given below. The information is obtained mainly from *diabetesnet* homepage (14) and the homepages of the companies.

The *Optiscan Biomedical Corporation* is developing a glucose measuring method using middle infrared radiation. This semi-invasive method applies IR-radiation with 9-10 different wavelengths and measures the phase-shift of the returning waves. This is done after rapidly cooling down an area of skin for test. One disadvantage is absorption of the IR-waves in water, which is the major component of blood and interstitial fluid. Another is because there is no temperature difference between the glucose and the water beneath the skin, they cannot be differentiated from one another. However, accuracy appears to be good in very limited testing. It is however is reduced by individual variations, such as skin temperature, black body radiation, cooling speed and other factors.

It is still not known whether or not the system needs regularly calibration with another meter.

The Therasense FreeStyle Navigator is a semi-invasive continuous meter under FDA review (2007). The monitoring system is divided in three parts: Part one is the sensor designed to be worn for several days at a time. The sensor is placed just under the skin like a patch on the abdomen or the upper arm. The sensor measures interstitial fluid 5-6mm beneath the skin surface as frequently as once per minute. The second part is a transmitter located at the sensor site. The third part is a receiver, about the size of a pager, and can be carried anywhere on the patient's body. The receiver displays the glucose value, trends and also has a high and low alarm. It also stores the results for further investigations. Some issues are reliability, size, waterproofness and time of each sensor wear.

The Synthetic Blood International is developing a device called Implantable Glucose Biosensor. As the name indicates, this is an implanted device with an inner- and outer part. The inner part is of course the sensor, monitoring continuously the patient's blood glucose level. It is equipped with a titanium battery and a micro-processor. The size of the device is twice a cardiac-pacemaker, and made in the same bio-material as this. Results are digitally displayed by the outer unit, with a size like a beeper. The total implant lifetime is about a year.

#### 2.4 Sensor Technology

Many ways of measuring glucose or other chemicals have been tested and/or used in the past years of diabetes research. Two of the main principles are the optical sensor and the current sensor. Some of them utilises blood or a body fluid directly, while others use reflection in the skin or detecting changes in radio waves. The oldest and the most common type of sensor and often used as reference because of the superior accuracy, are the two types of test strip measurements. In both cases, a drop of blood is collected on a test strip and fed into the sensor. This sensor is either optical or electrochemical. In both cases, the drop of blood are mixed with other chemicals and then tested on. In the optical case, the mixed chemicals form a blue colour. By measuring the intensity of this blue colour, the glucose level is extracted (15). Although this method gives accurate results and measurement, the newer electrochemical is about to become superior. This method has a lot lesser demands of cleaning and maintenance compared with the optical. This ensures even more polite results. Again, by adding a drop of blood to a test strip and mixing it with other chemicals, the level of glucose can be extracted by measuring the current trough the sample. About 1µl blood is needed and the measurement only takes second.

16

Because of the human- and chemical factors involved, one of the largest sensor challenges is to make a sensor capable of providing reliable measurements over a long period of time without maintenance like cleaning and so forth. Also, when making a sensor for long time implantation, the use of a reactant to perform the measurement is excluded. This is a crucial success factor in continuous monitoring systems where the sensor cannot be repeatedly extracted for maintenance and reactant refilling. Many promising sensors and monitoring systems have failed because of the human body tend to reject foreign objects or clots have formed in the sensor mechanism. The sensor used for this project is based on osmotic pressure. The sensor is a closed chamber with a reference liquid inside and a semipermeable membrane as one of the chamber walls. This membrane separates the internal reference liquid from the interstitial fluid, but it also act as a tunnel for molecules smaller than a given size. This means, small water molecules can flow through the membrane, larger dissolved particles cannot. The large particles, based on the density in the reference liquid versus in the interstitial fluid, will therefore cause a chemical potential to arise across the membrane. This potential will enforce a net diffusion of water through the membrane in a try to equalize the two concentrations. Eventually, a equilibrium between the internal and the interstitial fluid concentration is reached and the water diffusion will come to a stop. The pressure change inside the reference chamber is dependent on the amount of water flown in or out through the membrane. The amount of water is again dependent on the concentration difference inside and outside the membrane.

This means, if we could make a membrane selective for glucose molecules alone, we would have a perfect sensor. This is however not the case. The membranes selectivity is based on a diffusion resistance depending on the molecule size. This means, if we could draw a resistance curve versus molecule size, it would show an increasing resistance for increasing particle size. However, the membrane cannot guarantee molecules in any given size to pass or not pass through the sensor membrane. This lack of a sharp cut-off in particle size is a source of error. Also, second order effects will be present if other substances than glucose could change the water diffusion. The membrane stiffness is also an error-source as the volume inside the reference chamber would change if the membrane were flexible. Response time is also an important factor. How rapid changes in the glucose concentration can the sensor and membrane follow? And, the body tends to reject all foreign objects introduced to it. Which effect would this have on the response time and the long time stability of the sensor and system? These points and questions are crucial when a sensor is developed and later tested.

### Chapter 3

# 3 System Review and Energy transfer Theory

One of the goals in this project is to make the implant so small it can be fitted into any part of the body. Because the size is important, batteries or other power sources cannot be mounted onto the implant. We therefore have to feed the implant with power from outside. The easiest way of doing this is of course by having wires through the skin, from a battery mounted outside the body to the implant on the inside. From an electronic point of view, this would be the most effective and safest way of providing enough energy at all times. This is not possible however. The human body and skin will not allow this kind of solution, as it will immediately lead to inflammation, poisoning and other unwanted reactions. Energy must therefore be transferred wirelessly from the external unit to the internal. This chapter will present this kind of energy transfer, and look at some aspects and formulas connected to such a system. It will start with going through a total system description and review of its parts and functionality. The following sections look at the basic physics in such inductive energy transfer, before a possible system solution is presented. At the end, some additional aspects are discussed, forming a complete picture of the energy transfer.

#### 3.1 System Review

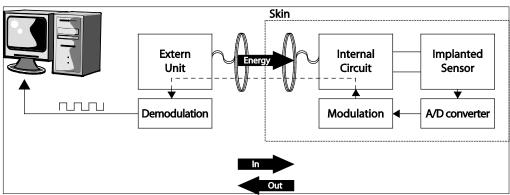

Figure 3.1 The different system parts

Figure 3.1 shows a graphic overview of the complete system. Starting on the outside of the body, or the skin, we find the *external unit*. This is the unit the patient will experience, and its tasks will be:

- powering itself and the internal unit

- receive the measurements from the internal unit

- process and present the readings and results to the patient

- storing an amount of results and be compatible with PC/Mac to transfer results for long term storing and control

Inside this *external unit* it will have to be a coil, and the *internal unit* must also contain a coil. In Figure 3.1, these coils are drawn individually from the external and internal units for better illustration of the system. These two coils are the main part in the wireless energy and communication transfer. By placing two coils on top of each other in a fairly distance from one another, we will create what is called an inductive link. This rather large field of physics and electronics will be discussed and calculated further in the following sections.

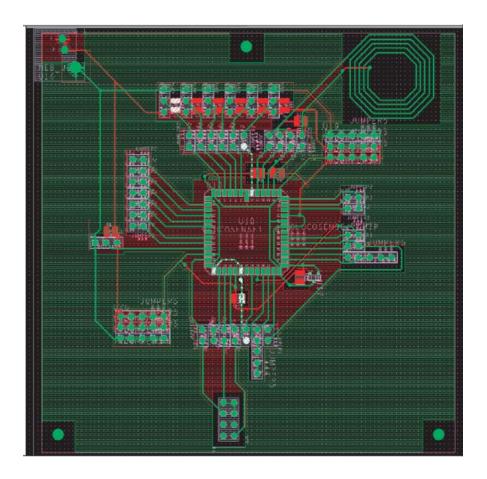

Inside the body, together with of the mentioned coil, we find the implant. Again in Figure 3.1, the sensor itself, the A/D converter and the modulator are drawn separately from the internal unit for better illustration. However, all this circuits are fabricated on the same PCB<sup>11</sup>/ASIC. We will use Figure 3.1 and specify the internal unit-, sensor-, A/D converter- and the modulator tasks separately:

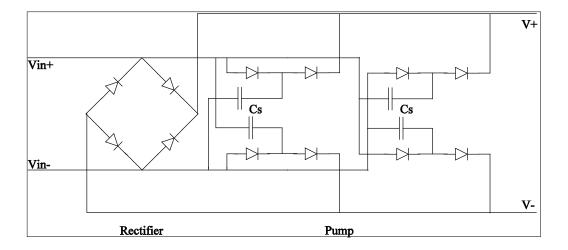

The Internal Circuit tasks will be:

- convert the incoming AC power-signal to DC current

- charge a supply capacitor for use as battery during measurements

- regulate the power signal to a stable 1V supply

The Implanted Sensor tasks will be:

- measure the glucose level in the patient interstitial fluid

- change its resistance based on the measured glucose level

The A/D converter tasks will be:

• convert the current signal from the sensor into a digital signal

<sup>&</sup>lt;sup>11</sup> PCB – Printed Circuit Board

The Modulation tasks will be:

- modulate the digital signal from the A/D converter

- transfer the modulated signal to the external unit for patient presentation

This quick overview shows all that's needed for making a fully automated glucose monitoring system. Beside of this electronic part, some medical areas need to be investigated. Some of them are what materials the implant can be made of that the body won't reject, places to implant the sensor where the readings are accurate, how long the implant will survive in the body before it has to be replaced and so forth. This thesis will not discuss these questions further, but rather concentrate on the inductive link and the electronics of the Internal Circuit.

#### 3.2 Inductance

The sensor and implant need energy to function and to do the measurements. Of reasons mentioned earlier, this energy needs to come from outside and be picked up and stored by the implant. A well known method of transferring energy over short distances is by electromagnetic induction, known as an inductive link. In the following, we will look at the basic physics of this electromagnetism and induction.

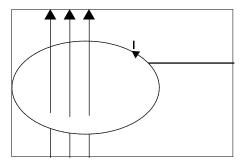

Figure 3.2 Electrical leader inside magnetic field

In a homogenous magnetic field, we denote the field strength **B**. By placing a circular electric leader inside the field we get what is shown in Figure 3.2. The magnetic flux, denoted  $\Phi_{B}$ , is defined as the field strength through a given area (the circular area given by the electric leader):

$$\Phi_{\rm B} = \int \overrightarrow{\boldsymbol{B}} \cdot d\mathbf{A} \tag{3.1}$$

If the magnetic field is changed over time, i.e. changes direction, the flux is changed and it will induce a *charge*. This is known as the Faradays induction principle and defined as:

$$\varepsilon = -\frac{d\Phi}{dt} \tag{3.2}$$

where  $\varepsilon$  denotes the induced electromagnetic charge.

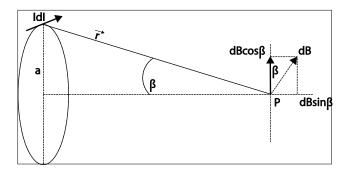

Biot-Savarts law defines how the magnetic field contribution in a single point is affected by an infinitesimal current, *Idl*:

$$d\vec{B} = \frac{\mu_0 I d\vec{l} \times \vec{r}}{4\pi |\vec{r}|}$$

(3.3)

where r is the distance between the point and the current source, and  $\mu$  is the permeability. Figure 3.3 shows this magnetic inductance in a point P.

Figure 3.3 Magnetic field contribution in a single point P

By integration of the whole current-loop, the total magnetic field is derived:

$$\vec{B} = \oint \frac{\mu_0 I d\vec{l} \times \vec{r}}{4\pi |\vec{r}|^3} \tag{3.4}$$

In equation 3.4 it is seen that the magnetic field is direct proportional to the current. This also means the magnetic flux is proportional to the current and can be expressed as:

$$\Phi_B = L \bullet I \tag{3.5}$$

where L is a constant expressing the relationship between the current and the magnetic flux density, also known as *inductance* and measured in the SI unit Henry (H):

$$1H = 1 \left\lceil \frac{V \bullet s}{A} \right\rceil \tag{3.6}$$

An inductor can be looked at as simply a lot of current-loops connected together. If we put N current-loops together and using formulas (3.4) and (3.5), we can derive the expression of an inductor:

$$L = \frac{N\Phi_B}{I} = \frac{N\int \vec{B} \cdot d\vec{A}}{I} = \frac{N\mu_0}{4\pi} \int \frac{d\vec{l} \times \vec{r}}{|\vec{r}|^3}$$

(3.7)

From (3.7) it is seen that L is decided from the number of turns N, the radius r, and the geometrical shape of the turns/inductor. Formula (3.7) can be seen in a numerous types of forms based on the shape and type of inductor.

#### 3.3 Mutual Inductance

A common definition of mutual inductance is: two separated current-loops where an alternating current *in the first* will make a change in magnetic flux, and there on induce a charge *in the second*. This will be the case if we place two electrical conductors in the same magnetic field **B**, as in Figure 3.4.

Figure 3.4 Mutual Inductance; two current loops placed closely together will interfere with one another and affect the charge and current flowing through the two leaders

2.2.

By having this figure in mind, we will derive an expression for the mutual inductance. Each inductor will have two flux contributions; let us start with the second one. The first contribution is its own current,  $I_2$ , which we can denote  $\Phi_{22} = L_2I_2$ . The second contribution is from the variation of the current in inductor one, inductive coupled to our second inductor, and can be denoted  $\Phi_{21}$ . In the same way as  $\Phi_{22}$  is proportional to the current  $I_2$ ,  $\Phi_{21}$  will be proportional to  $I_1$ . A constant, denoted  $M_{xx}$ , will therefore fulfil and connect the relationship between the two inductors and their currents. We can therefore write:

$$\Phi_{21} = \mathbf{M}_{21} \mathbf{I}_1 \tag{3.8}$$

By using the same principles as for (3.7) we can derive what is known as Neumanns formula, an expression of mutual inductance:

$$M = M_{12} = M_{21} = \frac{\mu_0}{4\pi} \oint_1 \oint_2 \frac{d\vec{l_1} \cdot d\vec{l_2}}{|\vec{r}|}$$

(3.9)

The mutual inductance M is, like the self inductance L, a geometrical dependent constant affected by the two loops shape and placing to one another. By deciding this, for example two similar inductors placed above each other, the mutual inductance M can be expressed as a function of only distance r between the two coils.

The last but important factor we will mention is the coupling coefficient, denoted k. Since the magnetic flux from loop one working on loop two,  $\Phi_{21}$ , never can be greater than  $\Phi_{22}$ , the factor k is used and we say  $\Phi_{21} = k_{21} \Phi_{22}$ . Since  $\Phi_{22} = L_2I_2$ , and  $\Phi_{21} = M_{21}I_2$ ,  $M_{12}$  can be expressed as:

$$M_{21} = \frac{\Phi_{21}}{I_2} = \frac{k_{21}\Phi_{22}}{I_2} = k_{21}L_2 \tag{3.10}$$

Keeping in mind (3.9), we look at the flux contribution on loop one, giving  $M_{12} = k_{12}L_1$  and there on  $M^2 = M_{12}M_{21} = k_{21}k_{12}L_1L_2$ , means:

$$M = \sqrt{M_{12}M_{21}} = \sqrt{k_{12}k_{21}L_{1}L_{2}} = k\sqrt{L_{1}L_{2}}$$

(3.11)

and

$$k = \frac{M}{\sqrt{L_1 L_2}} = \frac{M}{L}$$

(3.12)

where  $k = k_{12}k_{21}$  can adopt values between 0 and 1. This is a very useful parameter/constant and is given much attention during coil and system design. A large k, close to one, will ensure good "contact" and energy transfer between the two coils.

#### 3.4 The System

One of the important goals in developing this type of system is the energy loss, or energy dissipation. Especially because the external unit is battery powered, high efficiency in the power transfer is therefore important. One of the key elements in this is the resonance circuit in both the internal and the external unit (16) (17) (18) (19). In the literature it is augmented for using 2. order RLC filters in series in the external unit, and in parallel in the internal. Both filters should be tuned into the same resonanc frequency which equals the frequency of the AC signal produced by the external unit. Table 3.1 shows the two different circuits and their impedance which is the key for making use of resonanc circuit.

|     | Circuit           | Schematic | Impedance                                                |

|-----|-------------------|-----------|----------------------------------------------------------|

| Z1  | RLC - series      | R1 C1 L1  | $R_1 + \frac{1}{j\omega C_1} + j\omega L_1$              |

| Z2  | RLC -<br>paralell | C2 — R2   | $ \frac{j\omega L_2}{+\frac{R_2}{j\omega R_2 C_2 + 1}} $ |

| Z12 | Inductive<br>link | L1) {L2   | jωkL                                                     |

Table 3.1 RLC configuration for 2. order filters

At resonance, only the real part of the impedance will be energy dissipating. The imaginary part of the impedance will cancel out and therefore lowering the total amount of energy dissipated in the transfer system. Thus, by using these resonating filters we can draw the first schematic overview of the total system, Figure 3.5<sup>12</sup>

<sup>&</sup>lt;sup>12</sup> The internal circuitry is somewhat simplified for better showing the RLC filters in the inductive. In addition to the rectifier/chargepump and voltage regulator unit, the internal system

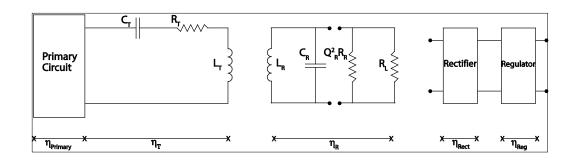

Figure 3.5 System overview

In the following investigation, we are interested in what voltage we can induce on  $L_2$  from  $L_1$ , and there on what voltage we can expect to deliver to the chargepump circuit. In help for this investigation, we will use the simplified circuit in Figure 3.6. In this figure the chargepump and the following circuits are substituted with the resistance  $R_2$ . Making it easier and less notation during the calculations of the desired voltage across it. Also,  $L_1$  and  $L_2$  are divided into two inductors on each side, this for separating the mutual inductance from the self inductance and for help to keep them apart during calculation. The calculations are in thread with the standard procedure used for such systems. Similar methods it used in the earlier mentioned (16) (17) (18) (19).

Figure 3.6 Inductive link elements with load resistance modulating the internal circuitry

By combining equation (3.2) and (3.5), the *electromotorical* voltage is derived:

$$\varepsilon = -\frac{d\Phi_B}{dt} = -L\frac{dI}{dt} \tag{3.13}$$

By applying the theory from the mutual inductance and equation (3.8)

$$\Phi_{21} = M_{21}I_1 \tag{3.8}$$

consists of a storage capacitor, voltage protection diode and the circuit boxes shown in Figure 3.1

we can derive an expression of the induced voltage by means of change in the magnetic flux between two current loops in a fairly distance from each other.

$$\varepsilon_1 = -L_1 \frac{dI_1}{dt} + M_{21} \frac{dI_2}{dt} \tag{3.13}$$

The index in equation (3.13) indicates a current in the second loop affecting loop 1. However, by changing the indexes, the opposite can be found; a current in loop 1 affecting loop 2 and thereby inducing a voltage,  $\varepsilon_2$ . As for our intention of providing a voltage across  $L_2$  in Figure 3.5 as high as possible,  $L_1$  must be exited with an alternating current at a curtain frequency. A brief discussion of the actual choice of frequency will follow in section 3.5. As we want oscillation on both sides (external and internal) for ensuring maximum power transfer efficiency, the frequency and the capacitor and inductor values must be chosen to achieve that. For the external series resonating circuit, this means:

$$f_r = \frac{1}{2\pi\sqrt{L_1C_1}}$$

(3.14)

The real impedance of  $L_I$  and  $C_I$  in series is equal to zero at oscillation frequency;  $R_I$  is therefore the only ohmic resistance and will be a current limiting resistance in this system.

In the internal oscillating circuit,  $L_2$  is placed in parallel with capacitor  $C_2$ . Although this may look as a short, their impedance at the resonance frequency is ideally infinite. Therefore, high voltages can be achieved over these elements, and the leakage will be approximately zero. This voltage can then be taken out across  $R_2$ , or in Figure 3.5, the chargepump circuit. In the following, we want to calculate this voltage,  $V_2$ , based on the induced voltage;  $V_m$ .  $V_2$  is therefore just a voltage divided between  $L_2$ ,  $C_2$  and  $R_2$ :

$$V_{2} = \frac{\frac{R_{2} \frac{1}{j\omega C_{2}}}{R_{2} + \frac{1}{j\omega C_{2}}}}{R_{2} \frac{1}{j\omega C_{2}}} V_{m} = \frac{R_{2}}{j\omega L_{2}(1 + j\omega C_{2}R_{2}) + R_{2}} V_{m}$$

$$j\omega L_{2} + \frac{R_{2} \frac{1}{j\omega C_{2}}}{R_{2} + \frac{1}{j\omega C_{2}}}$$

(3.15)

As equation 3.15 is a very useful formula for the internal circuit itself, we want to extend it into an expression where we include the current in the external unit. This means, substituting  $V_m$  to  $I_I$ . As  $V_m$  is the induced voltage across  $L_2$  caused by the mentioned current  $I_I$  in the external unit, we get the relationship:

$$V_m = j\omega M I_1 \tag{3.16}$$

This leads to

$$V_{2} = \frac{R_{2}}{j\omega L_{2}(1+j\omega C_{2}R_{2})+R_{2}}j\omega MI_{1}$$

(3.17)

by combination of (3.15) and (3.16). As our ultimate goal is to find an expression for  $V_2$  given  $V_I$ , we need to apply Ohm's law together with (3.17). This implies to find the total impedance on the external circuit. First, the impedance in the internal circuit is:

$$Z_2 = j\omega L_2 + \frac{R_2}{1 + j\omega C_2 R_2}$$

(3.18)

The relationship of the impedance through the inductive coupled coils are stated in (20) and gives the  $Z_{12}$ , the impedance in the internal circuit through the inductive link and working on the external unit:

$$Z_{12} = \frac{\omega^2 M^2}{Z_2} \tag{3.19}$$

The total impedance of the external unit is therefore:

$$Z_{1} = R_{1} + j\omega L_{1} + \frac{1}{j\omega C_{1}} + Z_{12}$$

(3.20)

This implies, by exciting the external circuit with the voltage  $V_I$ , the following expression yields for the current  $I_I$ :

$$I_{1} = \frac{V_{1}}{R_{1} + j\omega L_{1} + \frac{1}{j\omega C_{1}} + Z_{12}}$$

(3.21)

As for the final step, combining (3.21) and (3.17) gives:

$$V_{2} = \frac{\frac{R_{2} j\omega M V_{1}}{R_{1} + j\omega L_{1} + \frac{1}{j\omega C_{1}} + \frac{\omega^{2} M^{2}}{Z_{2}}}}{j\omega L_{2} (1 + j\omega C_{2} R_{2}) + R_{2}}$$

$$\downarrow \qquad (3.22)$$

$$V_{2} = \frac{R_{2} j \omega M V_{1}}{j \omega L_{2} R_{1} (1 + j \omega C_{2} R_{2}) + R_{1} R_{2} + j^{2} \omega^{2} L_{1} L_{2} (1 + j \omega C_{2} R_{2}) + j \omega L_{1} R_{2} + \frac{j \omega L_{2} (1 + j \omega C_{2} R_{2})}{j \omega C_{1}} + \frac{R_{2}}{j \omega C_{1}} + \frac{j \omega^{3} M^{2} L_{2} (1 + j \omega C_{2} R_{2})}{Z_{2}} + \frac{\omega^{2} M^{2} R_{2}}{Z_{2}}$$

As stated earlier in the section, by keeping the transfer frequency fixed and choosing  $L_1C_1/L_2C_2$  to oscillate at this frequency, expression (3.22) can be simplified<sup>13</sup> (not shown here) to:

$$\left|\frac{V_{2}}{V_{1}}\right| = \frac{kR_{2}\sqrt{\frac{L_{1}}{L_{2}}}}{\sqrt{(R_{1} + k^{2}R_{2}\frac{L_{1}}{L_{2}})^{2} + (\omega_{r}k^{2}L_{1})^{2}}}$$

(3.23)

From (3.23) we see the coupling coefficient k, is present both in the numerator and denominator. This complicates the calculations, and if (3.23) is derived with respect to k, it becomes clear that  $|V_2|/V_1|$  shows a maxima at a certain value of k, called  $k_{crit}$ . As k is a function of distance, it is easy to imagine a looser coupling when the spacing of the two coils is increased. However,  $|V_2|/|V_1|$  is also lowered when the distance is shorter than the distance of  $k_{crit}$ . This is not so simple to realize. A closer connection between the two coils leads to a higher  $Z_{12}$ . This will lower  $I_1$ , and then again lower the induced voltage across  $L_2$ .

As  $k_{crit}$  is an important value, Q-factor (quality factor) is also mentioned in such systems. Q-factor is also used in describing other systems and also smaller components like coils and so forth. In connection with the above, we define the Q-factor as (21):

<sup>&</sup>lt;sup>13</sup> When  $\omega^2 = 1/L_2C_2$ , the  $Z_{12}$  becomes real (the imaginary part is zero), and therefore the presents of the internal unit trough the coupling M will not alter the resonance frequency of the external circuitry. Keeping  $Z_{12}$  purely real for all values of k is important for the resonance and the total functionality of the transfer system.

$$Q = 2\pi \frac{Energy stored in the circuit}{Energy dissipated in the circuit during one periode}$$

The Q-factor of the coils used in the system above is therefore  $Q_{L1} = \frac{\omega L_1}{R_{L1}}$  where

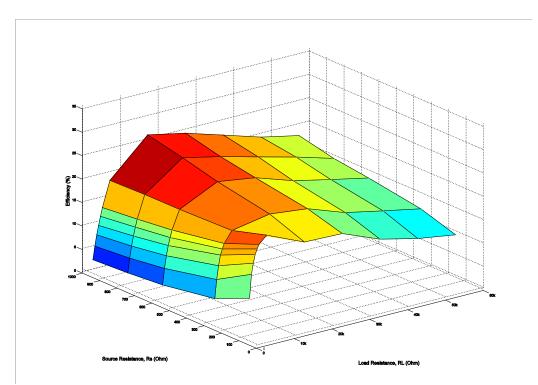

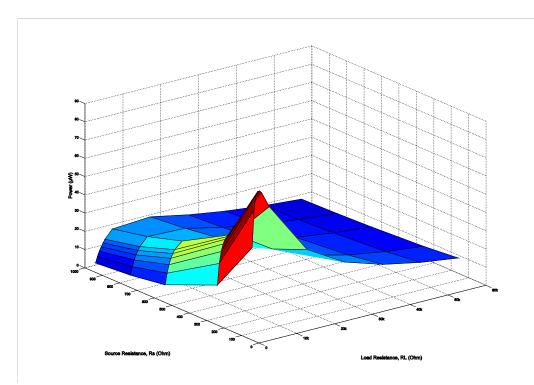

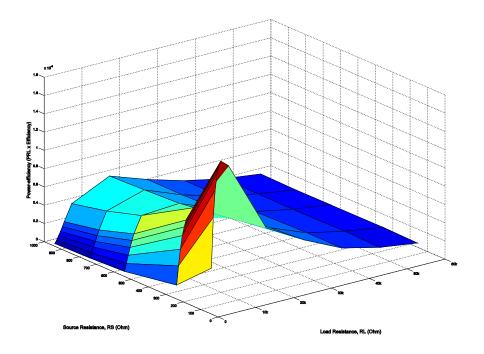

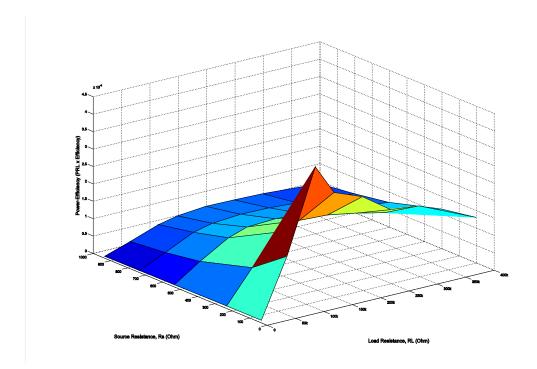

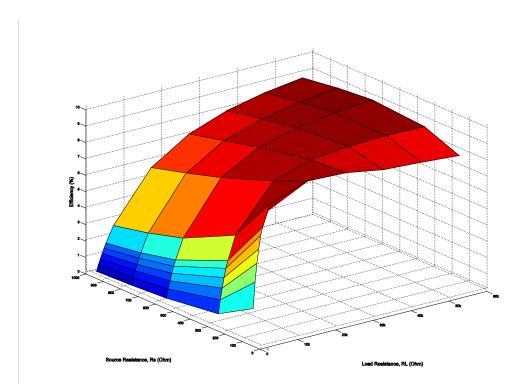

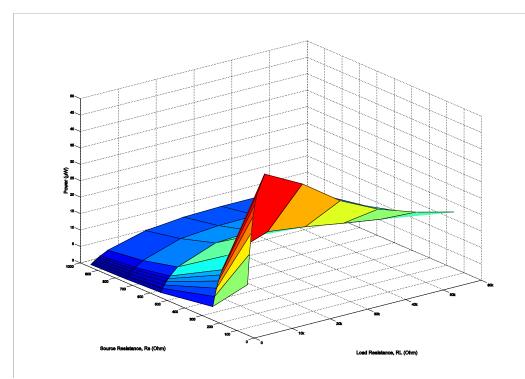

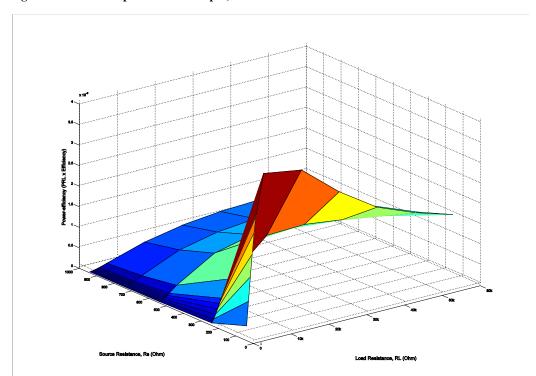

$R_{LI}$  is the self resistance in the coil  $L_I$ . Efficiency and Q-factor have been in focus when designing inductive power links the past few years. From the definition of the Q-factor above, we will look briefly at some of the calculation methods of the efficiency in an inductive link. Figure 3.7 defines the different efficiencies in an inductive link, denoted  $\eta$ .

Figure 3.7 A sketch of the whole system showing the different parts and their efficiency. The load connected here is the resistance RL, however, the load in the finished system will be the rectifier, regulator and so forth

From Figure 3.7 the Q-factor of the series RLC transmitting circuit is given by

$$Q_T = \frac{\omega L_T}{R_T} \tag{3.24}$$

when no magnetic field is involved,  $\omega$  is the frequency of oscillation and  $R_T$  is the total resistance. When *no* load is present<sup>14</sup> in the receiving circuit, the Q-factor becomes

$$Q_R = \frac{\omega L_R}{R_R} \tag{3.25}$$

Both the  $R_L$  and  $Q_R^2 R_R$  are not connected/taken away from the system in Figure 3.7

where  $R_R$  is a combination of the receive coil series resistance and  $C_R$  equivalent series resistance. If now  $R_L$  is added and we assume  $Q_R^2 >> 1$  so that  $Q_R^2 + 1 \approx Q_R^2$ , we can define the receive efficiency,  $\eta_R$ , for the receiver circuit as (22):

$$\eta_{R} = \frac{1}{1 + \frac{R_{L}}{Q_{R}^{2} R_{R}}} = 1 - \frac{Q_{R}^{'}}{Q_{R}}$$

(3.26)

where Q'<sub>R</sub> is the quality factor of the receiving circuit with load:

$$Q'_{R} = \frac{(Q_{R}^{2} R_{R}) \parallel R_{L}}{\omega L_{R}}$$

(3.27)

This indicates when load  $R_L$  is added, power is lost due to heating in the receiving resonance circuit. Thus, for high efficiency it should be ensured that  $Q_R^2 R_R \gg R_L$ . For high receive efficiency,  $Q_R^2$  will be much less than  $Q_R$ .

Finally, we will try to find the transmitting efficiency,  $\eta_T$ . As already augmented for, at oscillation, the impedance seen from the transmitting circuit into the receiving is purely resistive (real). This inductive coupled load can therefore be seen as a resistance in series with the transmit coil, now called  $R_{Lreflect}$  (not drawn in Figure 3.7). If we deliver power P to  $R_{Lreflect}$ , then  $\eta_R P$  will be delivered to the load. The efficiency at which we deliver this power to the load is limited by the voltage divider of  $R_T$  (drawn in Figure 3.7) and  $R_{Lreflect}$  (not drawn in Figure 3.7). From this the transmit efficiency can be derived (23)

$$\eta_T = \frac{k^2 Q_T Q_R^{'}}{1 + k^2 Q_T Q_R^{'}} = k^2 Q_T^{'} Q_R^{'}$$

(3.28)

where  $Q_T = \frac{\omega L_T}{R_T + R_{Lreflect}}$  is the quality factor of the loaded transmit circuit.

From Figure 3.7 we now have found  $\eta_{link}$ , as this is defined as

$$\eta_{link} = \eta_T \eta_R \tag{3.29}$$

Investigations show that the receive efficiency,  $\eta_R$ , can be close to one if the unloaded receive coil has a high  $Q_R$ . Thus, the power efficiency is primarily dependent on the transmit efficiency,  $\eta_T$ . To maximize  $\eta_T$ ,  $Q'_T$  and  $Q'_R$  must be made as high as is practical. However, designing for high Q-factors has is risks

as the bandwidth of the resonance circuit is given by  $\omega/Q$ . So a high Q implies a narrow operating region, not well suited for component variation, stray capacitances or even the presence of conductive materials near the coil. To avoid this,  $Q_T$  and  $Q'_R$  should be limited by potential of component variation, and then again, focus should be on designing for the optimal coupling coefficient, k, for achieve high transmit efficiency,  $\eta_T$ . Figure 3.7 also contains other efficiency measurands, like  $\eta_{Primary}$ , these will not be treated further in this thesis.

#### 3.5 Choice of Frequency

In choice of operating frequency there are many considerations. First of all, the demand of free radio frequencies is great, and authorities have therefore regulated these into bands. This is done by several instances, internationally by the International Telecommunication Union (ITU), regionally for Europe the European Conference of Postal and Telecommunications Administration (CEPT) and so on. But most important is the national regulation of the country where the frequency is intended to be used (24). Besides of the frequency itself, other parameters are also regulated. Examples are duty cycles, channel separation and out of band dampening. This has to be taken into account when choosing operation frequency. Some bands are especially allocated to different tasks and areas of use. These are to be found in the ITU Radio Regulations, Article S5, Frequency allocations. For the medical use, some parts of the spectrum well suited for this, are set aside for what is called *Industrial*, Scientific and Medical use other than communication (ISM-band). Although medical equipment because of its significance can get dispensation and use other frequencies, choosing a frequency in the ISM-band if possible saves a lot of effort trying to get the product approved and sold on the market. These ISMbands are also more or less internationally accepted, making special adaptation for other markets unnecessary.

| Lower Frequency<br>(MHz) | Upper Frequency<br>(MHz) | Center Frequency<br>(MHz) |

|--------------------------|--------------------------|---------------------------|

| 6.765                    | 6.795                    | 6.780                     |

| 13.553                   | 13.567                   | 13.560                    |

| 26.957                   | 27.283                   | 27.120                    |

| 40.660                   | 40.700                   | 40.680                    |

Table 3.2 The four lower ISM-bands defined by the ITU-R

| Frequency Band   | Maximum Radiated Effect                     | Allowed for   |

|------------------|---------------------------------------------|---------------|

| 119 – 135kHz     | 72dBµA/m at a distance of 10m               | Inductive     |

|                  | reduced by                                  | applications  |

|                  | 3dB every octave from 30kHz                 |               |

| 135 – 140kHz     | 42dBµa/m at a distance of 10m               | Inductive     |

|                  |                                             | applications  |

| 140 – 148,5kHz   | 37,7dBµA/m at a distance of 10m             | Inductive     |

|                  |                                             | applications  |

| 6,765 – 6,795MHz | 42dBμA/m at a distance of 10m               | Inductive     |

|                  |                                             | applications  |

| 13,553 –         | 42dBμA/m at a distance of 10m               | Inductive     |

| 13.567MHz        |                                             | applications  |

| 26,957 – 27,283  | 42dBµA/m at a distance of 10m               | Inductive     |

|                  |                                             | applications  |

| 402 – 405MHz     | 25 μW effectively radiated power Medical im |               |

|                  | Channel separation up to 300kHz             | communication |

Table 3.3 Frequency bands allowed for inductive applications and medical implants from the Norwegian Post- og teletilsynet, FOR-2007-04-20-439.

From an energy point of view, we are interested in transferring as much energy as possible through the inductive link before and during the measurement, ensuring stable operation and correct results. This implies a high transmission frequency if the amplitude is fixed. However, absorption in biological tissue and energy loss is larger with increasing frequency. In addition, the efficiency is affected by different frequencies. Thus, an optimal frequency would occur if it were to be measured on a complete implanted working system, with one type of coil, separation distance and alignment. Because patients are different, implantdepth can vary and other parameters can differ, this optimal frequency can only be found by a qualified guess during system construction. Also, the biological damage in the tissue when radiated several times a day must be well inside the accepted levels (25). In addition, IEEE have done a project and stated safety levels with respect to human exposure in the frequency bands between 3 kHz and 300 GHz which should be followed (26). Similar projects reports on different transfer frequencies, and many around 13MHz (27) (28). In thread with these reports and the possible frequency bands in Table 3.2 and Table 3.3, 13.56MHz is chosen as transfer frequency when designing the following circuitry (rectifier/chargepump and regulator).

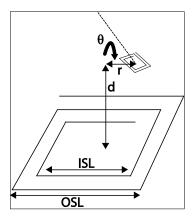

#### 3.6 Considerations around coil design

To ensure the energy transfer, we need two good coils in the system. One placed on the implant, and one on the external unit. Let us first look at the implanted. One of the design goals of the implant is size, making it as small as possible. The coil may be the largest single unit on the implant. It should be made planar, and ideally integrated on the implant. It is possible to make a coil on the silicon wafer, together with other electronics. With this solution the implant will be very compact and without too many components mounted on it. The coil can be placed around on the chip where it is space for it, filling the "holes" in the electronic. This solution however, is difficult to both make and calculate. We saw in equation (3.7) the geometrical shape of the inductor played a role in its inductance, and it may be difficult to ensure the needed power and signal transfer in this way.

A planar coil as discrete component mounted on top of the implant may in the first prototypes be the best choice. In this way the two coils (implant and external unit), can be made similar in geometrical shape and even size. When it comes to shapes, square and circular are commonly used. Even though circular coils give better performance because of the lower self resistance<sup>15</sup>, square coils are often used because of its simplicity during fabrication. In addition, the shape and mounting on the implant can be done in a way helping to keep the implant in place and not allow it to rotate as this is crucial for the alignment against the external coil. The fabrication material of the coil has, like the rest of the implant, of course to be bio-compatible, like gold or platina. Further protection between the coil and the tissue at the implanted site should be considered for patient comfort and lower health risk. Examples are noble metals, types of soft sealing like bio-compatible rubber and other types of housing for the implant. As for the coil in the external unit, this is not so critical.

The main goal when designing and choosing coils are making the power and signal transfer strong enough under all circumstances. From equation (3.9) we remember the placement of the two coils affected the mutual inductance. The coils should therefore be made in the light of the two unit's placement to one another. This means in practice choosing coils from their size, shape and value in a trade off between coupling and misalignment sensitivity (29).