# Hardware Implementations of the McEliece Cryptosystem for Post Quantum Cryptography

Petter Nyland Røneid

Thesis submitted for the degree of Master in Informatics: Programming and System Architecture 60 credits

Department of Informatics Faculty of mathematics and natural sciences

UNIVERSITY OF OSLO

Spring 2021

# Hardware Implementations of the McEliece Cryptosystem for Post Quantum Cryptography

Petter Nyland Røneid

$\bigodot$ 2021 Petter Nyland Røneid

Hardware Implementations of the McEliece Cryptosystem for Post Quantum Cryptography

http://www.duo.uio.no/

Printed: Reprosentralen, University of Oslo

#### Abstract

The ever-evolving threat landscape of cybersecurity has shown us that no bit of information is secure once enough time has elapsed. New methods of attack, analysis, and advancements in technology regularly break old cryptographic methods.

Advancements in quantum computing are now becoming a concern for the security of our asymmetric cryptography. Quantum algorithms will drastically reduce the complexity of solving the underlying security primitives and have created the need for quantum-resistant cryptosystems.

The NIST PQC is an ongoing process of selecting a quantum-resistant standard for asymmetric cryptography. One of the candidates to the NIST PQC is Classic McEliece, a system based on the now 40-year-old code-based McEliece. Despite its age, the McEliece cryptosystem with binary Goppa code is still regarded as secure and quantum-resistant with proper parameter choices.

This thesis outlines how linear codes can be used to construct cryptographic schemes. It performs a performance comparison of the software and hardware implementations of the code-based candidates Classic McEliece, BIKE, and HQC.

Finally, the hardware implementation of Classic McEliece was examined in the search for alternative designs and improvements. Some potential improvements were found, and some alternate designs performed poorly, thus reaffirming the choices of the Classic McEliece team.

# Acknowledgements

I want to thank my supervisor Thomas Gregersen. Our regular meetings early on helped me select a direction. I am very grateful for the opportunity to explore this topic, and I appreciated the high degree of freedom and independence I was given.

I would also like to thank my co-supervisors, Audun Jøsang and Åvald Åslaugson for being available when I needed help.

The current situation has been challenging for everyone, so I thank my friends and family for attempting to keep me sane.

Lastly, I would like to thank my professor of cryptography Leif Nilsen. Without taking the introductory course TEK4500, I would never have chosen this path. The course was a pivotal period in my life, and I wish Leif a happy retirement.

# Contents

| G  | lossa    | ıry                                            | 6         |  |  |  |  |  |  |  |  |

|----|----------|------------------------------------------------|-----------|--|--|--|--|--|--|--|--|

| Li | st of    | Figures                                        | 8         |  |  |  |  |  |  |  |  |

| Li | st of    | Tables                                         | 9         |  |  |  |  |  |  |  |  |

| Ι  | In       | troduction and theory                          | 11        |  |  |  |  |  |  |  |  |

| 1  | Inti     | roduction                                      | 12        |  |  |  |  |  |  |  |  |

|    | 1.1      | NIST PQC                                       | 13        |  |  |  |  |  |  |  |  |

|    | 1.2      | Research Questions                             | 13        |  |  |  |  |  |  |  |  |

|    |          | 1.2.1 Performance Comparison                   | 13        |  |  |  |  |  |  |  |  |

|    |          | 1.2.2 Hardware Description Language Generation | 13        |  |  |  |  |  |  |  |  |

|    |          | 1.2.3 Optimizations and Alternative Designs    | 14        |  |  |  |  |  |  |  |  |

|    | 1.3      | Research Methods                               | 14        |  |  |  |  |  |  |  |  |

| 2  | Theory 1 |                                                |           |  |  |  |  |  |  |  |  |

|    | 2.1      | Quantum Computing                              | 15        |  |  |  |  |  |  |  |  |

|    |          | 2.1.1 Shor's Algorithm                         | 15        |  |  |  |  |  |  |  |  |

|    |          | 2.1.2 Grover's Algorithm                       | 15        |  |  |  |  |  |  |  |  |

|    |          | 2.1.3 The end for classical PKE's              | 16        |  |  |  |  |  |  |  |  |

|    | 2.2      | Symmetric Cryptography                         | 16        |  |  |  |  |  |  |  |  |

|    | 2.3      | Asymmetric cryptography                        | 18        |  |  |  |  |  |  |  |  |

|    | 2.4      | 128-Bit Security                               | 19        |  |  |  |  |  |  |  |  |

|    | 2.5      | IND-CPA                                        | 20        |  |  |  |  |  |  |  |  |

|    | 2.6      | IND-CCA for a PKE                              | 21        |  |  |  |  |  |  |  |  |

|    | 2.7      | KEM                                            | 22        |  |  |  |  |  |  |  |  |

|    | 2.8      | NIST PQC Categories                            | 22        |  |  |  |  |  |  |  |  |

| 3  | Lin      | ear Codes                                      | <b>24</b> |  |  |  |  |  |  |  |  |

|    | 3.1      | Distance Between Codewords                     | 24        |  |  |  |  |  |  |  |  |

|    | 3.2      | Generator Matrix                               | 26        |  |  |  |  |  |  |  |  |

|    | 3.3      | Parity Check Matrix and Syndromes              | 26        |  |  |  |  |  |  |  |  |

|    | 3.4      | Encoding                                       | 27        |  |  |  |  |  |  |  |  |

|    | 3.5      | Decoding                                       | 27        |  |  |  |  |  |  |  |  |

|    | 3.6      | Hamming Codes                                  | 28        |  |  |  |  |  |  |  |  |

|    | 3.7      | Cyclic Codes                                   | 29        |  |  |  |  |  |  |  |  |

|    |          | 3.7.1 Parameters                               | 29        |  |  |  |  |  |  |  |  |

|   | 3.8               | Binary Goppa Codes                | 29<br>30<br>30<br>30 |

|---|-------------------|-----------------------------------|----------------------|

|   |                   | 0 11                              | 32                   |

| 4 | Ma                | Eliece                            | 33                   |

| 4 | 4.1               |                                   | 33                   |

|   | т.1               |                                   | 35                   |

|   |                   |                                   | 35                   |

| 5 | Dno               | grammable Logic                   | 36                   |

| Э | <b>Pro</b><br>5.1 |                                   | <b>3</b> 6           |

|   | 0.1               |                                   | 30<br>37             |

|   |                   | 1 0 0                             | 37                   |

|   |                   |                                   | 37                   |

|   |                   |                                   | 38                   |

|   |                   |                                   | 38                   |

|   |                   | 5.1.5 Ammix FI GA Doard Survey    | 30                   |

| 6 | Att               | acking McEliece                   | 41                   |

|   | 6.1               | -                                 | 41                   |

|   |                   |                                   | 42                   |

|   | 6.2               |                                   | 42                   |

|   | 6.3               | Side-Channel Attacks              | 43                   |

|   |                   |                                   | 43                   |

|   |                   |                                   | 44                   |

|   | 6.4               |                                   | 44                   |

|   |                   | 6.4.1 Anti Tampering              | 45                   |

| п | т                 | he code-based NIST PQC candidates | 17                   |

| 7 | Cla               |                                   | <b>49</b>            |

|   | 7.1               |                                   | 49                   |

|   |                   |                                   | 50                   |

|   |                   | 7.1.2 $K_{\text{gen}}$            | 50                   |

|   |                   |                                   | 51                   |

|   |                   |                                   | 51                   |

|   |                   | 7.1.5 $\mathcal{D}$               | 51                   |

|   |                   | 7.1.6 Encapsulation               | 51                   |

|   |                   | 1                                 | 52                   |

|   | 7.2               |                                   | 52                   |

|   | 7.3               | •                                 | 53                   |

|   |                   |                                   | 53                   |

|   |                   |                                   | 53                   |

|   |                   | 7.3.3 Performance                 | 53                   |

| 8  | BIF  | <b>KE</b>                                                                 | 55        |

|----|------|---------------------------------------------------------------------------|-----------|

|    | 8.1  | Niederreiter KEM                                                          | 55        |

|    |      | 8.1.1 Parameters                                                          | 55        |

|    |      | 8.1.2 $K_{\text{gen}}$                                                    | 56        |

|    |      | 8.1.3 Encode                                                              | 56        |

|    |      | 8.1.4 Decode                                                              | 56        |

|    |      | 8.1.5 Encapsulation                                                       | 57        |

|    |      | 8.1.6 Decapsulation                                                       | 57        |

|    | 8.2  | Performance                                                               | 58        |

|    | 8.3  | Hardware Implementation                                                   | 58        |

| 9  | HQ   | С                                                                         | 60        |

| Ŭ  | 9.1  | HQC KEM                                                                   | 60        |

|    | 0.1  | 9.1.1 Concatenated Codes                                                  | 60        |

|    |      | 9.1.2 Encoding                                                            | 61        |

|    |      | 9.1.3 Decoding                                                            | 61        |

|    |      | 9.1.4 Encapsulation                                                       | 61        |

|    |      | 9.1.5 Decapsulation                                                       | 61        |

|    | 9.2  | Performance                                                               | 62        |

|    | 9.3  | Hardware Implementation                                                   | 62        |

| Π  | I    | Conclusion and future work                                                | 64        |

| 10 |      | nparison                                                                  | 66        |

| 10 |      | Software Performance                                                      | 66        |

|    |      | Hardware Performance                                                      | 67        |

|    |      | Bandwidth                                                                 | 68        |

|    |      | FPGA Requirements                                                         | 69        |

|    |      | Code-Based NIST PQC                                                       | 71        |

|    |      |                                                                           |           |

| 11 |      | lerreiter with binary Goppa codes - Hardware                              | 72<br>72  |

|    | 11.1 | Encryption                                                                | 72<br>73  |

|    | 11.9 | 11.1.1 Generating <i>e</i>                                                | 73<br>74  |

|    | 11.2 | P Finite field operations $\dots$ 11.2.1 Multiplication $GF(2^m)$ $\dots$ | 74<br>74  |

|    |      | 11.2.1 Multiplication $GF(2^m)$                                           | 74        |

|    |      | 11.2.2 Squaring in $GF(2^m)$                                              | 76        |

|    |      | 11.2.5 inverting ciclicities in $Or(2^{-})$                               | 10        |

| 12 | Cor  | nclusion                                                                  | <b>78</b> |

|    | 12.1 | Future work                                                               | 78        |

|    |      | 12.1.1 Alternate Support Generation                                       | 78        |

|    |      | 12.1.2 Hardware Optimization for BIKE and HQC                             | 78        |

|    |      | 12.1.3 AVX Optimizations                                                  | 79        |

|    |      | 12.1.4 BRAM Tuning of CM                                                  | 79        |

|    |      | 12.1.5 ARM Compatibility                                                  | 79        |

|    | 12.2 | Closing                                                                   | 80        |

| A  | ppen | dices                                                                     | 81        |

| A Mathematical background     | 82 |

|-------------------------------|----|

| A.1 Finite Field              | 82 |

| A.2 Galois Field              | 83 |

| A.3 Binary Arithmetic         | 83 |

| A.4 Polynomials               | 83 |

| A.5 Irreducible Polynomials   | 83 |

| A.6 Polynomial Reduction      | 83 |

| A.7 Polynomial Fields         | 84 |

| A.8 Polynomial Addition       | 84 |

| A.9 Polynomial Multiplication | 84 |

| A.10 Polynomial Inversion     |    |

# Glossary

AES advanced encryption standard. 13

$\mathbf{AT}$  anti tampering. 45, 46

**BIKE** bit flipping key encapsulation. 55

BM Berlekamp-Massey. 31

CM Classic McEliece. 8, 9, 12–14, 35, 49–53, 67, 68, 71, 72, 78, 80

CMHW Classic McEliece Hardware Implementation. 9, 53, 54

coset leader The vector of smallest hamming weight in a coset of vectors. 28

**DES** data encryption standard. 13

DFR decoding failure rate. 29, 56, 61

**DPA** differential power analysis. 73

ELP error locator polynomial. 43

FPGA field programmable gate array. 36–39

hamming weight The number of non-zero entries in a binary vector. 33

HDL hardware description language. 14, 37, 38

HLS high level synthesis. 37, 38, 68

HQC Hamming Quasi-cyclic. 9, 35, 60, 61

IND-CCA Indistinguishability under Chosen Ciphertext Attack. 2, 8, 21, 45

IND-CPA Indistinguishability under Chosen Plaintext Attack. 8, 20, 22

ISD Information Set Decoding. 41, 42, 52

KEM Key Encapsulation Mechanism. 22, 45

${\bf LUT}$  lookup table. 36, 38

**NIST** National Institute for Standards and Technology. 13

OW-CPA One-Wayness under Chosen Plaintext Attack. 20, 22

$\mathbf{P_k}$  Public key. 16, 33

**perfect code** A code in which the distance between all codewords is the same, and decoding spheres around codewords cover the entire vector space.. 28

PKE Public Key Encryption scheme. 2, 8, 12, 16, 18, 19, 21, 22, 33, 49

**PKI** Public Key Infrastructure. 19

$\mathbf{pl}$  programmable logic. 36

PQC Post Quantum Cryptography. 13, 55

QC-MDPC Quasi-cyclic Moderate Density Parity Check. 9, 35, 55

- $\mathbf{S_k}$  Secret/Private key. 33

- **TEMPEST** Telecommunications Electronics Material Protected from Emanating Spurious Transmissions. 44

# List of Figures

| 2.1        | Communication over an insecure channel                           | 16         |

|------------|------------------------------------------------------------------|------------|

| 2.2        | Encrypted communication over an insecure channel                 | 17         |

| 2.3        | Public key encryption                                            | 19         |

| 2.4        | Indistinguishability under Chosen Plaintext Attack described in  |            |

|            | pseudo-code                                                      | 20         |

| 2.5        | Indistinguishability under Chosen Ciphertext Attack described in |            |

|            | pseudo-code for a PKE                                            | 21         |

|            | *                                                                |            |

| 3.1        | Error occurs during transmission                                 | 25         |

| 3.2        | Error is detected and corrected                                  | 25         |

| 3.3        | Hamming bounds around valid codewords (red) in a perfect code    |            |

|            | with $d = 3$                                                     | 26         |

| 3.4        | Bit flipping algorithm in [15]                                   | 30         |

| 3.5        | Parity Check matrix for A Goppa Code                             | 31         |

| 3.6        | Parrerson Decoding algorithm with a Goppa Code                   | 31         |

| 3.7        | Berlekamp-Massey algorithm in pseudo code                        | 32         |

|            |                                                                  |            |

| 4.1        | Encryption in a standard McEliece Cryptosystem.                  | 33         |

| 4.2        | Decryption in a standard McEliece Cryptosystem.                  | 34         |

|            |                                                                  |            |

| 6.1        | Exploitable leakage in an unprotected symmetric cryptographic    |            |

|            | implementation                                                   | 44         |

| - 1        |                                                                  | 10         |

| 7.1        | CM timeline                                                      | 49         |

| 7.2        | Parity Check matrix for A Goppa Code                             | 51         |

| 7.3        | Parity check matrix reduced to semi-systematic form              | 51         |

| 7.4        | SimpleKem Encapsulation used in CM                               | 51         |

| 7.5        | SimpleKem Decapsulation used in CM                               | 52         |

| 0.1        |                                                                  | 50         |

| 8.1        | Key generation for BIKE                                          | 56         |

| 8.2        | Encoding subroutine for BIKE                                     | 56         |

| 8.3        | Encoding subroutine for BIKE                                     | 56         |

| 8.4        | Black-Gray-Flip decoding algorithm used in BIKE                  | 57         |

| 8.5        | Maximal message space size for BIKE                              | 58         |

| 8.6        | Encapsulation procedure in BIKE                                  | 58         |

| 8.7        | Decapsulation procedure in BIKE                                  | 58         |

| 9.1        | Encapsulation procedure in HQC                                   | 61         |

| 9.1<br>9.2 |                                                                  | $61 \\ 62$ |

| 9.2        | Decapsulation procedure in HQC                                   | 02         |

# List of Tables

| 2.1                                                       | NIST PQC security categories                                                                                                                                                                                                      | 23                               |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| $ \begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \end{array} $ | Standard McEliece Cryptosystem                                                                                                                                                                                                    | $34 \\ 34 \\ 35 \\ 35 \\ 35$     |

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4$                                | Spartan®-6 board specifications       Spartan®-7 board specifications         Artix®-7 board specifications       Spartan®-7 board specifications         Zynq®-7000 board specifications       Spartan® - 7 board specifications | 39<br>39<br>40<br>40             |

| 7.1<br>7.2<br>7.3<br>7.4                                  | Parameters for CM                                                                                                                                                                                                                 | $50 \\ 53 \\ 54 \\ 54$           |

| $8.1 \\ 8.2 \\ 8.3 \\ 8.4 \\ 8.5$                         | BIKE QC-MDPC encoding and decoding          Parameters for BIKE          Perfomance of BIKE [6]          Perfomance BIKE hardware implementation [6]          Footprint of the BIKE implementation [6]                            | 55<br>56<br>58<br>59<br>59       |

| $9.1 \\ 9.2 \\ 9.3 \\ 9.4 \\ 9.5 \\ 9.6$                  | HQC PKEParameters for the concatenated code used in HQCSizees in bytes for HQCPerfomance of HQC [7]Perfomance HQC hardware implementation [7]Footprint of the HQC implementation [7]                                              | 60<br>61<br>61<br>62<br>62<br>63 |

| $\begin{array}{c} 10.2 \\ 10.3 \end{array}$               | Key pair generation ranked by performance                                                                                                                                                                                         | 66<br>67<br>68<br>69             |

|                                                           | PQC submissions. Ranked by time×area                                                                                                                                                                                              | 69<br>69<br>70                   |

| 10.7 | FPGA requirements for the code based NIST PQC candidates .                         | 70 |

|------|------------------------------------------------------------------------------------|----|

| 10.8 | Advantages/disadvantages of HQC $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 71 |

| 11.1 | Performance of encoder                                                             | 73 |

|      | Parameter choices probability of generating $t$ unique values on                   |    |

|      | the range $[0, n-1]$ by uniform random generation                                  | 74 |

| 11.3 | Estimated LUTs after synthesis for multiplication modules of el-                   |    |

|      | ements in $GF(2^{13})$                                                             | 75 |

| 11.4 | Estimated LUTs after synthesis for squaring modules of elements                    |    |

|      | in $GF(2^{13})$                                                                    | 75 |

| 11.5 | Estimated LUTs after synthesis for inversion modules of elements                   |    |

|      | in $GF(2^{12-14})$                                                                 | 76 |

|      | Performance comparisons for squaring modules in $GF(2^{13})$                       | 77 |

| 11.7 | Estimated LUTs after synthesis for inversion modules of elements                   |    |

|      | in $GF(2^{12-14})$                                                                 | 77 |

| 10.1 |                                                                                    |    |

| 12.1 | CM (semi systematic) performance achieved by [55] for category                     | 70 |

|      | 1 security on the ARM Cortex M4                                                    | 79 |

| A 1  | Addition and multiplication of elements in $\mathbb{Z}_3$                          | 82 |

| A.2  |                                                                                    | 83 |

|      |                                                                                    |    |

# Part I

# Introduction and theory

# Chapter 1

# Introduction

Quantum computers are coming, and with them, they bring potentially catastrophic effects on modern cryptography. If quantum computers become sufficiently powerful, the encryption techniques we use today to ensure secure communication over the internet could be broken entirely overnight, thereby compromising the confidentiality of business processes in the financial, military, commercial, government, and private sectors.

Although the quantum threat is not a certainty, [1, p. 2], the consequences of a quantum computer are too devastating to ignore.

There are two primary categories of cryptography; symmetric (Section 2.2) and asymmetric (Section 2.3). Asymmetric is the category that is used for internet communication, and the security of most asymmetric schemes rely on the difficulty of solving the factoring, and the discrete logarithm problem. With today's technology, these problems are considered to be hard (NP complexity), but if quantum computers become sufficiently powerful, they will be able to solve these problems in polynomial time. This reduction in complexity from non-polynomial to polynomial time, will render the most widely used asymmetric schemes completely broken.

This creates a considerable incentive to find replacements algorithms that are quantum resistant. NIST [2] has an ongoing selection process, the NIST PQC, that aims to select the new standard for asymmetric cryptography. Among the candidates for this selection process we find Classic McEliece (CM) [3].

CM is based on the McEliece PKE introduced by Robert McEliece in 1978 [4]. There are no known attacks that break the security of McEliece in a significant way. Because of this, McEliece is especially interesting in the NIST PQC, as it is regarded as the most tested and mature candidate to PQC.

McEliece has, however, a significant drawback: its key size. To achieve classical 128-bit security in the post-quantum world, the public key is about 1 MB. This is a far cry from our current PKEs, where for instance, an RSA key providing 128-bit security will be 3074 bit.

CM is not, however, the only McEliece based candidate in the NIST PQC. Other proposals offer smaller key sizes, but their security is still under scrutiny because they are based on newer and less tested codes. The proposals all have strengths and weaknesses, and it is not very obvious which is superior.

In addition to the numerous code-based proposals, they all have accompanying hardware implementations that can improve execution time or hardware cost. To thoroughly compare the proposals, these will also have to be included in the analysis.

# 1.1 NIST PQC

National Institute for Standards and Technology (NIST) is a US governmental agency with a long-standing history in developing and maintaining standards regarding cybersecurity. Data encryption standard (DES) was announced as the standard for data encryption in 1976. When it many years later was assumed to be insecure, NIST began a selection process to find a new standard; the advanced encryption standard (AES). The winner of this selection process was Rijndael [5], and it is not known as the AES. AES is now the defacto symmetrical encryption algorithm.

It is a similar process we find ourselves in now. The quantum threat to modern asymmetric cryptographic standards has created a need for replacements. This is where the NIST Post Quantum Cryptography (PQC) comes in. NIST PQC is a selection process for post asymmetric cryptography, with separate categories for key exchange and digital signatures.

There are four security primitives that are believed to be quantum resistant, and all the submissions are based on one of these:

- 1. Lattices

- 2. Linear Codes

- 3. Isogenies

- 4. Multivariate-quadratic

It is in this context that this work is done. The key exchange implementations that are based on linear codes will be examined to achieve insight into their construction and performance.

### 1.2 Research Questions

This work will attempt to answer the following questions that arise when developing code-based cryptographic implementations.

#### **1.2.1** Performance Comparison

Though the structure of the three code based candidates for the NIST PQC are McEliece based, they depend on the security of different linear codes. The binary Goppa codes of Classic McEliece [3] enjoy a maturity that the cyclic codes of BIKE [6] and HQC [7] do not. If the cyclic codes maintain their security in the future, will the performance of these three systems have a clear winner?

#### 1.2.2 Hardware Description Language Generation

The hardware implementation of CM generates some of its modules from Sage-Math scripts. The scripts are quite straightforward, and in most cases, they will generate the logic in terms of elementary 'xor', 'not', and 'and' gates. This is not an unusual practice, but it poses some interesting questions. It is easy to assume that generating an ideal logic like this will create a minimal circuit, but that is not necessarily true when synthesizing designs on an FPGA. The synthesized designs are complex interactions between lookup tables and not elementary gates.

It is advantageous to have a solution written in pure HDL, and because we will have a generated module and a written module, we can directly compare the footprints of each. We can then get an idea if ideal logic produces the smallest hardware design.

#### 1.2.3 Optimizations and Alternative Designs

When designing hardware solutions for cryptographic purposes, the goal is often to reduce the runtime. It is, therefore, an obvious goal to look for optimizations in either footprint or runtime in the hardware designs.

Alternative designs are could also lead to performance improvements or trade-offs. If an alternative design is found, it should be compared to the reference design and discussed.

### 1.3 Research Methods

To answer the questions in Section 1.2 requires a thorough study of code-based cryptography. This included studying the three code-based systems in the NIST PQC, getting familiar with abstract algebra and its application in cryptography, and studying hardware description languages.

To not fall into every pitfall, it was also emphasized to get familiar with the literature around attacking McEliece. Any cryptographic implementation must be created with the knowledge of the threats to its security.

Because Classic McEliece is the only code-based finalist in round 3, it was given special attention.

Running hardware synthesis requires some proprietary tools. A virtual machine running Ubuntu 16.04.07 Xenial was set up, as this was one of the only versions that support the entire toolchain. To conduct hardware simulation, Modelsim was used, and to perform synthesis, Vivado WebPack was used. In addition, to run the CM hardware code generation scripts SageMath 7.4 was installed. Note that the version numbers are important when they are explicitly stated.

The software implementation of classic McEliece was modified to produce keys, messages, and ciphertexts to be used in the hardware experiments. Then modules from the hardware submission were isolated to perform experiments. The code for the experiments can be found at:

https://github.uio.no/petternr/McElieceAPI

# Chapter 2

# Theory

# 2.1 Quantum Computing

Quantum computers, should they become a practical, will allow us to design new types of algorithms that cannot run on classical computers that are limited by the classical laws of physics. By leveraging quantum mechanics to do computations we will be able to solve new and old problems with incredible speeds by today's standards.

Unfortunately, two of these problems are the discrete logarithm problem and the factoring problem; the two bases for computational security of modern asymmetric cryptography.

#### 2.1.1 Shor's Algorithm

Shor's Algorithm [8] was designed by Peter Shor in 1994, and is an algorithm for factorization designed to run on a quantum computer. In classical computers, factorization is assumed to be hard and can not be done better than non-polynomial time, but in a quantum computer, Shor's can do this in polynomial time.

Shor later revised his algorithm to also solve discrete logarithms [9].

#### 2.1.2 Grover's Algorithm

Grover's Algorithm [10] was designed by Lov Grover in 1996. It does not reduce the complexity of any one cryptosystem like Shor's, but it reduces the complexity of all search problems.

Grover's will allow finding an element in an unstructured dataset in  $\mathcal{O}(\sqrt{n})$ where *n* is the size of the dataset. This is a huge improvement (and also quite counter-intuitive) as we traditionally would have to search through all elements and scale with  $\mathcal{O}(n)$ .

This means that every single cryptographic technology, symmetric, asymmetric and hash functions will at least have the cost of a brute force attack cut by about  $\mathcal{O}(\sqrt{n})$  (assuming that Grover can be implemented efficiently).

For this reason, it is common to scale the security level in bits by a factor of 2. This indicates a squaring search space, and will therefore negate the worst-case effects of Grover's.

#### 2.1.3 The end for classical PKE's

All PKE's in use today have security based on the hardness of either the factoring problem or the discrete logarithm problem. These problems are believed to be in the classical category NP, which means that the program that solves them will have running time-scaled exponentially with the numbers that are being computed.

Shor's algorithm [8] was invented by Peter Shor in 1994 and is an algorithm for integer factorization in polynomial time, which can be generalized to solve a general discrete logarithm problem. This is terrible news for the crypto world, as it completely breaks the security of all widely used PKE's. Luckily it can not be implemented on classical computers and can only work if larger quantum computers can be built. So if quantum computers of an arbitrary qubit-length become feasible, our current asymmetric cryptography will be completely broken.

That is not to say that RSA, DH, and EC can no longer be used, but they will require absurdly large keys to maintain the current level of security. A post-quantum RSA scheme would require a one terabyte  $P_k$ , and the cost of each new encryption and decryption would be on the scale of \$1 [11].

### 2.2 Symmetric Cryptography

Cryptography is the practice of protecting communication between two parties against an adversary which wants to read or tamper with the messages. In other words, cryptography allows us to send a message that only the intended recipient can read.

Consider Figure 2.1. Alice can send Bob a message, but everything sent over the insecure channel is visible to Oscar. To have secure communication, we have to make the information unreadable for Oscar. *Sensitive data* is indicated as red, while black indicates *non-sensitive data*.

Figure 2.1: Communication over an insecure channel

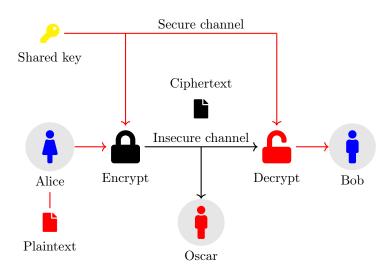

Now consider Figure 2.2, with the addition of encryption and decryption, the data sent over the insecure channel is no longer sensitive. Granted that Alice and Bob have a shared key they can use for encryption and decryption. Oscar can not obtain their communication without first obtaining the shared key.

Figure 2.2: Encrypted communication over an insecure channel

Symmetric cryptography is cryptography where the communicating parties share a secret key.

This also creates a new problem, namely, how can Alice and Bob exchange a shared key in the first place? Traditionally a secure channel will mean that they will have to exchange the key physically, but this is not always practical. For n parties to communicate securely, we need n(n-1)/2 key pairs. This is the key distribution problem.

During the cold war, the United States and the Soviet Union had a communication channel based on the one-time-pad, which requires a keystream of the same length as the message. Due to the high-security risk of these keys, armed couriers had to deliver them. Now, this was difficult enough for two parties, but imagine what it would be like for the entire world. This is the problem that asymmetric cryptography helps us avoid.

So, in summary, let us define what a symmetric scheme is. To do this; we have to create some other definitions first.

#### **Definition 1.** Spaces

A space is the set of all possible values within the context of a cryptographic scheme, where  $\mathcal{K}$  is the key space,

$\mathcal{M}$  is the message space,  $\mathcal{C}$  is the ciphertext space.

#### **Definition 2.** Encryption

Let  $\mathcal{E} : \mathcal{K} \times \mathcal{M} \to \mathcal{C}$ , encryption of a message  $m \in \mathcal{M}$  under a key  $k \in \mathcal{K}$  is done by:

$$\mathcal{E}_k(m) = 0$$

where the subscript k of  $\mathcal{E}$  implies the call  $\mathcal{E}(k,m)$  where k is fixed.

**Definition 3.** Decryption Let c be the encrypted ciphertext of m under the key k, and let  $\mathcal{D}: \mathcal{K} \times \mathcal{C} \to \mathcal{M}$  be the function that can perform decryption by:

$$\mathcal{D}_k(c) = p$$

where the subscript k of  $\mathcal{D}$  implies the call  $\mathcal{D}(k,c)$  where k is fixed.

**Definition 4.** Symmetric Cryptographic Scheme let  $k \in \mathcal{K}$  be generated by the function,  $K_{gen} : () \to \mathcal{K},$  $\mathcal{E} : \mathcal{K} \times \mathcal{M} \to \mathcal{C},$  $\mathcal{D} : \mathcal{K} \times \mathcal{C} \to \mathcal{M}$ be the function that allows decryption of  $\mathcal{E}$  so that:

$\mathcal{D}_k(\mathcal{E}_k(p)) = p$

A symmetric cryptographic scheme is  $\Pi = (K_{gen}, \mathcal{E}, \mathcal{D}).$

Note that these definitions do not define any properties that make a cryptographic scheme secure, and if  $\mathcal{E}_k$  and  $\mathcal{D}_k$  where the functions that just returned the input these would be a valid cryptographic scheme according to this definition. To have secure cryptographic scheme additional properties are necessary (Section 2.5).

### 2.3 Asymmetric cryptography

Symmetric cryptography created a problem of key distribution: how do we distribute keys to communicating parties. *Asymmetric cryptography* allows two parties with no prior knowledge to exchange a shared secret key over an insecure channel.

Public Key Encryption scheme (PKE) is often used interchangeably with asymmetric cryptography.

So like with symmetric cryptography, let us define what a PKE is.

**Definition 5.** Public Key Encryption scheme (PKE) Let the tuples of keys  $P_k$  and  $S_k$  in the respective keyspaces  $\mathcal{K}_p, \mathcal{K}_s$ ,  $\mathcal{M}$  be the message space, and  $\mathcal{C}$  be the ciphertext space.  $K_{gen}: () \to \mathcal{K},$  $\mathcal{E}: \mathcal{K}_p \times \mathcal{M} \to \mathcal{C},$  $\mathcal{D}: \mathcal{K}_s \times \mathcal{C} \to \mathcal{M}$  so that:

$$\mathcal{D}(S_k, \mathcal{E}(P_k, p)) = \mathcal{D}(S_k, c) = p$$

A PKE is the tuple  $(K_{gen}, \mathcal{E}_{S_k}, \mathcal{D}_{S_k},)$

So unlike a symmetric scheme, a PKE C will have two keys; one for encryption (public key), and one for decryption (private or secret key). The public key will as the name implies be known to the public, but the private key is the secret part of the decryption algorithm and will be kept secret by the owner of the key. There is a unique relation between  $k_{\text{priv}}$  and  $k_{\text{pub}}$  and they can not be used interchangeably; one can not use a private key to decrypt a message that was not encrypted using the corresponding public key.

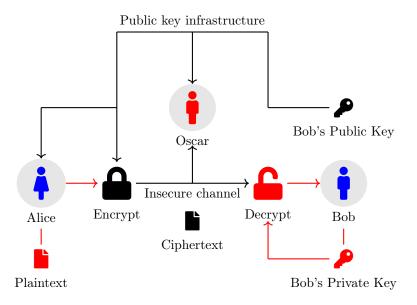

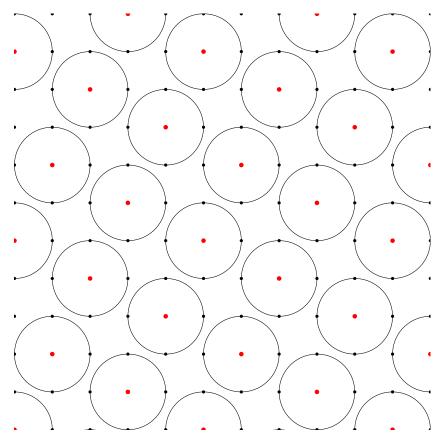

The flow of a PKE is illustrated in 2.3. Here Alice will use Bob's public key to encrypt the message, and Bob can decrypt it using his private key.

We also see that Oscar has access to Bob's public key, but he can not use this key to discern anything about what the plaintext is. The public key must be distributed using a Public Key Infrastructure (PKI). In short, a PKI is a way of distributing public keys so that their integrity is assured. If Alice requests Bob's public key, Oscar could potentially intercept and replace Bob's public key with his own. This is the problem that a PKI solves. We will not be concerned about how a PKI works, but if the reader is curious an explanation can be found in [12, p. 566].

Figure 2.3: Public key encryption

#### 2.4 128-Bit Security

A security goal is an abstract concept that allows us to compare the security of two heterogeneous cryptosystems. The gold standard of security is regarded to be 128-bit. This means that to break the security of a scheme, there must exist no attack better than a brute force search of a keyspace of 128-bit.

Breaking RSA, for instance, is equivalent to factoring the public key, which is a large number. Factoring a number has lower complexity than just bruteforcing the keyspace, and therefore an RSA key must be quite a bit larger than 128-bit to achieve 128-bit security (3072 bit).

Due to Grover's, the security goal for post-quantum cryptography is considered to be 256 bit.

### 2.5 IND-CPA

We saw from Section 2.2 that the definitions of a Cryptographic scheme does not say anything about the security of them. They could potentially completely expose the messages that they intended to encrypt, but still, meet the definition of a cryptographic scheme.

To say something about the security of a cryptographic system, we have some useful properties they can achieve that guarantees that an attacker will not be able to break the system.

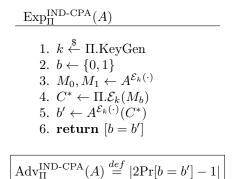

One of the primary target properties is Indistinguishability under Chosen Plaintext Attack (IND-CPA), and to achieve this property, a cryptographic system must be demonstrated to win a game. The game is defined in Figure 2.4.

$\operatorname{Exp}_{\Pi}^{\operatorname{IND-CPA}}(A)$  describes an experiment where a challenger will allow any adversary to gain access to an encryption oracle  $\mathcal{E}_k$  which will allow them to encrypt any message they want under the secret key k. In step 3, the adversary will select two messages, where one of them will be encrypted based on b. The adversary will then make a guess whether b was 0 or 1. If they are correct they win, and if they can consistently beat the game, then  $\Pr[b = b']$  will be greater than 1/2. Just by guessing an adversary will be expected to win half the time, so  $\operatorname{Adv}_{\Pi}^{\operatorname{IND-CPA}}(A)$  should be close to 0 to guarantee that any adversary can not do better than guessing.

There is a weaker security goal called OW-CPA where the adversary will not be allowed to encrypt messages, so this property only guarantees that an adversary can not find a connection between plaintext and ciphertext.

Figure 2.4: Indistinguishability under Chosen Plaintext Attack described in pseudo-code

If a cryptosystem is proven to be IND-CPA, it will imply several desirable properties of that system that apply to any adversary. Any adversary will **not** be able to:

- Learn what the message is by encrypting the  $M_1$  or  $M_2$  after step 3. This means that every encryption of the same message is different.

- Learn a connection between message and ciphertext.

- learn any bit of the message given a ciphertext even when the plaintext is known.

### 2.6 IND-CCA for a PKE

In a modern cryptosystem, only the key should be secret. The inner workings of an algorithm is assumed to be known to an attacker, so we need to create cryptosystems in a way that an attacker can not learn anything about the plaintext when observing the ciphertext.

A cryptosystem can achieve formal security if it can be shown to achieve Indistinguishability under Chosen Ciphertext Attack (IND-CCA). IND-CCA is defined as a game and is described in Figure 2.5.  $\text{Exp}_{PKE}^{\text{IND-CCA}}(A)$  describes how an attacker A can win. A secret and public key is fixed from the keyspace of the algorithm. Then a bit is fixed, and the attacker will select two messages with access to the decryption oracle  $\tilde{\mathcal{D}}_{S_k}$  and the public key. The decryption algorithm will allow the attacker to decrypt any ciphertext, but after  $C^*$  has been selected, they can not decrypt the selected messages' ciphertexts. The attacker will then guess if the bit was 0 or 1, and wins if they guess correctly.

| $\mathrm{Exp}_{\mathrm{PKE}}^{\mathrm{IND-CCA}}(A)$                                                                                                                                                                                                                                                          | $\tilde{\mathcal{D}}_{s_k}(C)$                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| 1. $(s_k, p_k) \stackrel{\$}{\leftarrow}$ PKE.KeyGen<br>2. $b \leftarrow \{0, 1\}$<br>3. $M_0, M_1 \leftarrow A^{\tilde{\mathcal{D}}_{S_k}(\cdot)}(p_k)$<br>4. $C^* \leftarrow$ PKE. $\mathcal{E}_{p_k}(M_b)$<br>5. $b' \leftarrow A^{\tilde{\mathcal{D}}_{S_k}(\cdot)}(C^*)$<br>6. <b>return</b> $[b = b']$ | 1. if $C = C^*$<br>2. return $\perp$<br>3. else<br>4. return $\mathcal{D}_{S_k}(C)$ |

| $Adv_{\rm PKE}^{\rm IND-CCA}(A) \stackrel{def}{=}  $                                                                                                                                                                                                                                                         | $2\Pr[b=b']-1 $                                                                     |

Figure 2.5: Indistinguishability under Chosen Ciphertext Attack described in pseudo-code for a PKE

$\operatorname{Adv}_{PKE}^{\text{IND-CCA}}(A)$  is the advantage an attacker can achieve over the system which fall on the interval [0, 1]. If an attacker can correctly guess *b* they must have broken the system, so we should expect an attacker to gain no advantage better than  $0 + \epsilon$ , where  $\epsilon$  is very small. So we expect an adversary to obtain no better advantage than  $\approx 0$ , which implies that the best they can do is guessing at *b*.

The definition of IND-CCA might look a bit arbitrary, but if we consider what it would take for an adversary to win this game, we can see that the definition implies some very favorable properties of our PKE.

If an adversary can not obtain a meaningful advantage in this game, they can **not**:

- 1. Obtain the key.

- 2. Learn a connection between plaintext and ciphertext.

- 3. Learn a connection between similar-looking ciphertexts.

- 4. Encrypt the same message again to compare with the given ciphertext.

- 5. Learn any bit of the plaintext given the ciphertexts.

- 6. Predict the structure of the ciphertext.

#### 2.7 KEM

A Key Encapsulation Mechanism (KEM) is often very similar to a PKE, but instead of encrypting a message, a KEM will will encrypt a symmetric key directly. This is how most asymmetric cryptography works because symmetric cryptography is much more effective in terms of time and therefore cost. A Key Encapsulation Mechanism (KEM) is usually a PKE that has been modified to encapsulate a key instead of a message, and one can then construct a PKE using the KEM to derive a shared encryption key.

A common way of constructing a KEM is to take an existing PKE with a weak security goal like OW-CPA and add an encapsulation stage to ensure that derived secret is cryptographically secure.

As seen in Definition 7, encapsulation will generate a random element m from the message space and use a function H to derive a shared secret. H is commonly selected to be cryptographically secure hash function, a function that works as a random oracle.

**Definition 6.** Hash function

A hash function  $H : \mathcal{M} \to \mathcal{H}$ , where  $\mathcal{H}$  is some fixed space  $\{0,1\}^l$ , and  $\mathcal{M}$  is the space of all messages  $\{0,1\}^*$

**Definition 7.** *KEM scheme* let  $(K_{gen}, \mathcal{E}, \mathcal{D})$  be the components of a IND-CPA secure PKE,  $H : \mathcal{M} \to \mathcal{K}^*$  $\mathcal{K}^*$  a symmetrical keyspace Encapsulate :  $\mathcal{K} \to \mathcal{C} \times \mathcal{K}^*$ Decapsulate :  $\mathcal{C} \times \mathcal{K} \to \mathcal{K}^*$  so that

$Encapsulate(P_k) = (c, K), Decapsulate(S_k, c) = K$

The components of a KEM are  $(K_{gen}, \mathcal{E}, Encapsulate, , \mathcal{D}, Decapsulate, H)$ .

## 2.8 NIST PQC Categories

The security of the NIST PQC proposals are measured by adhering to 5 categories, where 5 is the highest and 1 is the lowest. The categories are listed in Table 2.1. The type defines that the system must be at least as hard as exhaustive search for AES, or a collision search for SHA corresponding to the given size of either AES or SHA. For key exchange, categories 1,3, and 5 are the most interesting categories. 2 and 4 are more interesting when discussing signature schemes which are also subjects for the NIST PQC.

| Category | Minimum security level | type |

|----------|------------------------|------|

| 1        | 128                    | AES  |

| 2        | 256                    | SHA  |

| 3        | 192                    | AES  |

| 4        | 386                    | SHA  |

| 5        | 256                    | AES  |

Table 2.1: NIST PQC security categories

# Chapter 3

# Linear Codes

To understand what a linear code is, let us first build an intuition for what a code is. The word code in this context means that we are talking about encoding something. That is to use a symbolic representation to represent an object that is not the same as the object itself.

Mathematically a code C is uniquely identified as a subspace of a space P. That is to say that a code can be the entire space P or any proper subspace of P. This definition is not very useful as it does not tell us how to encode anything.

To encode a message from another space M we create a mapping  $G: M \to C$ so that every element  $m \in M$  corresponds to an element in C. With this mapping, we have a way to encode elements in M, but it does not guarantee us a way of decoding them. For instance if every element  $m \in M$  maps to the same *codeword*  $c \in C$  it is impossible to go the other way.

To be able to decode our encoding, the mapping needs to be reversible. In other words, it needs to be injective and therefore invertible.

The injective mapping between our two spaces  $G: M \to C$  implies that there exists an inverse function.

**Definition 8.** A code C over  $F^n$  is is a linear code iff 1.  $u - v \in C$  for all  $u, v \in C$ 2.  $au \in C$  for all  $a \in F, i \in C$ Where F is a field

## 3.1 Distance Between Codewords

Every element of our code is a codeword and can be represented as a vector. We then observe that every invalid codeword y in the larger body P will have some distance d to a valid codeword c. If we create a linear code with a clever choice of d, we will then be able to uniquely express y = c + e where  $e \in P$  with some low weight. So if a low weight vector e is added to c we will be able to detect it and hopefully correct it.

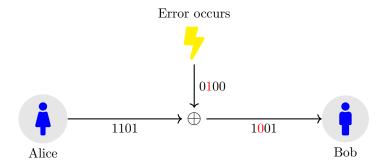

If we consider fig 3.2 we see that an error occurred under transmission. This low weight error changed the message, and Bob cannot determine what the original message was.

Figure 3.1: Error occurs during transmission.

If now Alice uses a linear code to encode the message as in figure 3.2, Bob will be able to detect that an error occurred during transmission. Because this invalid message has a determinable distance to a valid codeword, it can be corrected.

Figure 3.2: Error is detected and corrected.

# **Definition 9.** Hamming weight $h_{wt}(v)$

The number of non zero elements in a binary vector  $GF(2)^n$ . Ex  $h_{wt}(v) = h_{wt}([1,1,0]) = 2$

#### **Definition 10.** Hamming distance $h_d(u, v) = h_{wt}(u - v)$ for any $u, v \in GF(2)^n$ $Ex \ u = [1, 1, 0], v = [1, 0, 1] \to h_d(u, v) = h_{wt}(0, 1, 1) = 2$

So by using linear codes, we cannot only detect errors in messages but also correct them. To identify the closest codewords uniquely, we need to define our code so that the distance between valid codewords is the same and an odd number. Any invalid codeword can be uniquely decoded into a valid one. This distance between valid codewords is called *minimum Hamming distance*.

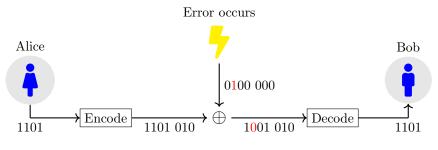

To understand the interaction between minimum Hamming distance and correctable errors, consider Figure 3.3. We can see the entire space a code C exists on, where the codewords are evenly spaced out. Each valid codeword has its *hamming bound* drawn around it, which here is a circle of radius (d-1)/2 = 1. The bound indicates that every invalid codeword within the bound is uniquely decoded to the valid codeword it belongs to. A code where the bounds cover the entire space (as seen in the Figure) is a *perfect code*.

Figure 3.3: Hamming bounds around valid codewords (red) in a perfect code with d=3

**Definition 11.** C is a q-ary linear [n, k, d] code if

- 1. C is a subspace of  $GF(q)^n$

- 2. C has dimension k

- 3. C has minimum Hamming distance d

### 3.2 Generator Matrix

We have talked about a mapping  $G: M \to C$  that can be expressed as a matrix G'. This matrix G' is called the *Generator matrix* for C and the structure of G' is so that the rows of G' form a basis for C.

**Definition 12.** Let C be a (n, k) linear code over  $F_q$ . If a matrix G's rowspace equals C then G is the generator matrix for C.

# 3.3 Parity Check Matrix and Syndromes

A parity check matrix H is defined as the matrix that has the relation  $H\mathbf{c}^T = \mathbf{0}$ for any  $\mathbf{c} \in C$ . **Definition 13.** Let C be an (n,k) linear code over  $F_q$ . Then a matrix H for which  $H\mathbf{c}^T = \mathbf{0}$  iff  $\mathbf{c} \in C$

The parity check matrix is particularly useful because by definition it will essentially negate the any valid codeword when multiplied. If we have a valid codeword  $c \in C$ , and an error is introduced to the vector y = c + e, then the syndrome s = Hy will only be a product of e as s = Hc + He = 0 + He

The syndrome is, as the word implies, a symptom of an underlying problem and it can tell us where the error is located in  $\mathbf{y}$ .

#### 3.4 Encoding

Encoding using a Linear code is very fast. If we have a (n, k) linear code C over  $F_2$  with generator matrix G, we select a message from  $\mathbf{m} \in F_2^k$  and encode it to  $\mathbf{x} \in F_2^n$  by  $\mathbf{m}G = \mathbf{x}$ .

This is a linear operation and can be implemented very effectively.

### 3.5 Decoding

Decoding a word r = c + e where  $c \in C$  and e is some error, is to find the closest codeword to  $r \to c$  or to find the error e.

**Definition 14.** The general decoding problem let C be a linear code and r be a received word on the form

r = c + e

Where  $c \in C$  and e is a random low weight vector. The Decoding Problem is to find m or e given r and C, and is split into two problems.

**Definition 15.** Decoding problem 1 - Syndrome decoding let C be a (n, k) linear code with parity check matrix H. Given a syndrome s = He, determine e of weight t such that

He = s

**Definition 16.** Decoding problem 2 - Codeword finding let C be a (n, k) linear code with parity check matrix H. determine c of a given weight t such that

$Hc = \mathbf{0}$

In some cases, the error vector will have a predetermined weight that will allow unique decoding. As long as the code has minimum hamming distance d, unique decoding will be possible with  $h_{wt}(e) <= \lceil \frac{d-1}{2} \rceil$ . This is called halfdistance decoding, and most decoding algorithms target this type of decoding.

If e can also be  $\lceil \frac{d-1}{2} \rceil < h_{wt}(e) \leq d$ , then decoding is still possible, but decoding will not have a unique answer. There might be several codewords with the same minimum distance from r therefore decoding might produce a list of closest codewords and different solutions for r = c + e. This is called

full-distance decoding and requires list decoding algorithms that will produce a list of solutions. This also makes consideration of which error weight to be prioritized. There might be different solutions with different error weights, and it is not obvious which one is the correct weight.

Decoding algorithms depend on what code one is using. The simplest way of decoding is to create a syndrome using the parity check matrix of the code. By adding an error to a code C, one will create a new code C' in which all the elements  $c' \in C'$  will have the same syndrome. If the code is sufficiently small, one can enumerate all these sets and find which set r belongs. The lowest weight vector, coset leader, in this set will be the error e.

Coset decoding is impossible to perform if the code grows too large to feasibly enumerate all the cosets, and this is why there are decoding algorithms tailored for each class of code.

The general decoding problem does not require a decoding algorithm. It is possible to decode any word r = c + e, as an attacker will have access to the generator matrix <sup>1</sup>, and because the rows of this matrix form a basis for Cthey have access to the entire code. It is then possible for the attacker to solve r = c + e by at least enumerating  $c \in C$ . The general decoding problem has proved to be computationally hard, and is classified as NP-complete [13].

#### 3.6 Hamming Codes

Hamming codes are an easy-to-understand subset of linear codes. They are constructed by adding parity check bits to create a codeword. These parity check bits will be a function of the message bits.

They are parameterized with [n, k, d]. Hamming codes are perfect codes as long as  $n = 2^r - 1$  and k = n - r for  $r \in \mathbb{Z}$  and r > 2 and d = 3.

To construct a [7, 4, 3] hamming code, one only needs to decide three parity check bits x, y, z to append to the message bits  $m_1$ -.

$$x = a + b + d$$

$$y = a + c + d$$

$$z = b + c + d$$

Where all arithmetic is done in  $\mathbb{Z}_2$ . We can then construct the generator matrix for the code:

$$G = \begin{bmatrix} 1 & 0 & 0 & 0 & 1 & 1 & 0 \\ 0 & 1 & 0 & 0 & 1 & 0 & 1 \\ 0 & 0 & 1 & 0 & 0 & 1 & 1 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 \end{bmatrix}$$

Because the generator matrix is already in the form:  $G = [I_k \mid T_{n-k \times k}]$  we can easily construct the parity check matrix by  $H = [-T^t \mid I_{n-k}]$ .

<sup>&</sup>lt;sup>1</sup>An attacker might have access to a scrambled version of the generator matrix, but they will be able to construct an equivalent code through linear algebra.

|     | [1 | 1 | 0 | 1 | 1 | 0 | 0 |  |

|-----|----|---|---|---|---|---|---|--|

| H = | 1  | 0 | 1 | 1 | 0 | 1 | 0 |  |

| H = | 0  | 1 | 1 | 1 | 0 | 0 | 1 |  |

Now every vector in  $m \in \mathbb{Z}_2^4$  encoded with G by y = mG + e with e being a random error of weight 1, will be uniquely identifiable by the syndrome s = Hy. If s is non zero, this means that e is non zero and because e can only be of weight 1, and that mG cancels out by H; then the syndrome is only a function of the column in which the error occurred.

So to decode a hamming code, one can simply determine the syndrome which will be the same as a column in H, and the index of this column will be the location of the error in y. This only works because the syndrome is a function of only one error, and if there were multiple errors; then the syndrome would be some linear combination of multiple columns, which is harder to determine.

### 3.7 Cyclic Codes

**Definition 17.** A cyclic code is a linear code C where any circular shift of a codeword  $c \in C$  is also in c.

Cyclic codes are constructed using polynomial rings  $\mathcal{R} = \mathbb{F}_2[X]/(X^r - 1)$ . The generator matrix is then uniquely defined by the first row:

$$r_1 = p_0 + p_1 x + \dots + p_r x^{r-1}$$

The second row:

$$r_2 = xr_1 \mod X^r - 1$$

$r_2 = x^2 r_1 \mod X^r - 1$

The third row:

and so on.

#### 3.7.1 Parameters

A cyclic code has codelength n, dimension k, and row density w, where typically  $w = O(\sqrt{n})$ .

#### 3.7.2 Decoding Cyclic Codes

Cyclic codes are often decoded using probabilistic algorithms and must be adjusted to have an acceptable decoding failure rate (DFR). DFR is the rate at which decoding either fails.

#### **Bit Flipping**

Gallager's bit flipping [14] is a probabilistic decoding algorithm that allows correction of  $\mathcal{O}(\sqrt{n})$  errors with high probability.

Because cyclic codes are sparse, it is possible given a syndrome s = He to check the probability that every position of e is in error.

Bit flipping is sequentially guessing that  $e_i = 1$  based on the  $P_r[e_i = 1 | s]$  which can be calculated.

Input parity check matrix H, ciphertext c Maximal iterations X, Maximal syndrome weight u

Output error vector e

1.  $s \to Hc$ 2. for i in 0...X: (a) th = computeThreshold(s, e)(b) for j in 0...n - 1: i.  $unsatifiedParityChecks = H_i \cdot s$ ii. if  $unsatifiedParityChecks > th \ e[j] = e[j] \oplus 1$ (c) s = H(c + e)3. output e if  $h_{wt}(s) = u$  else  $\perp$

Figure 3.4: Bit flipping algorithm in [15]

# 3.8 Binary Goppa Codes

A (n, m, t) Goppa code C is a linear code of length n that correct t errors and m is the size of the finite field used. C is uniquely defined by a irreducible polynomial g(x).

#### 3.8.1 Parameters and Setup

To construct a Goppa code n, m and t are selected for desired error correcting capability t. When the parameters are chosen, the code is constructed by selecting a random list L of n elements in  $GF(2^m)$  called the *Support*, and a random monic polynomial  $g(x) \in GF(2^m)[X]$  of degree t for which g(L) = 0 called the *Goppa Polynomial*.

#### Support

The support is a set of n elements from the finite field  $GF(2^m)$ . This field is usually constructed with an irreducible polynomial h of degree m and all field arithmetic is done in the extension field GF(2)/h. The support L is then nrandom elements in this field.

$L = [\alpha_0, \alpha_1, \cdots, \alpha_{n-1}]$

Generating the support is done:

#### Goppa Polynomial

A Goppa polynomial g is a monic polynomial of degree t and coefficients in  $GF(2^m)$ , with the added requirement that  $g(\alpha_i) \neq 0$  for  $i \in [0, \dots, n-1]$ . This can be achieved by selecting an irreducible polynomial, or a square-free polynomial.

#### 3.8.2 Decoding Goppa Codes

There are two common algorithms for decoding Goppa Codes; Patterson [16] and Berlekamp-Massey [13].

|     | $\left[\frac{1}{g(\alpha_0)}\right]$                            | $\frac{1}{g(\alpha_1)}$              |   | $\frac{1}{g(\alpha_{n-1})}$                          |

|-----|-----------------------------------------------------------------|--------------------------------------|---|------------------------------------------------------|

|     | $\frac{\alpha_0^1}{g(\alpha_0)}$                                | $\frac{\alpha_1^1}{g(\alpha_1)}$     |   | $\frac{\alpha_{n-1}^1}{g(\alpha_{n-1})}$             |

| H = | :                                                               | :                                    | · | :                                                    |

|     | $\left\lfloor \frac{\alpha_0^{t-1}}{g(\alpha_0)} \right\rfloor$ | $\frac{\alpha_1^{t-1}}{g(\alpha_1)}$ |   | $\frac{\alpha_{n-1}^{t-1}}{g(\alpha_{n-1})} \right]$ |

Figure 3.5: Parity Check matrix for A Goppa Code

The main idea of decoding a received word encoded with a Goppa code is finding an error locator polynomial  $\sigma$  that will have roots in L. When  $\sigma$  is found L is evaluated such that  $\sigma(\alpha_i) = 0$  indicates a 1 in the error vector e.

#### Patterson's Algorithm

The algorithm is outlined in Figure 3.6. Step a) can be done with Euclid's Algorithm, which will have a variable runtime. It is unknown if Patterson's can be completed in constant time, and there are timing attacks that have been shown to exist in [17]. This makes Patterson unsuitable for cryptographic purposes without mitigation.

- 1. Compute syndrome  $s(z) = \sum_{i=1}^{n} \frac{r_i}{z \alpha_i}$ 2. Determine error locator polynomial  $\sigma(z)$  by:

- (a) Determine h(z) such that  $s(z)h(z) = 1 \mod g(z)$ . if h(z) = z let  $\sigma(z) = z$

- (b) Calculate d(z) such that  $d^2(z) \equiv h(z) + z \mod g(z)$

- (c) Find a(z) and b(z) with b(z) of least degree, such that  $d(z)b(z) \equiv a(z)$  $\mod g(z)$

- (d) Put  $\sigma(z) = a^2(z) + b^2(z)z$

- 3. Determine the set of  $\alpha_i$  such that  $\sigma(\alpha_i) = 0$

- 4. The error positions are then found by the corresponding indices i.

Received word is z, q(z) is the Goppa Polynomial, and the set of  $\{\alpha_i\}$  is the Goppa support.

Figure 3.6: Parrerson Decoding algorithm with a Goppa Code

#### Berlekamp-Massey

Berlekamp-Massey (BM) [13] is a decoding algorithm that allows decoding of t/2 errors under a Goppa code. In order to find all errors a trick was proposed in [18] where the syndrome is doubled and arithmetic is done under the Goppa polynomial  $g(x)^2$ .

BM initializes the error locator polynomial  $\sigma(x), \beta(x) \in GF(2^m)[x]$  and integers  $l, \delta \in GF(2^m)$ . It then incrementally updates these values for 2t iterations and leaves  $\sigma(x)$  as the true error locator polynomial.

**Input**: t, syndrome S(x) **Output**: Error locator polynomial  $\sigma(x)$ 1. Initialize  $\sigma(x) = 1, \beta(x) = x, l = 0, \delta = 1$ 2. for  $k \in [0, 2t - 1]$ 3.  $d = \sum_{i=0}^{t} \sigma_i S_{k-i}$ 4. **if** d = 0 or k < 2t: 5.  $[\sigma(x), \beta(x), l, \delta] = [\sigma(x) - d\delta^{-1}\beta(x), x\beta(x), l, \delta]$ 6. **else**: 7.  $[\sigma(x), \beta(x), l, \delta] = [\sigma(x) - d\delta^{-1}\beta(x), x\sigma(x), k - l + 1, d]$ 8. **return**  $\sigma(x)$

Figure 3.7: Berlekamp-Massey algorithm in pseudo code

### **3.8.3** Beyond t

If a linear code C has error correction capability t, it is possible to introduce additional errors to break the uniqueness of decoding. As mentioned in Section 3.5 this requires list decoding and also has the benefit of making attacks more complicated [19].

A list decoding algorithm for binary goppa codes is outlined in [20] which can decode approximately  $n - \sqrt{n(n-2t-2)}$  errors.

# McEliece

McEliece is a code based Public Key Encryption scheme (PKE), and was introduced by Robert McEliece in 1978 [4]. In a general McEliec scheme the compents are:

- C: A linear code with generator matrix  $\hat{G}$ , parity-check matrix H and a chosen error-correction capability t.

- S: A non-singular matrix to provide diffusion.

- P: A permutation matrix to provide confusion.

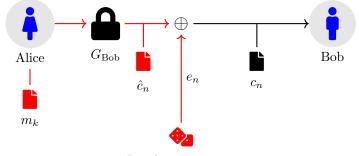

The public key is constructed  $G = S\hat{G}P$ , and data is encrypted by  $c = mP_k + e$  where e is a vector of hamming weight t (see Figure 4.2).

The Secret/Private key consists of S, P and a decoding algorithm  $\mathcal{D}$ , and the *c* is decoded using  $S^{-1}$ ,  $P^{-1}$  and  $\mathcal{D}$ . What is important to notice that decryption is more complicated than encryption, and some decoding algorithms cannot be implemented in constant time.

Random generator

Figure 4.1: Encryption in a standard McEliece Cryptosystem.

### 4.1 Niederreiter

Now that we have all the building blocks defined, we are ready to look at the Niederreiter variation of McEliece. Niederreiter is a dual variation of McEliece and was proposed by Harald Niederreiter in 1986 [21]. In the system, one uses the parity check matrix for encryption, essentially going backward.

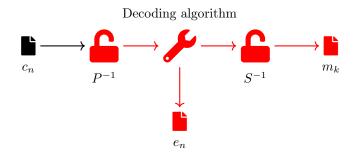

Figure 4.2: Decryption in a standard McEliece Cryptosystem.

| Codelength                    | Codelength $n$ , Dimension $k$ and $t$ correctable errors                   |  |  |

|-------------------------------|-----------------------------------------------------------------------------|--|--|

| $\hat{G}_{k \times n}$ - Gene | erator matrix for random linear code $C$                                    |  |  |

| $S_{k \times k}$ - Non :      | singular matrix                                                             |  |  |

| $P_{n \times n}$ - Perm       | utation matrix                                                              |  |  |

| Key                           | $S_k$ $P_k$                                                                 |  |  |

|                               | $(S, \hat{G}, P) \qquad \qquad G_{k \times n} = SGP$                        |  |  |

| Encryption                    | $h_{wt}(e) = t$                                                             |  |  |

|                               | $\mathcal{E}(e) = mG + e = c$                                               |  |  |

| Decryption                    | $\hat{c} = cP^{-1} = mSG + eP^{-1}$                                         |  |  |

|                               | $ \begin{array}{c} \mathcal{D}(\hat{c}) \to mS\\ m = mSS^{-1} \end{array} $ |  |  |

|                               | $m = mSS^{-1}$                                                              |  |  |

Table 4.1: Standard McEliece Cryptosystem

It is possible to construct a Niederreiter system from any linear code, but many systems using codes that allow smaller key sizes have been found to be insecure.

The most confidence-inspiring code is still the same as the original proposal [4] which uses binary Goppa codes.

| Codelength                    | Codelength $n$ , Dimension $k$ and $t$ correctable errors                             |  |  |

|-------------------------------|---------------------------------------------------------------------------------------|--|--|

| $\hat{H}_{(n-k)\times n}$ - 1 | Parity check matrix for random linear code $C$                                        |  |  |

| $S_{(n-k)\times(n-k)}$        | ) - Non singular matrix                                                               |  |  |

| $P_{n \times n}$ - Perm       | nutation matrix                                                                       |  |  |

| Key                           | $S_k$ $P_k$                                                                           |  |  |

|                               | $(S, \hat{H}, P) \qquad \qquad H_{k \times n} = S\hat{H}P$                            |  |  |

| Encryption                    | Encode $m$ as $e, h_{wt}(e) = t$                                                      |  |  |

|                               | c = He                                                                                |  |  |

| Decryption                    | $\hat{c} = S^{-1}c = \hat{H}Pe$                                                       |  |  |

|                               | $\begin{aligned} \text{Decode}(\hat{c}) &\to Pe \\ e &= P^{-1}Pe \to m \end{aligned}$ |  |  |

|                               | $e = P^{-1}Pe \to m$                                                                  |  |  |

Table 4.2: Niederreiter Cryptosystem

### 4.1.1 Keysizes

Key sizes using Goppa codes are relatively large in the PQC landscape. From table 4.3 we see that even when limiting the analysis to only code-based systems, Goppa codes are orders of magnitude larger than the others.

| Code    | Implementation | Security level | Size      | %    |

|---------|----------------|----------------|-----------|------|

| Goppa   | CM [22]        | 266            | 1022  kB  | 100% |

| HQC     | HQC [7]        | 256            | 7.245  kB | 0.7% |

| QC-MDPC | BIKE [6]       | 256            | 5.121  kB | 0.5% |

Table 4.3: McEliece Systems with different codes

### 4.1.2 Reduction in Message Space

Using the Niederreiter scheme, one has to encode the message to a binary vector of length n and weight t. This means that not the entire code can be used.

In the regular setup, the dimension would be k, which would allow the encryption of  $2^k$  distinct messages.

By representing the message as an error, the maximal possible messages are instead the number of vectors of length n and weight t. So for a (n, m, t) code C, if used in a Niederreiter scheme:

$$|C_{\text{Niederreiter}}| = \binom{n}{t}$$

And we can find the message bits of our code by  $\log_2(|C_{\text{Niederreiter}}|)$ . The parameter choices for [3] are listed and compared in Table 4.4

| Parameters  | McEliece     | Niederreiter |

|-------------|--------------|--------------|

| n/m/t       | message bits | message bits |

| 3488/12/64  | 2720         | 456          |

| 4608/13/96  | 3360         | 668          |

| 6688/13/128 | 5024         | 908          |

| 6960/13/119 | 5413         | 863          |

| 8192/13/128 | 6528         | 946          |

Table 4.4: Maximum message bits for a McEliece scheme with CM parameters

## Programmable Logic

We often encounter problems where computational time is a bottleneck. Modern CPUs are highly versatile but often unsuitable for solving specific problems in real-time on low-cost hardware. To address this issue, it is common to design specialized hardware that drastically reduces the time needed for computation.

Examples of problems like these are decoding Reed-Solomon codes in CD players [23], [24], or image recognition in demanding areas [25]. Without specialized hardware to perform computations; it would be impossible to have these technologies working in real-time.

It is assumed that the reader has some knowledge about programming and software implementations, and in this chapter, the basic outlines of hardware development will be outlined.

To test hardware components, it is vital to have platforms that allow us to change the designs without creating the circuits physically. Devices that allow the user to configure the physical layout of the chip are called programmable logic (pl) devices. There are many types of pl devices and some will allow the user to reconfigure the device any number of times.

### 5.1 FPGA

A field programmable gate array (FPGA) is an integrated circuit that can be programmed to replicate a hardware design. An FPGA is one of many programmable logic devices, but for this text, we will use FPGAs and programmable logic interchangeably.

The basic idea is that a FPGA is a chip with a set number of IO ports. Within the chip is a large number of LUTs that can be configured and routed arbitrarily to produce any desired behavior of the IO ports. What is so remarkable about this is that this can be done within a single clock cycle, and the programmer is only limited to how fast the actual electrical signal can propagate through the inner circuits. This is a common problem in hardware development and more complex logic will result in a longer path for the signal to travel, and thus the clock speed might suffer to make sure the signal has time to propagate.

### 5.1.1 Hardware Description Language

There are two primary language's that are used for FPGA development; Verilog and VHDL. These languages are called hardware description languages (HDLs) and are similar to programming languages but function quite differently.

Verilog, or SystemVerilog, is standardized as IEEE 1800 [26]. At the time of writing, there are about 8 thousand repositories on GitHub that contains Verilog or SystemVerilog.

VHDL, or Very High-Speed Integrated Circuit Hardware Description Language, was developed in 1983, and the latest version is standardized as IEEE 1076-2008 [27]. At the time of writing, there are about 450 repositories that contain VHDL.

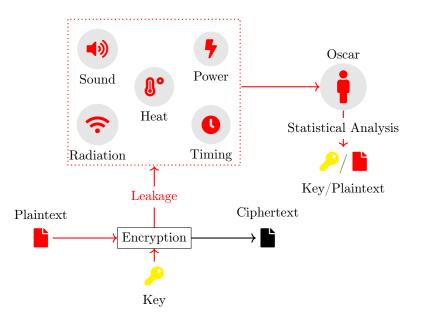

As Norwegian businesses more widely use VHDL, it is the target language of this work.