## High-speed Sampler for CMOS LIDAR

**Emil Ulvestad**

Thesis submitted for the degree of Master in Electronics and Computer Science, Microelectronics 60 credits

Department of Physics

Faculty of mathematics and natural sciences

**UNIVERSITY OF OSLO**

Autumn 2018

## **High-speed Sampler for CMOS LIDAR**

**Emil Ulvestad**

© 2018 Emil Ulvestad

High-speed Sampler for CMOS LIDAR

http://www.duo.uio.no/

Printed: Reprosentralen, University of Oslo

#### **Preface**

This Master's thesis was submitted for the degree of M. Sc. at the University of Oslo, dept. of Informatics. The work has been carried out in the period between spring 2017 and fall 2018 at the NANO group under the supervision of Professor Tor Sverre Lande, Ph. D. Kristian G. Kjelgård and Professor Dag T. Wisland.

Oslo, August 15, 2018

**Emil Ulvestad**

#### Acknowledgement

First and foremost, I would like to express my sincere gratitude to my supervisors, Tor Sverre Lande, Kristian G. Kjelgård and Dag T. Wisland. Your continuous guidance and scientific insights during our countless discussions have been invaluable. You have shown great enthusiasm and patience in my work, which has allowed me to develop both my knowledge and confidence.

I would also like to thank Øystein Bjørndal for your undisputed expertise in Cadence, Mathias Tømmer for your assistance in making the Beaglebone Black behave and Olav Kyrvestad for your practical assistance during tape-out and PCB production. A special thanks go to my partner in crime, Tohid Moradi Khanshan, for sharing the chip area with me and keeping me company during the long days in the lab.

I am also very grateful for the support that my friends and family have shown. Last but not least, I would like to thank my girlfriend, Vibeke, for always having faith in me and supporting and fuelling my ambitions without questions.

E.U.

#### **Abstract**

In this thesis, a high-speed sampling system intended for use in a depth selective spectroscopic LIDAR for transcutaneous blood assessment is proposed. The system is fundamentally based on a continuous-time sampling solution, enabling sampling rates close to 100GS/s, close to two orders of magnitude faster than standard clocked systems. Oversampling makes the system capable of capturing inherently weak and noisy high-frequency signals. Based on experimental verification in 90nm CMOS technology, the opportunities and limitations of continuous-time sampling systems are analyzed.

## **Contents**

|   |      | ace                                               |     |

|---|------|---------------------------------------------------|-----|

|   |      | nowledgement                                      |     |

|   | Abst | tract                                             | III |

| 1 | Intr | roduction                                         | 1   |

| 2 | Bac  | kground                                           | 4   |

| _ |      | 1-bit signal processing                           | 4   |

|   | 2.2  | CTBV Signal Processing                            | 5   |

|   | 2.3  | Signal averaging                                  | 6   |

|   | 2.4  | Swept Threshold Sampling                          | 8   |

|   | 2.5  | System architecture                               | 10  |

|   | 2.6  | •                                                 | 14  |

|   | 2.0  | 2.6.1 Process variation                           | 14  |

|   |      | 2.6.2 Mismatch in the delay lines                 | 16  |

|   |      | 2.6.3 Summary                                     |     |

|   | 2.7  | Environmental Variations                          |     |

|   | 2.1  | Environmental variations                          | 10  |

| 3 |      | lementation                                       | 20  |

|   | 3.1  | Sampling System                                   | 20  |

|   | 3.2  | Delay lines                                       | 21  |

|   |      | 3.2.1 Delay Element                               | 21  |

|   |      | 3.2.2 Initial delays                              |     |

|   | 3.3  | Samplers                                          |     |

|   |      | 3.3.1 Timing considerations & metastability       | 29  |

|   |      | Counters                                          | 30  |

|   | 3.5  | Input/Output                                      | 30  |

|   |      | 3.5.1 SPI module                                  | 30  |

|   |      | 3.5.2 Shiftregisters                              | 31  |

|   | 3.6  | Misc. supporting circuitry                        | 31  |

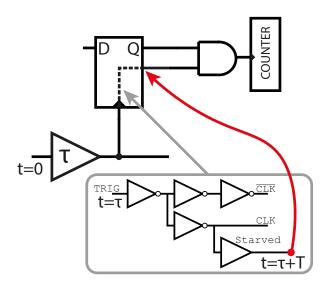

|   |      | 3.6.1 Delay element with current starved inverter | 31  |

|   |      | 3.6.2 Programmable delay element                  | 32  |

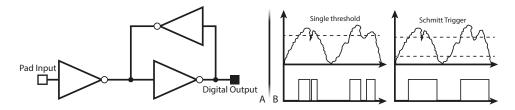

|   |      | 3.6.3 Schmitt Triggers                            | 32  |

|   |      | 3.6.4 Fan-out buffering                           | 33  |

|   | 3.7  | Complete system schematics                        | 33  |

|   | 3.8  | Power Supply                                      | 34  |

|   |      | 3.8.1 Decoupling                                  | 34  |

| 4 | Mea  | asurements & Characterization                     | 35  |

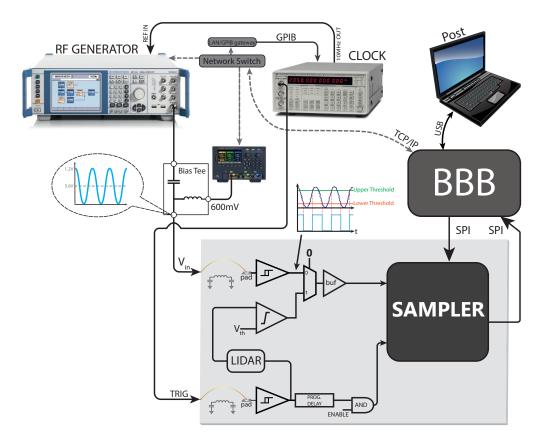

| - | 4.1  | Measurement setup                                 | 35  |

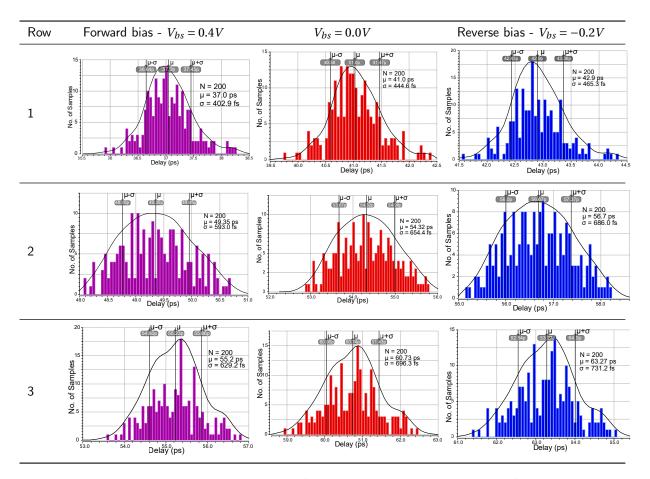

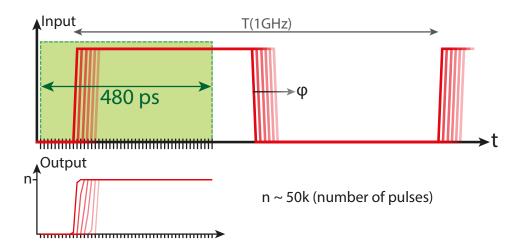

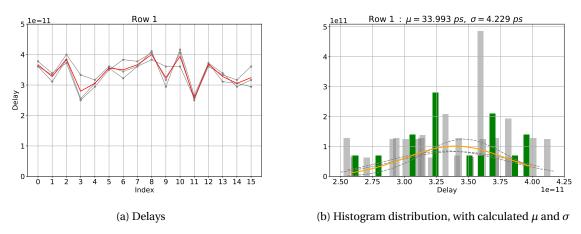

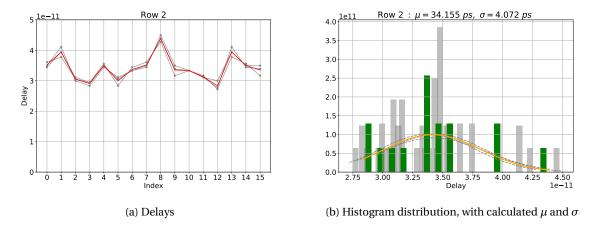

|   | 4.2  | Characterization of the delay lines               | 36  |

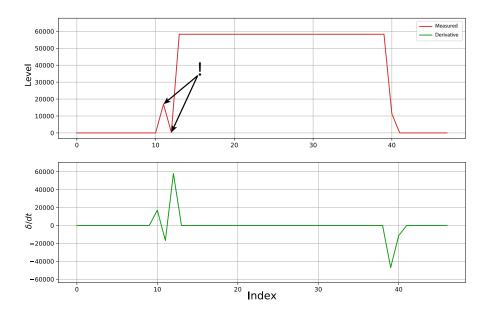

|   | 4.3  | Sequentiality                                     | 38  |

|   | 4.4  | Characterization of the interleaved system        | 40  |

|   |      | Power                                             | 41  |

|   |      |                                                   | 11  |

| 5 | Disc | cussion and Further Work                          | 42  |

| 6 | Con  | clusions                                          | 45  |

| CONTENTS | V |

|----------|---|

|          |   |

| A  | Acronyms                         | 46 |

|----|----------------------------------|----|

| В  | Paper (unpublished)              | 48 |

| C  | Raw data output from phase sweep | 54 |

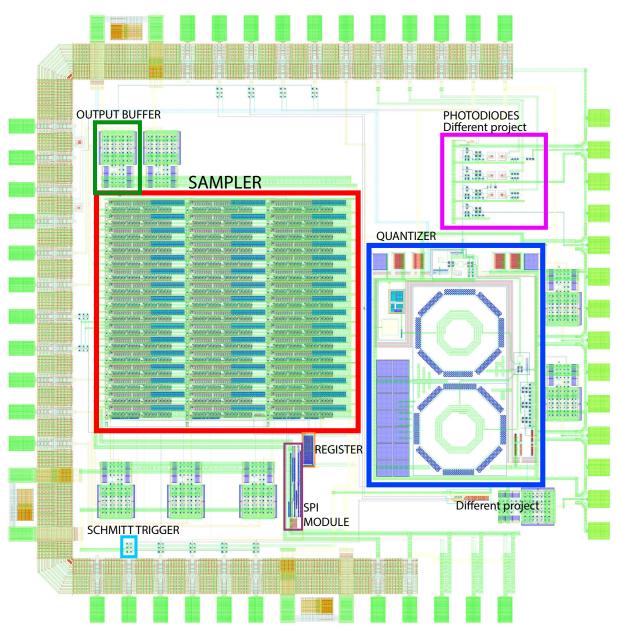

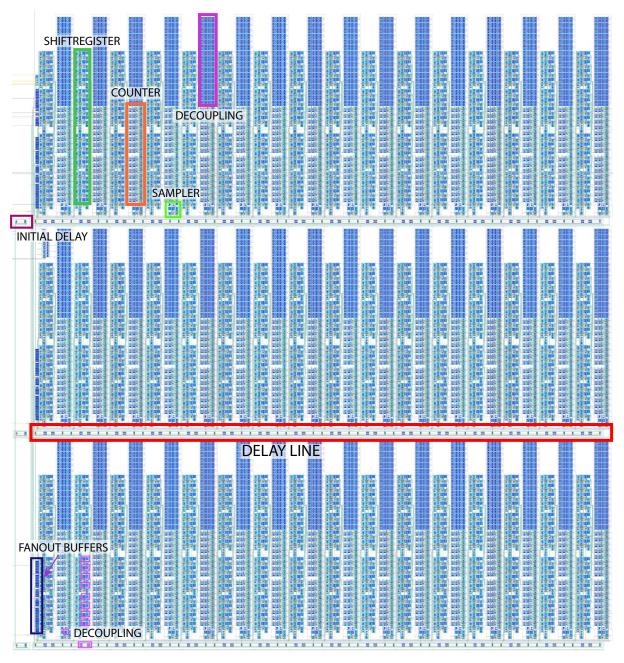

| D  | Layout                           | 55 |

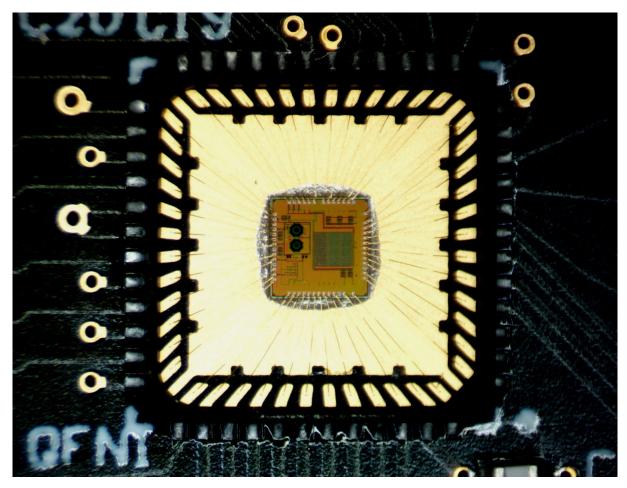

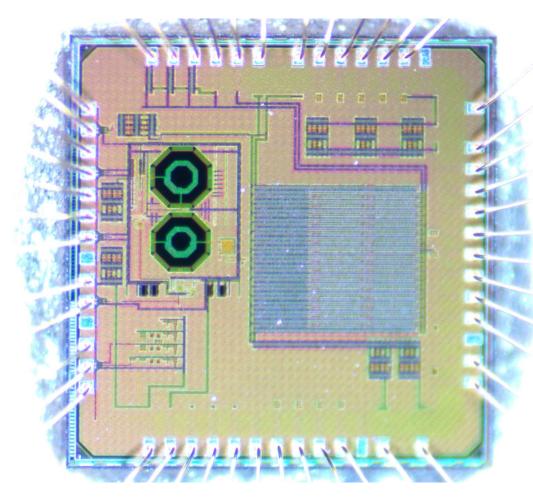

| Е  | Microscope photographies         | 57 |

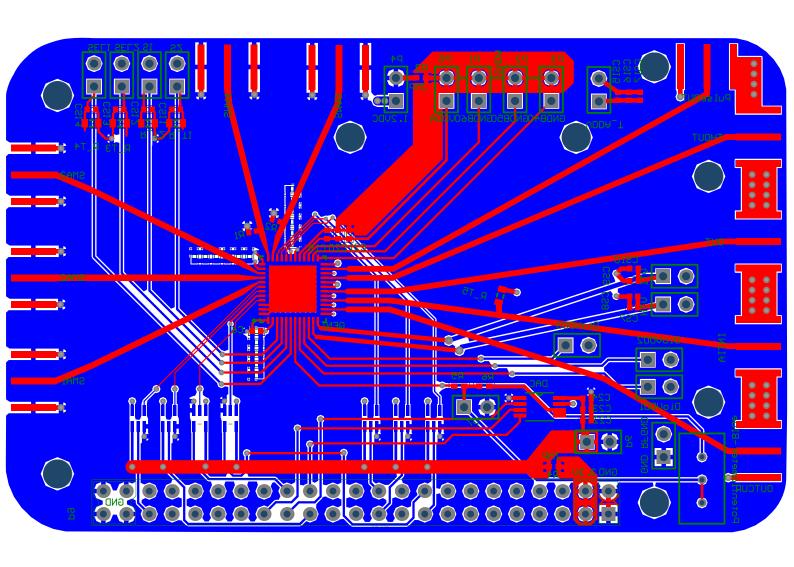

| F  | PCB                              | 59 |

| Bi | bliography                       | 61 |

# **List of Figures**

| 1.1  | Transcutaneous sensing with ToF                                         | 2  |

|------|-------------------------------------------------------------------------|----|

| 2.1  | Quantization error                                                      | 6  |

| 2.2  | Signal averaging example                                                | 8  |

| 2.3  | Swept threshold principle                                               | 8  |

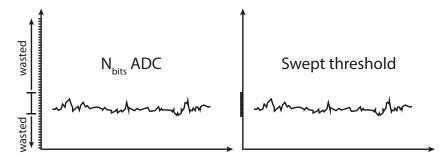

| 2.4  | Multi-bit ADC vs. swept threshold                                       | 9  |

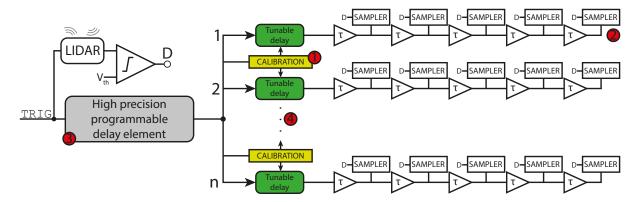

| 2.5  | System architecture                                                     | 11 |

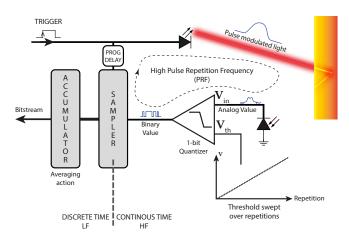

| 2.6  | Conceptual block diagram of swept threshold sampler                     | 12 |

| 2.7  | Delay line interleaving                                                 | 13 |

| 2.8  | Process variations                                                      | 14 |

| 2.9  | Effect of mismatch on critical path delay                               | 17 |

| 2.10 | Mismatch-caused accumulated deterioration of delay lines                | 18 |

|      |                                                                         |    |

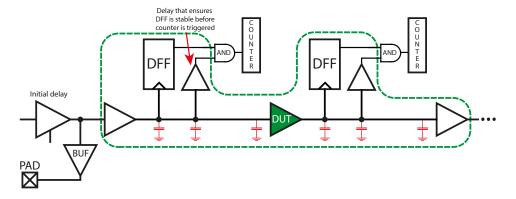

| 3.1  | Sampler block diagram                                                   | 20 |

| 3.2  | Illustration of accuracy vs. precision                                  | 21 |

| 3.3  | Delay element: Unbalanced inverters                                     | 22 |

| 3.4  | Various design techniques to maximize the speed of transistors          | 23 |

| 3.5  | Illustration: RC circuit                                                | 24 |

| 3.6  | Post layout simulation testbench for delay elements                     | 25 |

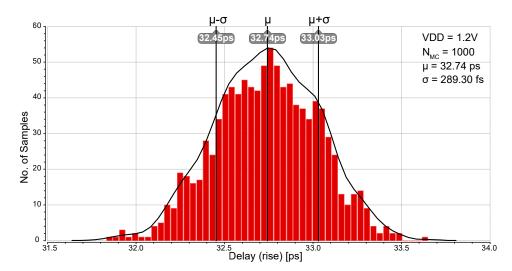

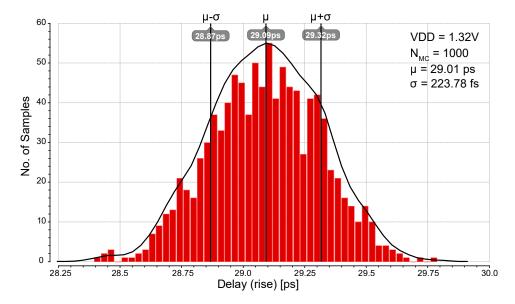

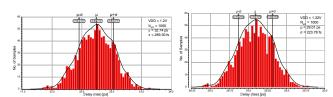

| 3.7  | Post-layout Monte Carlo simulation of delay element. VDD=1.2            | 25 |

| 3.8  | Post-layout Monte Carlo simulation of delay element. VDD=1.32           | 26 |

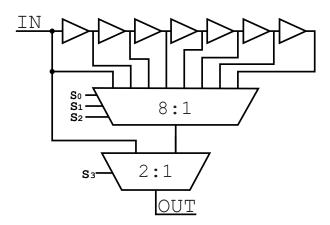

| 3.9  | Tunable initial delay                                                   | 27 |

| 3.10 | Post-layout Monte Carlo simulations of the initial delay elements       | 28 |

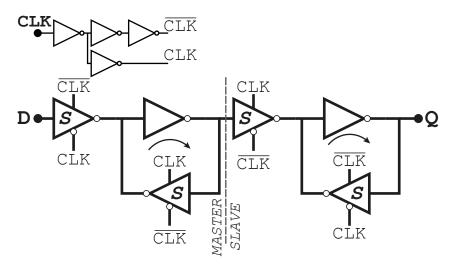

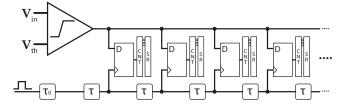

|      | Rising-edge triggered master-slave D flip-flop                          | 29 |

|      | Metastability                                                           | 30 |

|      | Schematic of asynchronous ripple counter                                | 30 |

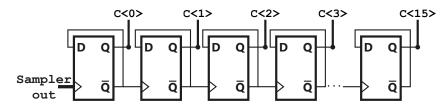

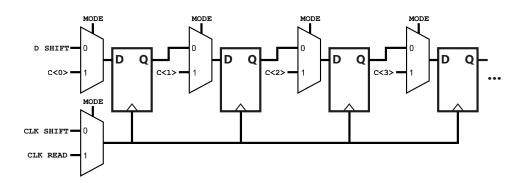

|      | Parallel-in/Serial-out Shift Register                                   | 31 |

|      | Delay element with starved inverter                                     | 32 |

|      | SPI-programmable delay element                                          | 32 |

|      | Schmitt Triggers                                                        | 33 |

|      | Fan-out Buffering                                                       | 33 |

|      | Sampler Line                                                            | 33 |

|      | Complete system block diagram                                           | 34 |

|      | On-chip decoupling strategies                                           | 34 |

|      |                                                                         |    |

| 4.1  | Measurement setup                                                       | 36 |

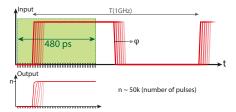

| 4.2  | Phase shifting principle                                                | 37 |

| 4.3  | Measurement results for delay line 1                                    | 37 |

|      | Measurement results for delay line 2                                    | 37 |

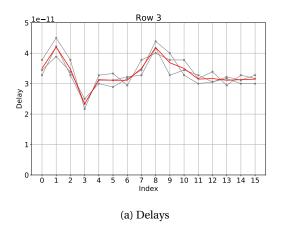

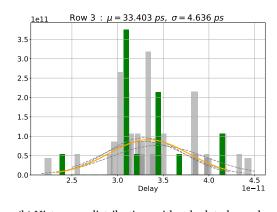

| 4.5  | Measurement results for delay line 3                                    | 38 |

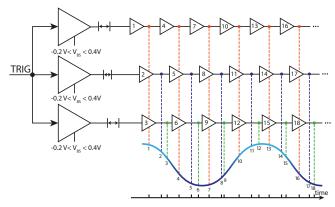

| 4.6  | Illustration of nonsequential sampling                                  | 39 |

| 4.7  | Nonsequential sampling                                                  | 39 |

| 4.8  | Back-gate compensation ensures sequential, but not equidistant sampling | 40 |

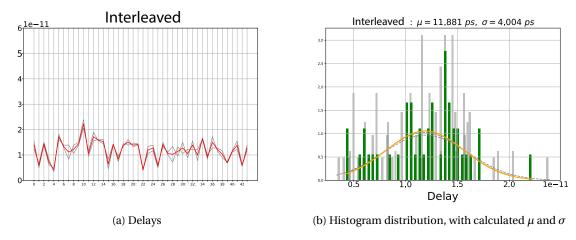

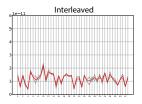

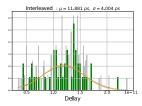

| 4.9  | Measurement results of the interleaved delay lines                      | 40 |

|      |                                                                         |    |

| 5.1  | Proposed reduction to unit delay load                                   | 43 |

| 5.2  | Proposed delay line topology with extended back-gate calibration        | 43 |

| LIST OF FIGURES | VII |

|-----------------|-----|

|                 |     |

| 5.3 | More topology improvements | 44 |

|-----|----------------------------|----|

| C.1 | Sampler Raw data           | 54 |

|     | Padframe                   |    |

|     | Package on PCB             |    |

## **List of Tables**

| 2.1 | Signal processing domains                | 5  |

|-----|------------------------------------------|----|

| 2.2 | Process and electronic parameters        | 16 |

| 0.1 |                                          |    |

| 3.1 | Unit delay element transistor dimensions | 24 |

| 3.2 | Initial delay dimensions 1               | 27 |

| 3.3 | Initial delay dimensions 2               | 27 |

| 3.4 | Extracted data from MC simulations       | 28 |

| 3.5 | SPI control bits                         | 31 |

### Chapter 1

### Introduction

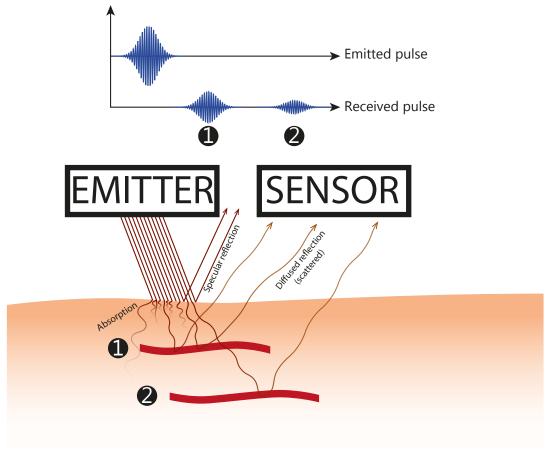

With the increasing portability and computational power of modern microelectronics, the interest towards development of new non-invasive biomarker sensing technology has increased significantly. Technology advances have enabled many wearable solutions providing long-term monitoring of cardiac, respiratory and metabolic diseases, like for example diabetes. However, most chemical monitoring techniques, e.g., blood glucose analysis for diabetes patients, remain subcutaneous<sup>1</sup>. In order to achieve entirely non-invasive detailed chemical assessments of biomarkers, *transcutaneous* sensing<sup>2</sup> is being explored as a potential solution. Pulse oximetry, in which near-infrared (NIR) light is passed through some thin part of the body and sensed by a photosensor on the opposite side, is a well established transmissive transcutaneous sensing technique used for measuring blood oxygen levels (hemoglobin saturation). However, oximeters do not provide sufficient accuracy for more specific monitoring of substances in the blood like glucose or carbon dioxide levels.

Spectroscopy is a well established scientific measurement technique for characterizing matter by analyzing its interaction with electromagnetic radiation (EMR). As EMR interacts with matter, it is either transmitted, absorbed, reflected, scattered or undergo photoluminescence<sup>3</sup>. Each atom and molecule render a unique response, and the resulting spectrum can be used to recognize the biochemical composition of the sample. As an example: Oxyhemoglobin (HbO2), which is a type of hemoglobin found in blood, show high levels of absorption of light between 300nm and 600nm. For the sake of simplicity, assume that no other substances in the sample share this characteristic. By emitting EMR in this spectrum, and studying the results, one can determine the levels of  $HbO_2$  in the sample by the degree of attenuation. Near-infrared (NIR) defines light ranging from 650nm to 1350nm in wavelength, and is where light has its highest depth of penetration in body tissue. However, with a predominant absorption of hemoglobin at wavelengths < 600 nm and water in the wavelength range >  $1\mu m$ , plus the fact that silicon substrate photosensors only show adequate sensitivity up to ~  $1\mu m$ biochemical characterization beyond a millimeter of tissue becomes impractical when outside the wavelength window of  $\sim 600 - 1 \mu m$  [1]. This window is often referred to as the therapeutic window. Although NIR light has high penetration in tissue, spectroscopy does not automatically become particularly accurate. Within the theurapeutic window the dominant light-tissue interaction is scattering, which causes rapid diffusion. The scattering increases the distance traveled by photons, which in turn leads to a higher probability of photon absorption. With the high degree of absorption in the body tissue, obtaining high sensitivity, i.e., signal-to-noise ratio (SNR), becomes a significant challenge in transcutaneous light sensing. Complex interactions between light and tissue further complicate the task of assigning specific properties to samples. As an example; when attempting blood glucose measurements, the weak NIR spectra from glucose is severely obscured behind the stronger overlapping spectra from water, hemoglobin, proteins, and fats in the human body. Estimating the glucose concentration from the scattered light, therefore, becomes challenging. With such broad and often overlapping bands, achieving high sensitivity in spectroscopy is not trivial.

Some advanced spectroscopic systems using optical techniques to provide depth profiling in semi-transparent materials have already been developed, as shown by Freebody et al. [2]. However, these systems are large, expensive and consist of complex optical solutions unsuitable for microelectronics. In addressing the challenges regarding selectivity, solutions in time-of-flight (ToF) measurements hold promising prospects when combined with microelectronics. With directed measurements of scattering at specific depths, the selectivity

<sup>&</sup>lt;sup>1</sup>Subcutaneous sensing: Sampling from tissue located under the skin.

<sup>&</sup>lt;sup>2</sup>Transcutaneous sensing: Sensing measured across the depth of the skin.

$<sup>^3</sup>$ Photoluminescence designates a number of effects, including fluorescence, phosphorescence, and Raman scattering.

may be significantly improved. A well-known ToF instrument is the radar. A simple radar solution is pulsed radar, which transmits a short radio pulse, at which point a high-speed a sampler is used to measure the ToF from the backscattered signal. This principle is also applied using light pulses for long-range sensing, conventionally named Light Detection and Ranging (LIDAR). Seeking existing solutions, we find many such light-based time-of-flight systems already integrated into CMOS technology, like the laser autofocus, found most high-end mobile cameras. However, such systems are either too large [3] or lack sufficient depth resolution [4].

Figure 1.1: ToF measurements will provide depth profiling which might increase selectivity in transcutaneous sensing.

The phrase "A chain is only as strong as its weakest link" is appropriate in describing how clock synchronized systems must limit their speed. The slowest logic stages in such a system will dictate the maximum clock frequency to avoid catastrophic race conditions which could lead to incorrect data or glitches. There will be uncertainty regarding arrival times of clocked signals, so special consideration must be made to meet the timing requirements with an acceptable margin. This limitation in speed restricts the depth selectivity when processing light signals. The diameter of a typical blood vessel in the underarm is in the order of 1mm. Sensing properties of the blood inside such a vessel will have to approach the same order of resolution. With light propagating through the body in the order of  $10^8 m/s$ , we find that a 1mm resolution will require a sampling rate of approximately 100GS/s ( $\frac{10^{-3}m}{10^8m/s}$ ). To this time, such high frequencies are considered unreachable in conventional microelectronics as most clock synchronized commercial systems have a peak clock frequency of no more than 5GHz. However, the continued development of microelectronics has brought with it significant improvements with regards to transistor sizes which has resulted in lower capacitances and faster digital gates. A typical gate-delay in nanometer technology is around 10ps and is still becoming faster with further advancements. These progressions have led to a new 1-bit signal processing domain; Continuous-Time Binary-Value (CTBV), which as a concept is based on the idea of substituting the clocked synchronization with delay-based timing. By removing their dependency on the clock, systems can operate in continuous time, with speeds limited by the inherent gate delay of the given technology.

The primary objective of this thesis is to explore how a high-speed signal acquisition system capable of reconstructing inherently weak and noisy high-frequency signals at an equivalent sampling rate approaching 100GS/s can be realized in standard CMOS technology. The architecture will be fundamentally based on CTBV signal processing. We will explore how CTBV allows us to regain the speed scaling provided by the technology, by utilizing the inherent gate-delay to design a temporally sequenced sampling system of interleaved delay lines. However, with great speed comes great responsibility. The stochastic process variations and temperature dependencies in CMOS introduce behavioral differences between devices which must be accounted for both before and during operation. We will rely on careful modeling and also explore back-gate tuning as a method of compensation during operation. However, the process variations are expected to become a limiting factor of the timing precision of signals and will add restrictions on both speed and depth of the system. In this thesis, we will be pushing the boundaries of the technology, and we hope through empirical, experimental verifications to reach definite conclusions regarding the potentials and limitations of continuous-time sampling and make way for future work.

### **Chapter 2**

### **Background**

In this chapter we will explore the theoretical foundation for realizing the sampling system, before presenting the proposed system architecture. Following comes a discussion on the challenges this introduces.

#### 2.1 1-bit signal processing

As the supply voltage and headroom of fine-pitch technologies decrease, implementing high-speed analog signal processing is becoming a significant challenge. The low power supply voltage prohibits any high performance integrated analog processing. 1-bit signal processing, on the other hand, has become a strong candidate, since it takes advantage of the many inherent properties of fine-pitch digital technologies; such as high speeds, simple design, low cost and a high degree of flexibility. Moving away from analog processing to multibit digital processing presents many potential benefits in itself, such as:

- Implementations of all-in-one packages on small Silicon die (SoC).

- · Allows for more advanced and flexible systems.

- Less deterioration during transmission and write/read. Data can be stored in memory and transferred without loss.

- More immune to noise, process- and environmental variations.

- There is also a potentially decreased power consumption since digital electronics have a much lower static power consumption compared to analog electronics.

- Operations can be parallelized.

Venturing from multi-bit to 1-bit signal processing there are additional benefits to be gained:

- 1-bit signal processing enables simpler, smaller designs, without the need for parallel data buses. With serial buses, timing skew in buses is no longer of any concern (allows for even higher speeds).

- Compared to multi-bit, 1-bit processing have potential for even lower power consumption.

- 1-bit AD/DA conversion will be much simpler and have a higher linearity than multi-bit converters. Multi-bit converters have many threshold levels and great care have to be made to ensure linear response. A 1-bit converter is either 0 or 1, so it can't have unevenly spaced levels.

- As highlighted in the next section, CTBV systems allow for high temporal resolution with the removal of the clock.

1-bit signal processing does, however, come with some limitations and potential drawbacks. The following points are considerations made from the perspective of our sampling system. Firstly, even though the system is not dependent on clocked synchronization, a clock will be required to trigger the sampling. Secondly, some form of oversampling or integrating action will be required to compensate for the inherently low dynamic range (DNR) and SNR of a 1-bit quantized system. As we will see in section 2.3 we achieve this through signal averaging, in which consecutive samples can be used to increase DNR and SNR. However, this oversampling

will come at the cost of increased processing time and can be power consumption. Thirdly, several "analog" operations, such as filtering and clipping are more challenging to achieve in 1-bit systems [5].

#### 2.2 CTBV Signal Processing

As mentioned in chapter 1 the sampler in this thesis is intended to perform readout in a pulsed LIDAR system, where it samples reflected EM pulses. A significant effort must, therefore, be placed in generating very high sampling rates to acquire the high-resolution sensing necessary to obtain a high degree of depth selectivity. The term *Continuous-Time Binary Value*, first coined by Hjortland and Lande [6], represents a unique hybrid signal-processing domain in which the signal is represented in binary, while time is kept continuous through the removal of a clock. By being clockless CTBV can offer the speed of conventional analog signal processing, while also supporting some of the advanced processing capabilities seen in digital signal processing (DSP) due to its binary value discretization. In the CTBV domain, a signal is expressed in a binary manner and is continuous in time. In contrast to clock synchronized digital logic, where transitions are dependent on the clock cycle, CTBV signals can transition at any point in time. This means that the signals are represented primarily by their transitions and pulse widths (similar to PWM¹), instead of the conventional representation of amplitude level at discrete steps.

|     |            | Time           |            |  |

|-----|------------|----------------|------------|--|

| 4)  |            | Discrete       | Continuous |  |

| Jue | Binary     | Digital        | CTBV       |  |

| Val | Continuous | Sampled analog | Analog     |  |

Table 2.1: Signal processing domains

In the CTBV domain, signals can be processed with a set of simple digital operations, which will be represented in short below.

- 1. Delay and pulse shaping: Delay elements can be constructed as two cascaded inverters. As the signal passes through a delay element, its transitions will be delayed by a predefined amount. If designed symmetrically the inverters will not significantly distort the pulse widths of the signal (some phase noise). However, asymmetric sizing can be applied intentionally to create a delay element which delays the rising or the falling edges of the signal significantly more than its counterpart. This allows us to adjust the widths of pulses easily.

- By cascading multiple delay elements, we create a *delay line*, which provides a sort of history of the input signal within a small time frame. The delay line operation is central to the design of the sampler and is addressed more in-depth in section 2.5.

- 2. *Sampling*: Simple 1-bit digital samplers can be used to sample CTBV signals at high speed. In this thesis, D flip-flops are used, in conjunction with delay lines, to perform the high-speed sampling, in which the D flip-flops' clock inputs are tapped from the different stages of the delay lines.

- 3. *Combinational logic*: Due to the binary quantization of CTBV, combinational logic operations (AND,OR,XOR, etc.) become trivial to implement. Such logic operations can, for example, be combined with delay elements for pattern detection, pulse width modulation, etc.

The simple architecture of CTBV signal processing circuits provides opportunities for designing highly area efficient systems. Also, with the exclusion of high power analog system components, and the fact that digital CMOS circuits primarily draw power during switching (dynamic power), CTBV presents unique opportunities for specialized low-power designs (which has become increasingly relevant in the recent decade). In the absence of the clock, many CTBV operations become limited mainly by the gate delays in the technology used - which in modern CMOS technologies can be as low as a few tens of picoseconds. A simple, yet clever technique to further increase speeds beyond the gate delays is easy to implement. The relative difference in delays

$<sup>^{1}</sup>$ In pulse-width modulation the amplitude(s) of a signal (usually analog) is encoded into the pulse width(s) of another signal (usually digital)

can be utilized to perform operations which will have a time resolution much smaller than the individual gate delays. This technique is of fundamental relevance in this sampler, but as we will address in subsection 3.2.2, manifests a significant design challenge due to device mismatch. In addition to increased speeds, the absence of the clock can further reduce power consumption and frees up a significant portion of the footprint which is usually intended for clock distribution. Although, it should be mentioned that clocked logic is often necessary for further processing following high-speed CTBV operations. Luckily this can be done off-chip or in isolated parts of the system in a sort of hybrid design.

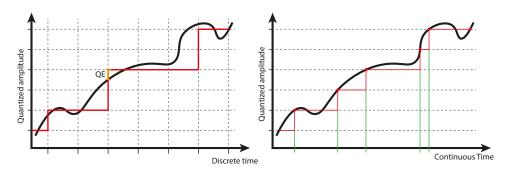

Quantization in digital signal processing involves the mapping of the continuous (time and value) input signal to a *limited* number of levels (bits) at discrete time intervals. As a rule of thumb, when a continuous signal is to be digitized, the finer the quantization, the more accurate the reconstructed signal will be. However, there is bound to be some error. This error, referred to as the *quantization error* (*QE*), describes the difference between the input value and its quantized value originating from the limited resolution of both time and value. In a CTBV system quantization error is eliminated as a problem as long as the signal remains continuous. In our system, we are quantizing and sampling in two separate operations. The quantizer used in this sampling system outputs a continuous-time binary signal that transitions precisely as the input signal crossed the given threshold level. We see that by not discretizing time (or value), no quantization error is introduced. However, upon sampling the 1-bit quantized signal, time is discretized, and the quantization error is introduced into the system.

Figure 2.1: QE is eliminated by removing discretization in either ampl. or time.

Many of the aforementioned advantages of CTBV signal processing also highlights some of its shortcomings. It is its simple logic and clockless design that facilitates the superior speeds, but it also limits the coding scheme of signals to just one bit, restricting available on-chip operations. Also, CTBV signal processing places a significantly harsher demand on the designer. For example, with poor design, it is conceivable that short pulses can completely disappear while propagating through a CTBV system, e.g., a delay line. If the inverters in said delay line are asymmetrically designed or have significant device mismatch, one transition will propagate faster through a gate than the other, effectively changing the pulse width. In a deep delay line, this possibly unintentional pulse shaping can eventually lead to pulses shrinking or expanding and eventually disappearing as one transition catches up to the other. At these high speeds, the performance also becomes more vulnerable to the inherent process variations in CMOS, i.e., *device mismatch*, which is the subject of section 2.6. By relaying information within the signal transitions and pulse widths, CTBV effectively becomes all the more vulnerable to this naturally occurring variation. We will be pushing the technology (TSMC 90nm low-power CMOS) towards its lower size limits to achieve the needed gate delays. A direct consequence of this will be a higher presence of mismatch. Considerable attention must be on reducing or compensating for the resulting effects of mismatch if we are to create a stable and robust sampling system.

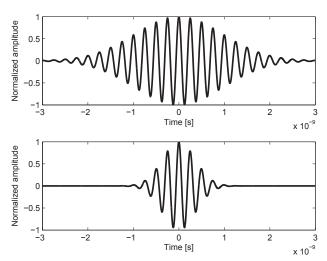

#### 2.3 Signal averaging

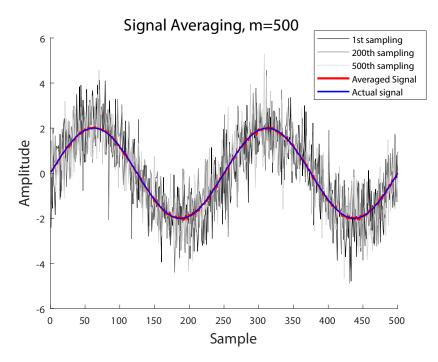

When there is a significant occurrence of noise within the frequency band of the signal, it will obscure the signal. With significant overlap between the signal and noise spectra, conventional noise reduction techniques, such as filtering, will fail since the filtering will also attenuate frequency components present in the signal, distorting it. Also, as mentioned in chapter 1, the backscattered signal will be very weak due to the high level of absorption in the body, leaving very little to be sensed by the photosensor. In other words, we have an inher-

ently weak reflected signal buried in noise which is to be represented with only a binary value quantization. Without compensation, the resulting SNR would be unacceptably low (< 0dB). Fortunately, the high speeds and binary coding scheme makes CTBV signal processing an ideal candidate for oversampling techniques such as signal averaging. Signal averaging (or processing gain), which is applied in the time domain, will improve the SNR and resolution of an A/D system at the cost of increased processing time and reduced throughput. By averaging over the sum of replicate measurements we can achieve an SNR significantly higher than the low native SNR of 1-bit signals. This is because the noise will average out with iterations, while the signal waveforms will sum together. There are however some requirements for this method to work. Signal averaging relies on repeated measurements, so the signal must be coherent (but not necessarily periodic). Also, for signal averaging to be effective, the signal must contain uniformly distributed noise (white) with a sufficient amplitude to cause random changes comparable to at least one LSB between samples. It is the random nature of white noise that makes signal averaging effective. By aligning each measurement with the previous iteration(s), the waveforms are summed. For this to work the temporal position of each signal waveform must be accurately known. The systematic signal components, S, in each repetition are combined so that after, e.g., m repetitions, the signal amplitude is m times larger than for a single measurement (mS). The noise, however, assuming that it is random, with  $\mu = 0$  and an average RMS value  $\sigma_n$ , will after m repetitions be the square root of the sum squared ( $\sqrt{m\sigma^2} = \sqrt{m\sigma}$ ). Thus, the SNR is improved by  $\sqrt{m}$ . This is confirmed mathematically below:

Assume an input signal f(t) consisting of both the coherent signal S(t) and the noise N(t):

$$f(t) = S(t) + N(t) \tag{2.1}$$

f(t) is sampled at a time interval of  $\tau$ . The value of a sample in time (i = 1, 2, ..., n) is then the sum of the signal and noise at that sample point.

$$f(\mathcal{T}_i) = S(\mathcal{T}_i) + N(\mathcal{T}_i) \tag{2.2}$$

For each repetition the data is accumulated in memory. So after m repetitions we have:

$$\sum_{k=1}^{m} f(\mathcal{T}_i) = \sum_{k=1}^{m} S(\mathcal{T}_i) + \sum_{k=1}^{m} N(\mathcal{T}_i) \quad \text{for } i = 1, 2, ..., n$$

(2.3)

With perfect alignment of repeated measurements, the signal component of each sample point is the same at each repetition, assuming a stable signal.

$$\sum_{k=1}^{m} S(\mathcal{T}_i) = mS(\mathcal{T}_i) \tag{2.4}$$

Under the assumption that the noise is uncorrelated and random with a mean of zero: after multiple repeated measurements  $N(\tau_i)$  has an RMS value of  $\sigma_n$ .

$$\sum_{k=1}^{m} N(\mathcal{T}_i) = \sqrt{m\sigma_n^2} = \sqrt{m}\sigma_n \tag{2.5}$$

Eqs. (2.4) and (2.5) gives the new SNR after m measurements as:

$$SNR_m = \frac{S(\tau_i)}{N(\tau_i)} = \frac{mS(\tau_i)}{\sqrt{m}\sigma_n} = \sqrt{m} \times SNR$$

(2.6)

Figure 2.2: Signal Averaging principle illustrated. Severely noisy signal recovered with with signal averaging over 500 measurements

In practice, signal averaging allows us to obtain higher-resolution A/D conversion with increased SNR through oversampling instead of increased complexity. For instance, to implement a 16-bit A/D converter, it can be sufficient to use a 12-bit converter that runs at 256 times the target sampling rate. By combining 256 consecutive 12-bit samples (within the required sampling period), the coherent signal increases by a factor of 256, while the noise by a factor of  $\sqrt{256}$ , so the SNR changes by a factor of 16 (=  $2^4$ ), effectively adding 4 bits to the A/D converter, producing a single sample with 16-bit resolution. However, signal averaging is only effective when the signal contains white uncorrelated noise with an amplitude significant enough to be detected by the A/D converter and causing random quantization level changes. If the A/D converter sees a stable input signal, all samples and the resulting average would be the same, rendering the averaging ineffective [7].

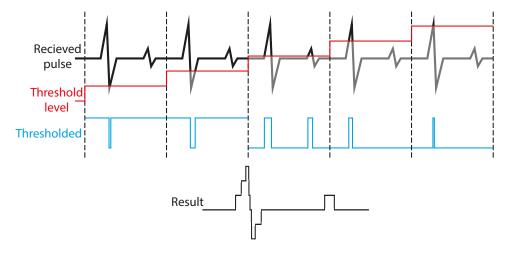

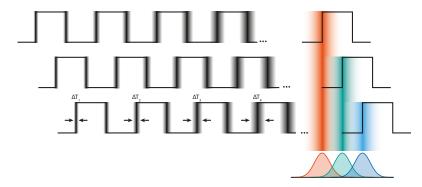

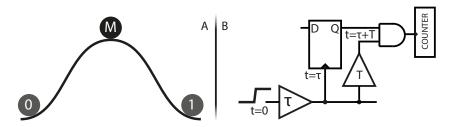

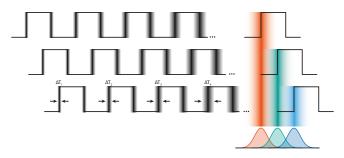

#### 2.4 Swept Threshold Sampling

Figure 2.3: Swept threshold principle

The required dynamic range can change significantly depending on the characteristics of the backscattered signal. With a weak and noisy backscatter in the pulsed LIDAR system, swept threshold becomes a viable sampling technique able to recover the pulse information efficiently. In swept threshold sampling a 1-bit quantizer compares the received signal with a given threshold level and outputs a digital, yet still continuous signal. This digital signal is then sampled by a series of 1-bit samplers in quick succession. Since the signal remains continuous after quantization, each sampler will capture the value at the exact time it is triggered. Following the sampling, accumulators connected to each sampler are incremented if the individual sample was "1". This procedure is repeated in a threshold level sweep across (only) the full range of the input signal, resulting in a sample and accumulate" operation which provides the averaging action needed to reconstruct the signal with a comfortable degree of SNR improvement. As highlighted in the previous section, the signal must be coherent. In other words, the signal (without noise) must be the same between measurements. Considering that the signal to be measured is the reflected pulse, this means that we require a stationary scene of a slowly changing process during the integration period. Furthermore, if swept threshold is to be effective in reconstructing weak signals, adequate threshold level control is required<sup>2</sup>. With swept threshold, the input range and threshold steps can be adjusted to better accommodate to the input signal characteristics. The input range can be traded in favor of faster sweep times, while processing gain can be adjusted with the number of steps [8]. This way the dynamic range of the sampling system will better relate to the input signal.

The theoretical limit of the SNR of an A/D converter (ADC) with no oversampling is:

$$SNR_{dB} = (6.02 \cdot ENOB) + 1.76$$

(2.7)

where *ENOB* is the effective number of bits. With a small signal amplitude expected from the LIDAR, ENOB will only be equal to the a small portion of the full range of the ADC; the dynamic range of the input signal does not match the rail-to-rail range of the ADC, hence it provides a poor initial resolution and low SNR. A substantial averaging effort will be required in order to acquire a decent SNR, and with a large number of unused quantization levels, the ADC will consume high amounts of power needlessly during this averaging. Swept threshold provides a more targeted A/D conversion. Considering that with weak signals with low SNR signal oversampling is unavoidable, swept threshold combines very well with CTBV, providing a cheap solution emphasizing power efficiency and high speed through its binary quantization and targeted dynamic range. One essential advantage of swept threshold sampling compared to multi-bit systems is that it required only a 1-bit quantizer, which simplifies the design and provides good inherent linearity of the system [8].

Figure 2.4: Multi-bit A/D conversion vs. swept threshold. Swept threshold allows us to adjust the sweep range and threshold steps depending on the input signal. This is yields an increased SNR while being more power efficient for weak signals. It is also faster and reduces the complexity of the sampling system.

In the backscattered signal, a significant relative level of uncorrelated white noise is expected. For a given threshold level this noise will lead to variations in the thresholded pulse widths and sometimes result in disappearing pulses. This might seem like a bad thing, but in fact, the white noise present can contribute in recovering weak signals which would otherwise go undetected. Signals below a given threshold level would by themselves pass unsensed, but with the added noise they will sometimes exceed the threshold and be picked up by the sampler. This behavior is referred to as *stochastic resonance* [9].

A full signal reconstruction could theoretically be achieved by using multiple quantizers similar to a flash ADC.  $2^N$  quantizers with individual threshold levels at linear intervals would provide a  $N_{bits}$  representation of the signal in a single sampling. However, to generate a 16-bits representation of the signal a total of 65535

<sup>&</sup>lt;sup>2</sup>Threshold level is set by an external high-resolution DAC

quantizers, each with individual threshold levels is required on-chip, which is not feasible [10]. By using a single quantizer, and repeatedly sampling the signal a total of  $2^{N_{bits}}$  times, each time with a unique threshold level, and then accumulating these results with counters, we achieve the same without the need of multiple quantizers. Besides, this method of sampling also has the benefit that a few bit errors now and then will not cause any significant errors. By integrating over multiple sweeps, the system becomes more robust, whereas, in a more conventional sampling system, e.g., a flash ADC, any such bit errors *could* have severe consequences on the results. The level of noise in the signal will determine how fine the threshold steps  $(\Delta V_{th})$  should be in order to recover the signal with adequate noise reduction. With noise levels greater than  $\Delta V_{th}$ , one can make the steps finer (reduce  $\Delta V_{th}$ ). However, this is not always an option, e.g., limitations in DAC that sets threshold levels. Instead, stochastic resonance can be utilized with swept threshold by performing multiple samplings at each threshold level. This is particularly useful in recovering weak signals where the noise is in the same order of magnitude as the signal, which is the expected scenario for the pulsed LIDAR.

#### 2.5 System architecture

As presented so far in this chapter, the basis for realizing a high-resolution noninvasive biomarker sensor has been laid. A quick summary of the previous sections:

- Transcutaneous sensing with targeted NIR light provides high depth of penetration in body tissue, but great absorption in tissue severely weakens the backscattered signal. With complex light-tissue interactions, a solution in time-of-flight, pulsed LIDAR, holds potential in addressing the challenges regarding selectivity. By measuring scattering at specific depths, selectivity may be significantly improved.

- High resolution is achieved with high sampling rates. 1-bit signal processing takes advantage of the inherent benefits of CMOS; speed and simplicity. Substituting clock synchronization with delay-based timing enables a system to operate in continuous-time with an operating speed limited by the inherent gate delay of the technology (1mm requires 100GS/s = 10ps).

- The coarse quantization and high potential rates of CTBV may help in increasing sensitivity as well. Signal averaging can, through repetition, manage to recover weak signals buried in (uncorrelated) noise. With very high sampling rates we can safely repeat measurements at frequencies in the *MHz* range (high PRF). The process in the body are very slow in comparison, so there will be practically no change over the course of a sampling period (blood glucose level show no significant change within a fraction of a second).

- The swept threshold technique allows us to adjust the dynamic range. The range and number of threshold levels (the step between) them decide the dynamic range of the sampler.

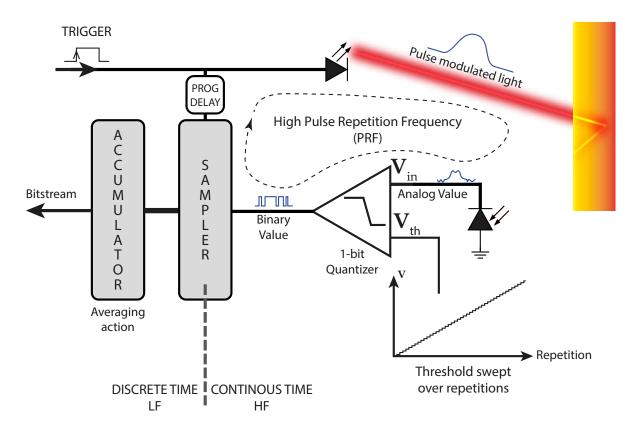

Figure 2.5: System architecture

Figure 2.5 illustrates the system architecture of the proposed pulsed LIDAR system. Conceptually we may consider the proposed LIDAR to be a modified radar with a RF-to-light transducer (laser-diode or LED) on the output and one or more light-to-RF transducer(s) (photodiode(s)) on the input. The weak echo pulses from modulated light directed into the body are sensed by photosensor(s) on the die. The signal is then thresholded and quantized, leaving it digital, yet still continuous. Digital samplers, triggered in quick succession, now performs the high-speed sampling of the signal. After sampling, accumulators connected to each sampler are incremented if a "1" was sampled. This procedure is repeated while sweeping the threshold level across the range of the input signal, resulting in a full readout of the received signal. This method of "sample and accumulate" through the range of threshold levels appear as an equivalent A/D conversion.

The down-range resolution of backscattered signals from static targets is proportional to the signal bandwidth. Since the signal bandwidth is inversely proportional to the signal duration in the time domain, a short light pulse will provide the highest depth resolution. Fortunately, wide signal bandwiths are allowed for modulated light (modulated light does not have to comply with the strict RF regulations of FCC<sup>3</sup> and ETSI<sup>4</sup>). However, the modulation bandwidth will become limited by the bandwidth limitation of the transducers. In this thesis, our primary objective is designing the high-speed sampler. It should be made clear that neither the quantizer or the photosensor(s) are within the scope of this thesis, and will therefore not be subject of any further discussion beyond this paragraph. I will limit myself to illuminating the necessary characteristics of the photosensor and the main features of the quantizer. With weak high-frequency backscatter, the photosensor(s) must be fast while also providing high responsivity for the wavelength range of interest. Designing photodiodes in standard CMOS (silicon substrate) that have both these characteristics at the same time come with its own set of technical difficulties. Suffice it to say that when confined to standard CMOS one of the only ways of increasing the speed of a photodiode is to reduce its junction capacitance, i.e., the active area. This increased speed comes at the expense of lower sensitivity, which means a loss in responsivity. Also, a smaller photodiode will have a higher noise floor, which can become a limiting factor considering the low light levels. The quantizer, developed by Novelda [11], converts the analog RF input signal to the CTBV domain in continuous time, able to react to minute changes in the input signal at high frequencies, with fine-grained control over threshold levels. It has shown good performance in similar systems, such as the successfully implemented swept threshold radar by

$<sup>^3</sup>$ Federal Communications Commission

<sup>&</sup>lt;sup>4</sup>European Telecommunications Standards Institute

Hjortland and Lande [6].

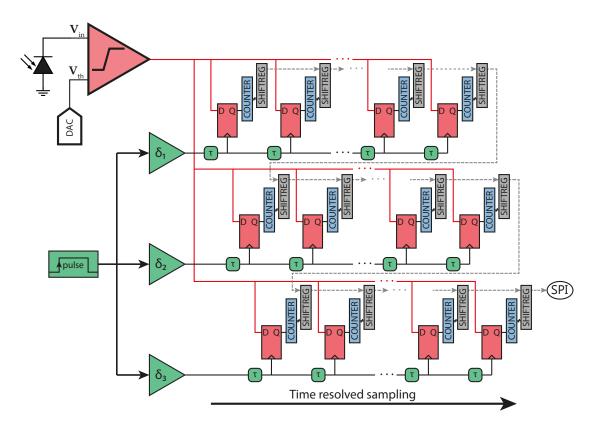

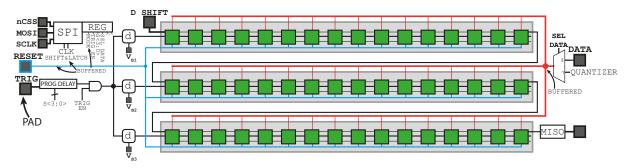

In short, the sampling system can be subdivided into four individual subsystems:

- Timing Delay line(s): Each unit delay of the dealy line consists of double inverters.

- 1-bit Samplers D flip-flops: Rising-edge triggered master-slave D flip-flops.

- *Accumulators Counters:* Asynchronous counters that increment with pulses applied to the counter's "CLK" input (sampler output).

- Readout Shift registers: Parallel in/Serial out (PISO) shift registers makes counter data accessible over SPI.

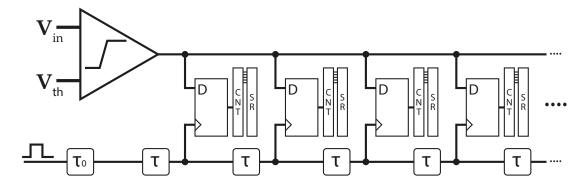

The implemented D flip-flops, counters and shift registers are detailed in chapter 3. Both the counters and shift registers are trivial in their design and since they are considered a part of the low-frequency digital domain, and require minimum attention at this point. The D flip-flop, however, can be viewed as the link between the high-frequency and low-frequency domain, and as such might prove to have a definitive impact the sampler performance due to a phenomenon referred to as *metastability*. This will be discussed in section 3.3. A cascade of delay elements makes up a delay line, which provides a history of an input signal. An applied trigger pulse will appear to travel within the line appearing at discrete points in time determined by the individual delay of each element. By using a delay line to trigger a sequence of samplers, tapped at these intermediate states, all with the thresholder output as their input, we have a sampling system which performs down-conversion from tens of gigahertz sampling rate to rates much more manageable by the accompanying digital logic (counters). With the explicit correlation between sampling rate and the equivalent spatial resolution, the delay lines will be of the utmost importance as they will determine the sampling rate of the sampler, and should be designed with elements at a minimum delay. However, with a small middle ground between success and failure, they will introduce significant design challenges.

Figure 2.6: Conceptual block diagram of swept threshold sampler

$$f_T \approx \frac{g_m}{2\pi C_L} \tag{2.8}$$

$$g_{m} = \frac{2I_{D}}{V_{ov}}, \ V_{ov} = V_{GS} - V_{th}$$

(2.9)

$$I_D = \frac{\mu C_{ox}}{2} \frac{W}{L} V_{ov}^{\alpha}, \ \alpha \in [1, 2]$$

(2.10)

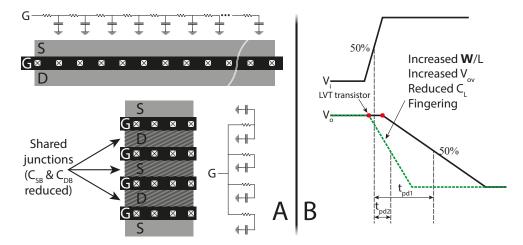

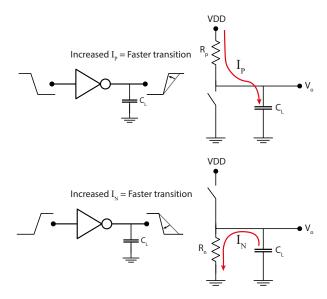

In the following paragraphs, we will investigate how short gate delays we can achieve in standard 90nm CMOS technology, how we can use this to reach our targeted sampling rate and touch on the challenges introduced in this design. Equation 2.8 refers to the transition frequency of a transistor  $f_T$ . It is defined as the frequency at which the current gain  $(\frac{I_{DS}}{I_{GS}})$  becomes unity, i.e., it represents the frequency where it transitions from an amplifier to an attenuator [12, p. 291]. It is determined by the relationship between transconductance  $(g_m)$  of the transistor, and the total capacitive load  $(C_L)$ . Equation 2.9 shows that  $g_m$  is proportional to the drain current,  $I_D$ . Intuitively this makes sense, since the higher the current, the faster it will charge its load capacitance. Equation 2.10 describes how  $I_D$  relates to the parameters of the transistor.  $\mu$  is the carrier mobility,  $C_{ox}$

the gate oxide capacitance, W and L are the dimensions of the gate, while  $V_{ov}$  is the gate overdrive voltage. For a given process node,  $C_{ox}$  is assumed fixed, while the mobility  $\mu$ , a fickle parameter, highly dependent on doping concentration, can also be considered a process dependent parameter. This means that for a given supply voltage, the designer is left only the device dimensions (primarily W) to adjust the gate delay of a transistor. Note that the majority of  $C_L$  consists of the gate capacitance  $(C_{ox} \frac{W}{L})$  of the following gate(s), with additional contributions from  $C_{wire} + C_{diff} + C_{parasitic}$ . This means that when scaling one gate to increase drive, the previous stage will see an increased load, increasing its delay. Increasing the gate overdrive voltage, i.e., increasing the difference between  $V_{GS}$  and  $V_{th}$ , can help to reduce the delay. This can be achieved by either increasing the supply voltage (within the constraints of the technology), which comes at the cost of greater power consumption  $(P_{dyn} \propto C_L V DD^2)$ , or as we will explore in subsection 3.2.2, through back-gate tuning which allows adjustment of the threshold voltage and grants some degree of delay adjustment.

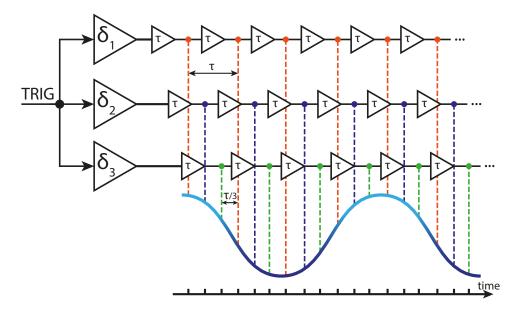

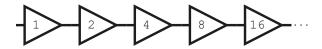

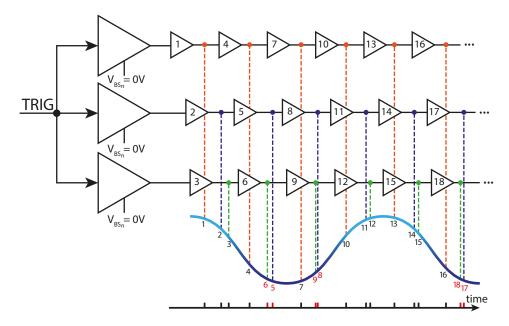

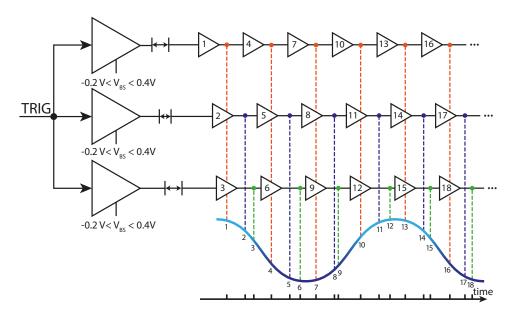

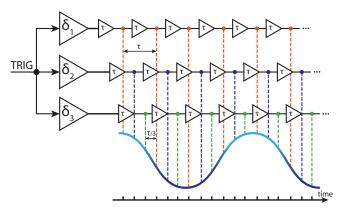

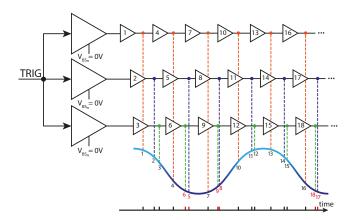

Previous publications [13], [14] indicate a nominal transition frequency for a single inverter approaching 100GHz, or  $t_{pd} = 10ps$ . However, considering parasitics and the added load on the output, a more realistic assumption is that a single inverter can operate with a propagation delay of around 15ps. In other words, it is feasible that a delay element consisting of two inverters can be designed to approach a delay as low as 30 ps reliably. Based on this lower limit in delay, a single delay line will allow for an effective sampling rate of approximately 33GHz ( $\frac{1}{30ps}$ ), as demonstrated by Hjortland and Lande [6]. However, the targeted depth resolution of 1mm equivalates to a sampling rate of 100GS/s, which means that the 1-bit samplers must be triggered at 10ps intervals. It becomes apparent that if we are to improve speeds any further, we will require parallelization to overcome this fundamental limitation in the technology. As mentioned in section 2.2, to further increase the time resolution in CTBV systems the relative difference between two delay elements can be exploited. By delaying signal A with for example 50ps, and signal B with 60ps we obtain a relative delay of only 10ps. This relative difference between delays can be used to create a timing configuration consisting of three parallel delay lines, in which each line is initiated with a relative time offset of 10ps to its neighbor(s). This approach of interleaving delay lines is illustrated in Figure 2.7 where, in this case, three delay lines are interleaved. This technique effectively triples the sampling rate and depth resolution, and is based on the premise that each initial delay differ from their neighbor with exactly 10ps and that the subsequent elements in each line all accurately generate a delay of 30ps in order to maintain a linear behavior and yield an effective sampling rate of 100GS/s. This will, however, not be the case. Since the conception of CMOS, stochastic variations in process parameters has induced a random mismatch in threshold voltage and current factor ( $\beta$ ) between identical devices. These unavoidable variations become more apparent as transistor sizes decrease, and will become a determining factor in the characterization of the sampling system. Device mismatch will limit the timing precision of the trigger pulse propagating through the delay lines and introduces restrictions on both speed and on how deep the delay lines can be designed.

Figure 2.7: Delay line interleaving.  $\delta_2 = \delta_1 + 10ps$ ,  $\delta_3 = \delta_2 + 10ps$ ,  $\tau = 30ps$

#### 2.6 Static Variations

#### 2.6.1 Process variation

As highlighted in the previous section; sufficiently fast delay elements are obtained by designing transistors with short and wide channels which reduce their capacitive load and maximize their drive potential, yielding fast switching transistors. When we are interleaving lines it is vital that all delay elements produce accurate delays. However, all transistors, particularly small ones, will suffer from the influence of process variations. These inescapable variations, originating from random atomic-level fluctuations and limitations in manufacturing, cause behavioral differences *between* devices, which means that no two CMOS devices are ever precisely alike. At smaller dimensions and lower supply voltages process variations are becoming increasingly relevant, since their contribution becomes a larger relative percentage of the device. Despite strides in the technologies, process variation remains a significant challenge in achieving high-speed, low voltage CMOS systems.

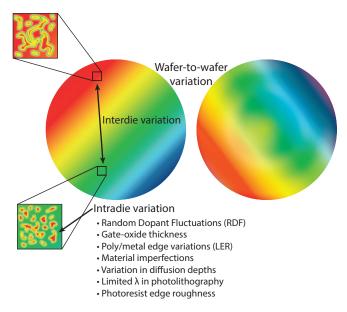

Process variation manifests across two kinds: interdie (die-to-die) and intradie (within-die) variations [15], [16] (in reality, also lot-to-lot and wafer-to-wafer, which mainly concerns high volume production, so we discard the considerations regarding such variations). Interdie variations, caused by systematic effects like process gradients on the wafer, are independent of device sizes. Interdie variations act globally on the entire die so that each device on the die experiences the same random shift in the mean value of device parameters. Intradie variations, however, affect each device within the same die in a different way. Intradie variations, commonly called *device mismatch*, can be categorized as random or systematic. The random component has a Gaussian distribution and shows no correlation across devices, which means that it cannot be predicted beyond statistical estimations. The systematic fluctuations exhibit spatial correlation and thus, lead to minimal variation for devices in close proximity. The relative effect on the mismatch due to device distance is only significant for large area devices with considerable spacing [16] and is therefore not considered in this thesis. Our definition of mismatch excludes all systematic variations and offsets of the absolute value of parameters caused during manufacturing by electrical, lithographic or timing differences.

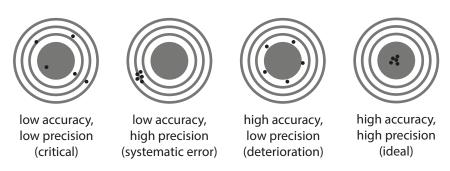

Figure 2.8: Process variations

In 1989 Marcel Pelgrom established that variations in threshold voltage and current factor ( $\beta$ ) are inversely proportional to the square root of the transistor area (Equation 2.11 and 2.12) [16]. This relationship, which has been shown to hold up quite well in modern CMOS technologies as well [17], intuitively means that the influence from mismatch on  $V_{th}$  and  $\beta$  will decrease with increased device sizes since the parameter variations will "average" over a greater distance or area. Note that  $V_{th}$  and  $\beta$  are not considered process parameters, but rather a result of several parameters, such as gate oxide thickness and substrate doping concentration. This shows that the local variation of such process parameters, p, are themselves dependant on the transistor dimensions (2.13). Furthermore, his experiments showed that threshold voltage variations are the dominant sources of drain-source current mismatch, which directly affects the gate-delay.

$$\sigma_{V_{th}} = \frac{A_{V_{th}}}{\sqrt{WL}} \tag{2.11}$$

$$\sigma_{\beta} = \frac{A_{\beta}}{\sqrt{WL}} \tag{2.12}$$

$$\sigma_p \propto \frac{1}{\sqrt{LW}}$$

(2.13)

where W is the gate-width and L is the gate-length, and the proportionality constants  $A_{V_{th}}$  and  $A_{\beta}$  are technology-dependent.

$$V_{th_N} = V_{th_0} + \gamma \left( \sqrt{|V_{SB} + 2\phi_F|} - \sqrt{|2\phi_F|} \right)$$

(2.14)

where

$$\gamma = (t_{ox}/\epsilon_{ox})\sqrt{2q\epsilon_{Si}N_A}$$

(2.15)

and

$$\phi_F$$

is the surface potential (2.16)

The body effect equation (2.14) which describes the resulting threshold voltage when a substrate bias is applied to (in this case) a NMOS transistor (body- or back-gate-effect), helps us illuminate how parameter variations have a direct effect on the electrical properties of a transistor. As the equation shows,  $V_{th}$  is proportional to the body effect parameter ( $\gamma$ ) which includes the oxide thickness ( $t_{ox}$ ) and doping concentration ( $N_A$ ). Intuitively any variations in these parameters would result in variations in  $V_{th}$ . Mizuno et al. [18] established that depletion layer charge fluctuation due to random dopant fluctuation (RDF) is the primary cause of  $V_{th}$  variation. In modern technologies RDF has been shown to have a more substantial impact since the number of dopants is substantially fewer [19]. They also showed that  $V_{th}$  fluctuations as a result of variations in the oxide thickness, although small, decreased linearly with decreasing oxide thickness (Equation 2.17). For a long time, as technologies scaled down, mismatch consistently improved due to a steady decrease in gate oxide thickness and better channel doping control which resulted in lower threshold voltages. In the last decade, however, the oxide thickness and threshold voltage scaling have significantly slowed down, as some parameters are approaching fundamental limits, both physical and to avoid unwanted effects such as time-dependent gate oxide breakdown<sup>5</sup>.

Due to the random nature of ion implantation, dopant diffusion and other processes involved in the doping of silicon, the number of channel dopants exhibits a statistical variation given by the Gaussian function [20]. With a discrete and random number of dopant atoms in the channel, there emerges an inherent spreading of various transistor parameters. Equation 2.17 shows how  $\sigma_{V_{th}}$  depends on  $t_{ox}$ ,  $N_A$  and the device area. It has been shown by later publications, that the analysis done by Mizuno is somewhat limited as it does not take into account all process contributions, such as S/D dopant fluctuation and substrate bias [20], but within the scope of this thesis, it provides sufficient insight into the parameters influencing  $\sigma_{V_{th}}$ .

$$\sigma_{V_{th}} = \left(\frac{\sqrt[4]{4q^3\epsilon_{Si}\phi_B}}{2}\right) \times \frac{t_{ox}}{\epsilon_{ox}} \times \frac{\sqrt[4]{N_A}}{\sqrt{W_{eff}L_{eff}}}$$

(2.17)

where  $\phi_B = 2k_BT\ln(N_A/n_i)$  ( $k_B$ : Boltzmann's constant, T: temperature,  $n_i$ : carrier concentration, q: elementary charge), and  $\epsilon_{Si}$  and  $\epsilon_{ox}$  are the permittivity of silicon and oxide.  $L_{eff}$  &  $W_{eff}$  are used to not include the offsets in the device area introduced by L/W variation.

<sup>&</sup>lt;sup>5</sup>A conducting path is formed through the gate oxide to substrate due to electron tunneling.

| <b>Process Parameters</b>            | Electrical Parameters             |

|--------------------------------------|-----------------------------------|

| Flatband voltage $(V_{fb})$          | Drain-source current ( $I_{DS}$ ) |

| Mobility (μ)                         | Input voltage ( $V_{GS}$ )        |

| Dopant concentration $(N_A)$         | Trans-conductance $(g_m)$         |

| Length offset ( $\Delta L$ )         | Output Conductance $(g_0)$        |

| Width offset ( $\Delta W$ )          |                                   |

| Short Channel Effect $(V_{tl})$      |                                   |

| Narrow Width Effect $(V_{tw})$       |                                   |

| Gate Oxide Thickness ( $t_{ox}$ )    |                                   |

| S/D Sheet Resistance ( $\rho_{sh}$ ) |                                   |

Table 2.2: [21] Process parameters manifest changes in the electrical behavior of a device, whereas the electrical parameters are those parameters usually of interest to the designer.  $V_{th}$  is highly dependent on  $N_A$ , which is not a finite number, as it depends on L, W, and the body bias. For this reason  $V_{th}$  does not belong in either category.

The process parameters that influence mismatch are fundamentally bound to the technology itself and are thus not variables that the designer can tune. During design, the circuit designer is left with only the device dimensions and layout to control the matching. However, during operation, the gate overdrive voltage, defined as the difference between the gate-source voltage ( $V_{GS}$ ) and the threshold voltage ( $V_{th}$ ), has a substantial influence on the contribution from threshold voltage variations. The resulting drain current modulation for a given  $V_{th}$  shift will be diminished by increasing  $V_{ov}$ . This becomes evident when studying the generic Sakurai model equation for drain-source current in saturation (2.18) [22]. For digital logic,  $V_{GS}$  in the equation can be considered to be VDD.

$$I_{DS,sat} = \frac{\mu C_{ox}}{2} \frac{W}{L} (\underbrace{V_{GS} - V_{th}})^{\alpha}$$

(2.18)

where  $\alpha$  is the velocity saturation index ranging between 1 and 2; 2 for long channel and close to 1 for short channel (sub-100nm) technologies. Considering the linear relationship between saturation current and  $V_{ov}$ , short channel devices are less sensitive to  $V_{th}$  (and VDD) variation than long channel devices, but it still remains significant. The supply voltage is limited by technology specifications and is not a variable that can be adjusted extensively to increase  $V_{ov}$ . Applying excessive voltages can cause a breakdown of the internal junctions of a transistor, which leads to an exponential increase in current, and high power dissipation. The trend of reducing supply voltages has made the impact of  $V_{th}$  mismatch more severe, however, many technologies provide low threshold transistors (LVT) that will operate with greater  $V_{ov}$  (at the cost of increased leakage current). At a fixed power supply voltage, low threshold devices become less sensitive to variations in threshold voltage (or VDD).

#### 2.6.2 Mismatch in the delay lines

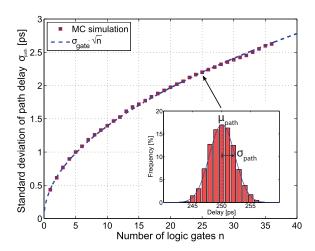

In most systems, there will be paths that are more sensitive to mismatch than others. These *critical paths* tend to become bottlenecks and often require particular attention. In the presence of mismatch, all devices will exhibit a random tendency to stray from their expected characteristics, such as the propagation delay. Any two (seemingly) identical paths will produce different, uncorrelated delays. The impact of mismatch on the propagation delay of a digital logic path can be investigated by studying a string of n identical logic gates, each with a mean gate delay of  $\mu_g$  and a standard deviation of  $\sigma_g$ . The total mean path delay,  $\mu_{path}$ , will display a linear relationship with n, while the total standard deviation of the path delay,  $\sigma_{path}$ , increases only proportional to  $\sqrt{n}$  [19]. This means that the *relative* delay variation of the path, its coefficient of variation (CV), decreases proportionally to the inverse square root of n. Note that it is the relative uncertainty that decreases with the path length, not the absolute standard deviation. Even though the delay of a long path will have a higher standard deviation than a short path, its standard deviation relative to the mean will be lower, i.e., its delay variability is lower (Figure 2.9).

$$\mu_{path} = n \cdot \mu_{g} \tag{2.19}$$

$$\sigma_{path} = \sqrt{n} \cdot \sigma_{g} \tag{2.20}$$

$$CV = \frac{\sigma_{path}}{\mu_{path}} = \frac{\sqrt{n}}{n} \frac{\sigma_g}{\mu_g} = \frac{1}{\sqrt{n}} \frac{\sigma_g}{\mu_g}$$

(2.21)

Figure 2.9: Effect of mismatch on critical path delay [19]

This means that long paths exhibit an "averaging" that tends to generate a total delay that is closer to the expected mean value, while shorter paths, generate a shorter delay, but display a greater tendency to differ from its expected delay. In our delay lines, it is not the total propagation delay of the line(s) that is of interest, but rather the specific delay of each delay element that makes up the line. Remember, the samplers tap the trigger pulse as it appears at each intermediate stage of the line(s). Accordingly, this means that we must consider the delay element our critical path. With a critical path of only two minimum length inverters, we expect a high coefficient of variation. The high relative delay mismatch in each delay element is expected to give rise to a more nonuniform propagation of the trigger pulse, which will result in inequidistant sampling. The variation at one stage in the delay line will affect all subsequent stages. In other words, the deviation in the nth stage will include the accumulated contribution of delay mismatch from all the preceding stages. Intuitively, this accumulation of mismatch leads to an increasing deterioration as the number of cascaded delay elements increase. As previously mentioned, delay line interleaving will be necessary to increase the effective sampling rate beyond the limitations set by the shortest gate delay of the technology. An important observation to be made at this point: When considering the accumulative deterioration of certainty in delay present in each delay line in combination with interleaving we see that there exists a possibility that samplers can trigger in non-sequential order. The probability of this happening increases the further into the line(s) the trigger pulse travels, meaning that there will be a limitation on the depth of the lines, determined by the degree of mismatch in the delay elements. The problem is illustrated in Figure 2.10.

*Remark*: This deterioration will also be impacted by jitter (section 2.7).

Figure 2.10: Accumulative deterioration of timing accuracy due to mismatch in the delay lines.

In section 3.2 we will perform Monte Carlo simulations (MC) on the delay elements to help "predict" the influence of mismatch on the delay line characteristics. MC is a statistical analysis that assists us in determining the influence of mismatch by performing simulations over a wide range of randomly chosen device parameters (corners), in accordance to the mismatch model of the technology. The results provide a statistical prediction on how the collective impact of process variations accumulate and affect the delay line performance, which will assist us in the design effort.

#### **2.6.3 Summary**

- Mismatch is caused during manufacturing by statistical variations in the process parameters that determine the behavior of devices. The random and uncorrelated nature of mismatch means that no two devices are ever identical.

- The parameters are fundamentally bound to the technology. For a given technology, the impact of mismatch can only be mitigated only with increased device area and through increasing the gate overdrive voltage. During operation, compensation for mismatch can be achieved by back gate tuning devices.

- Path delay variations become more prominent for smaller dimensions and reduced supply voltages. The relative delay variations in a path also display a dependence on its depth.

- The delay elements that make up the delay lines have been identified as *critical paths*, expected to have a high relative delay variation due to their minimum size and low depth. The accumulation of mismatch in the delay line places a constraint on the depth of the delay lines.

#### 2.7 Environmental Variations

While process variations originate from the limitations of manufacturing, environmental variations are the result of the surrounding environment of the chip during its operation. These variations incorporate temperature variations, power supply variations and variations in switching activity which result in a varying performance. The small leakage currents of CMOS devices produce a minimal static power consumption ( $P_{stat}$ ). However, when switching at high frequencies, the dynamic power consumption ( $P_{dyn}$ ) will contribute significantly to the overall power consumption of a system. The dynamic power consumption is the sum of the transient ( $P_T$ ) and the capacitive-load ( $P_L$ ) power consumption. As a device switches from one state to another, there is a transient current spike that originates from the charging of the internal nodes and a brief current that flows from VDD to GND while both N- and PMOS are on at the same time. Considering the fast transitioning delay elements, this "through current" is considered negligible compared to the charging current. Further power is consumed in the charging/discharging the applied load capacitance(s) of the device [23].

$$P_{tot} = P_{stat} + P_{dyn} (2.22)$$

$$P_{stat} = I_{leak} \cdot VDD \tag{2.23}$$

$$P_{d\gamma n} = P_T + P_L \tag{2.24}$$

$$P_T = C_{PD} \cdot VDD^2 \cdot f \tag{2.25}$$

$$P_L = \sum (C_{Ln} \cdot f) \cdot VDD^2 \tag{2.26}$$

where

Ileak is the leakage current

$C_{PD}$  is the internal capacitance of the device

$C_{Ln}$  is the capacitance of load n (fanout)

With a variable switching activity of the chip, the current demands on the supply voltage will consequently vary. With parasitics in the power delivery system, this changing power requirement results in a fluctuating supply voltage, i.e., power-supply noise. Analog devices are particularly vulnerable to power-supply noise since they often rely on stable bias points. In digital logic, the situation is not as severe since the noise margins for false transitions are significantly wider. However, the supply noise will affect their timing properties. In our delay lines, this noise will introduce a timing jitter which translates to an increased variation in the sampling instants [24]. The power-supply noise causes variations in the drive strength of the transistors and modulates their delay (see Equation 2.8). The uncorrelated variation in behavior between transistors caused by mismatch means that each device will be affected differently by this noise. In section 3.8 we will discuss how the power-supply noise is reduced in our design.

Furthermore, the generated heat during operation leads to fluctuating gate delays. This can be attributed to both a temperature induced threshold voltage variation and carrier mobility fluctuation [25]. Equation 2.27 shows how the surface potential  $(\phi_F)$  is proportional to the absolute temperature T. Remembering the body effect equation (Equation 2.14) this means that the threshold voltage reduces as the temperature increases, which in turn improves the gate delay. Note that as the generated heat lowers the threshold voltage of transistors, leakage currents are increased. These increased leakage currents lead to higher static power consumption, which in turn contributes to increased temperature. Observe how this positive feedback can cause failure if strong enough.

$$\phi_F = \left(\frac{kT}{q}\right) \ln\left(\frac{N_A}{n_i}\right) \tag{2.27}$$

where k is Boltzmann's constant, q is the elementary charge, and  $N_A$  and  $n_i$  are doping parameters.

Whereas the threshold voltage decreases with temperature, the carrier mobility displays an inversely proportional response to temperature, as shown by Equation 2.28. This means that the contributed gate delay modulation from mobility is therefore negative for an increased temperature.

$$\mu(T) = \mu(T_r) \left(\frac{T}{T_r}\right)^{-k_{\mu}} \tag{2.28}$$

where  $T_r$  is the room temperature and  $k_\mu$  is a fitting parameter ~ 1.5

It can be summarized that environmental variations can have a notable effect on the precision and delay resolution of delay lines during operation. These variations are not random since they depend on the workload of the system and is therefore time-dependent. The scenario which results in the worst-case voltage supply drop can occur at any time and is accordingly extremely difficult to predict. Likewise is the temperature dependent on a multitude of factors such as the ambient temperature and how well the chip dissipates heat through conduction, convection and radiation.

### **Chapter 3**

## **Implementation**

In this chapter, we will describe how the proposed architecture has been implemented in CMOS. As we introduce the various sub-systems, relevant analysis and discussion are presented to reveal the reasoning behind the design.

#### 3.1 Sampling System

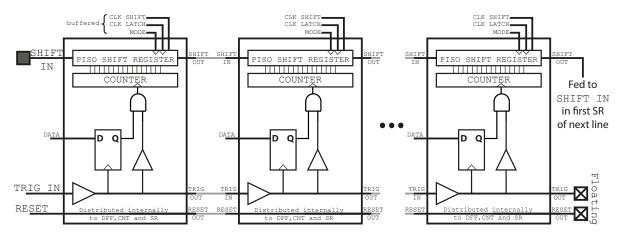

Figure 3.1 shows a block diagram of the sampling system. Additional supporting circuitry has been deliberately excluded at this stage to provide a clear system overview. However, as additional circuits become relevant, they will be introduced and discussed in detail throughout this chapter. The core subsystems are color-coded as such: TIMING, SAMPLING, INTEGRATION, READOUT.

Figure 3.1: Simplified block diagram of the sampling system,  $\delta_2 = \delta_1 + 10ps$ ,  $\delta_3 = \delta_2 + 10ps$ ,  $\tau = 30ps$ .

#### 3.2 Delay lines

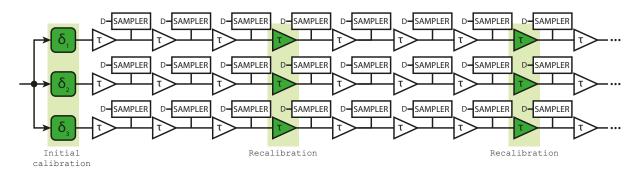

The "spine" of the system can be considered to be the three interleaved delay lines. Each line consists of 16 cascaded delay elements of double inverters designed to have a unit delay of  $\tau=30ps$ . Preceding each line is an initial delay element whose purpose is to create a relative offset of  $\delta\tau_o=10ps$  to the adjacent line(s). This offset is what enables the interleaved propagation of the trigger signal through the system which, in an ideal scenario will yield an effective sampling rate of 100GS/s (1/10ps). For the sampler to operate as intended, it is preferred that the delays are as equally spaced in time as possible. This way the samplers are triggered at regular intervals, generating an *equidistant* sampling sequence. In other words, the samplers trigger in sequential order, with a constant delay of 10ps. This can only be achieved if each line is initially offset to its neighbor by 10ps and that the subsequent delay elements do not deviate from 30ps. To illustrate this more abstractly:

- The term precision is used in this context to describe how similar the delay elements are. We relate the term to the degree of variations in the lines, i.e., the standard deviation of the delay elements. Extensive variation (high  $\sigma$ ) between the delay elements due to mismatch and/or other effects, i.e., a low precision, will lead to a rapid deterioration of the linearity of trigger pulse occurrences (see subsection 2.6.2). The level of precision is a restricting factor for maximum line depth, which directly relates to how large a window in time we can sample. With severe mismatch in the delay elements, the sampling can become inequidistant or even nonsequential at an early stage in the interleaved system.

- The term *accuracy* is used to indicate how close to the target delay the elements are. The system is designed in such a way that we are highly dependent on the delays reaching or coming close to this target value for the interleaved sampling to be correct. Since a relative initial delay of  $\delta_{\tau_0}$  is used to offset the lines, all subsequent elements must produce a delay of  $\tau = \delta_{\tau_0} \cdot 3$  (3 lines) to maintain a uniform temporal spacing between triggered samplers. To achieve the targeted sampling rate of 100GS/s,  $\delta_{\tau_0}$  must be 10ps, which means that  $\tau = 30ps$ . Note that, assuming 100% precision ( $\sigma = 0s$ ), a lack of accuracy, e.g.,  $\tau = 33ps$ , will not cause any deterioration, just a systematic error in the form of a constant inequidistant or non-uniform pulse propagation.

Figure 3.2: Illustration of accuracy vs. precision

In reference to our previous discussions on mismatch (subsection 2.6.2), it becomes clear that when striving to maximize the accuracy of the delay elements, i.e., short and wide transistor channels, there is an inadvertent negative impact on the precision of the lines as a result of an increased presence of mismatch. In this situation of mutually conflicting conditions, the challenge lies in the balancing act between accuracy and precision.

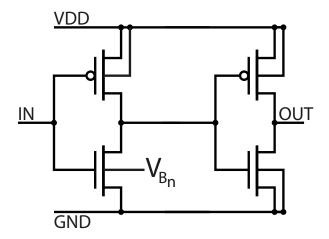

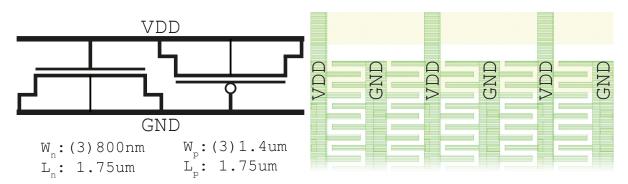

#### 3.2.1 Delay Element

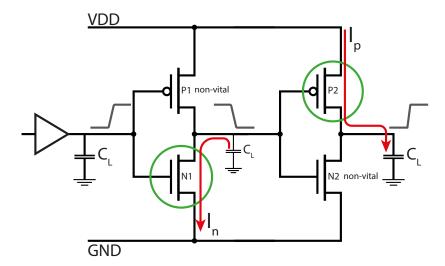

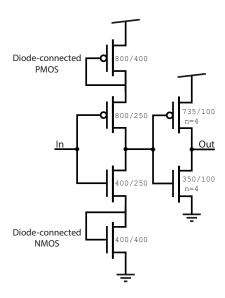

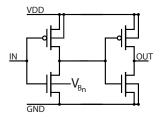

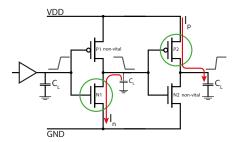

To create these high-resolution delay elements, the transistor lengths are kept at the minimum size (100nm) while the widths are increased to improve their drive strength. The total capacitive load seen at an output is  $C_L = C_{self} + C_{wire} + C_{fanout}$ , where  $C_{self}$  is the combined output junction capacitance of the driving device,  $C_{wire}$  is the total interconnect capacitance, and  $C_{fanout}$  is the sum of the subsequent gate capacitances. Due to the repeating pattern in the sampler, the load capacitance seen by the elements is close to constant. Thus, apart from the initial custom delays, the elements are identical - designed to have a drive strength which yields a delay of 30ps. Since it is primarily the rising edge which is of interest to us, the inverters in the delay elements can be designed asymmetrically (to facilitate fast rising edge behavior), which will help to reduce their junction capacitance and consequently both their rising edge delay and the load seen by previous output transistor. As

mentioned in section 2.2, this design choice will have the side effect of increasing the width of the trigger pulse as it travels through the lines, but considering the low line depths (16) and relatively long pulse period, it is not expected to cause any complications in this design.

Figure 3.3: By keeping  $W_{P1}$  and  $W_{N2}$  small the capacitive load is reduced at the expense of slower falling edge transitions.