# Single Bit Radar Systems for Digital Integration

Øystein Bjørndal

Department of Informatics

University of Oslo (UiO)

Norwegian Defence Research Establishment (FFI)

$September\ 2013-September\ 2017$

Thesis submitted for the degree of Philosophiae Doctor

# Abstract

Small, low cost, radar systems have exciting applications in monitoring and imaging for the industrial, healthcare and Internet of Things (IoT) sectors. We here explore, and show the feasibility of, several single bit square wave radar architectures; that benefits from the continuous improvement in digital technologies for system-on-chip digital integration. By analysis, simulation and measurements we explore novel and harmonic-rich continuous wave (CW), stepped-frequency CW (SFCW) and frequency-modulated CW (FMCW) architectures, where harmonics can not only be suppressed but even utilized for improvements in down-range resolution without increasing on airbandwidth. In addition, due to the flexible digital CMOS implementation, the system is proved by measurement, to feasibly implement pseudo-random noise-sequence and pulsed radars, simply by swapping out the digital baseband processing. Single bit quantization is explored in detail, showing the benefits of simple implementation, the feasibility of continuous time design and only slightly degraded signal quality in noisy environments compared to an idealized analog system.

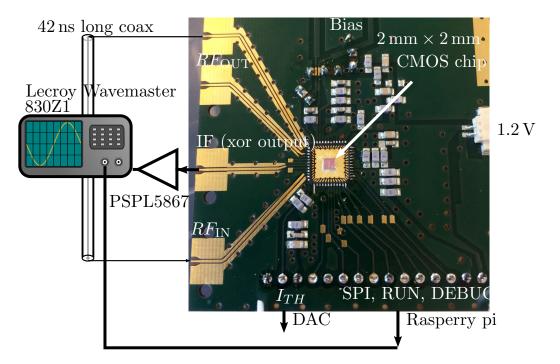

Several iterations of a proof-of-concept 90 nm CMOS chip is developed, achieving a time resolution of 65 ps at nominal 1.2 V supply with a novel Digital-to-Time converter architecture. In pulsed mode, the chip features programmable pulses with a minimum width of 130 ps and a time step of 65 ps. In CW mode, we can transmit arbitrary signals up to 3.8 GHz all the way down to DC. With a continuous time single bit receiver, the backscattered signal can be mixed with the on-chip XOR gate and integrated with the on-chip counters, to provide a system-on-chip CW platform.

# Acknowledgments

I am really grateful to everyone who has collaborated, motivated and supported me throughout this work. In particular, my supervisors Svein-Erik Hamran from FFI and Tor Sverre Lande (Bassen) from UiO; whose insight not only in their respective fields but also cross-discipline, goes without saying, has been invaluable. Thank you to Svein-Erik for always having an open door, your motivation, guidance and realistic goals have helped me grow as a researcher. Thanks to Bassen for pushing boundaries and scrutinizing my suggestions, both the long and short conversations, in-person and by email; has not only been motivating but also enlightening.

My colleagues both at FFI (Norwegian Defence Research Establishment) and at the Nanoelectronics group at UiO (University of Oslo) for your support, insight and lunch breaks: Tor Berger, Sverre Brovoll, Leif Damsgård and Mats Jørgen Øyan from FFI and Philipp Häfliger, Yngvar Berg, Joar Martin Østby, Kristian Gjertsen Kjelgård, Olav Stanly Kyrvestad, Mathias Tømmer, Jon Håvard Eriksrød, Tohid Moradi Khanshan, Amir Hasanbegovic and Sohail Musa Mahmood from UiO. Especially Kristian and Olav, without whom this thesis would be purely theoretical, for your assistance and support with chip tapeout, circuit board design, fabrication, lab setup and debugging.

I would like to acknowledge some of the previous PhD students working on the swept threshold principle and implementation for pulsed radar: Håkon Andre Hjortland, Malihe Zarre Dooghabadi, Shanthi Sudalaiyandi and Nguyen Thanh Trung whose circuit blocks have all been vital for the chip prototype in this work. In particular, to Håkon, for paving the way with the swept threshold principle and for your invaluable and insightful comments. I am also grateful to Novelda for the comparator.

Financial support from FFI from September 2013 through December 2016 and UiO from January 2017 through June 2017 is gratefully acknowledged.

Lastly to the love of my life, Ine, thank you for your patience and understanding and to my family for your support and encouragement.

# Contents

| Ι | $\mathbf{T}$ | nesis     |                                            | 1  |

|---|--------------|-----------|--------------------------------------------|----|

| 1 | The          | e first o | $\operatorname{chapter}$                   | 1  |

|   | 1.1          | Introd    | luction to the proposed radar              | 4  |

|   |              | 1.1.1     | Analog radar                               | 4  |

|   |              | 1.1.2     | Digital transmitter                        | 6  |

|   |              | 1.1.3     | Digital transmitter and receiver           | 8  |

|   |              | 1.1.4     | Proposed radar solution                    | 8  |

|   |              | 1.1.5     | Beneficial harmonics                       | 11 |

|   |              | 1.1.6     | Summary                                    | 12 |

|   | 1.2          | Applio    | cations                                    | 13 |

| 2 | Bac          | kgroui    | nd                                         | 15 |

|   | 2.1          | Radar     | architecture fundamentals                  | 15 |

|   |              | 2.1.1     | Pulsed time-of-flight radar                | 17 |

|   |              | 2.1.2     | Continuous-Wave (CW) Radar                 | 18 |

|   |              | 2.1.3     | Stepped-Frequency Continuous-Wave (SFCW)   | 22 |

|   |              | 2.1.4     | Frequency-Modulated Continuous-Wave (FMCW) | 26 |

|   |              | 2.1.5     | Correlator based radar                     | 28 |

|   | 2.2          | Swept     | threshold                                  | 35 |

|   |              | 2.2.1     | A single quantizer                         | 36 |

|   |              | 2.2.2     | Multiple quantizers                        | 39 |

| 3 | Sys          | tem pe    | erspective                                 | 51 |

|   | 3.1          | Time      | resolution                                 | 52 |

|   |              | 3.1.1     | Continuous time                            | 54 |

|   |              | 3.1.2     | Discrete time                              | 56 |

|   | 3.2          | Thern     | nal noise                                  | 60 |

|   |              | 3 2 1     | Intentional dithering                      | 62 |

|   | 3.3                         | Moving    | g targets                                           |

|---|-----------------------------|-----------|-----------------------------------------------------|

|   |                             | 3.3.1     | Tracking                                            |

|   |                             | 3.3.2     | Comparing frames in time 67                         |

|   |                             | 3.3.3     | Doppler shift                                       |

|   |                             | 3.3.4     | Summarizing moving targets                          |

| 4 | Imp                         | olement   | tation 79                                           |

|   | 4.1                         |           | n overview                                          |

|   |                             | 4.1.1     | SPI configuration                                   |

|   |                             | 4.1.2     | Transmitter                                         |

|   |                             | 4.1.3     | Receiver                                            |

|   | 4.2                         | Design    | flow                                                |

|   |                             | 4.2.1     | Analog design                                       |

|   |                             | 4.2.2     | Testbenches                                         |

|   | 4.3                         | Conclu    | ding implementation                                 |

| 5 | Bas                         | eband     | 99                                                  |

|   | 5.1                         | Analog    | g filter and ADC baseband path                      |

|   |                             | 5.1.1     | Double swept threshold baseband                     |

|   | 5.2                         | Cascad    | led Integrator-Comb filters                         |

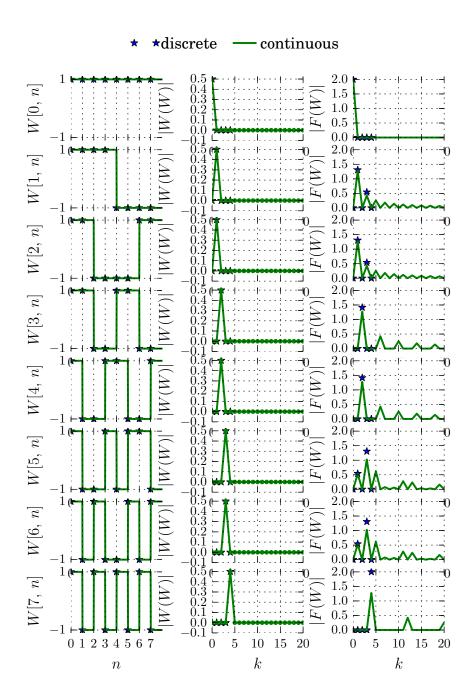

|   | 5.3                         | Fourier   | r and Walsh transform of square wave signals 112    |

|   |                             | 5.3.1     | Implementation, XOR as a multiplication circuit 117 |

|   |                             | 5.3.2     | Utilizing Walsh in a square wave radar 117          |

|   |                             | 5.3.3     | Walsh and m-sequence                                |

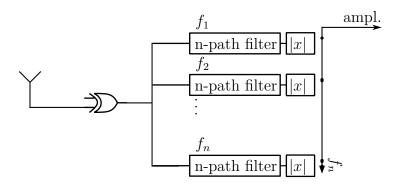

|   | 5.4                         | N-path    | n filter bank                                       |

|   |                             | 5.4.1     | Relationship to a superheterodyne receiver 125      |

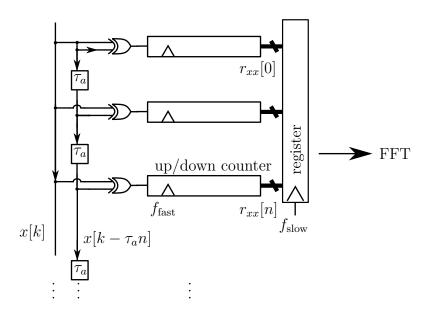

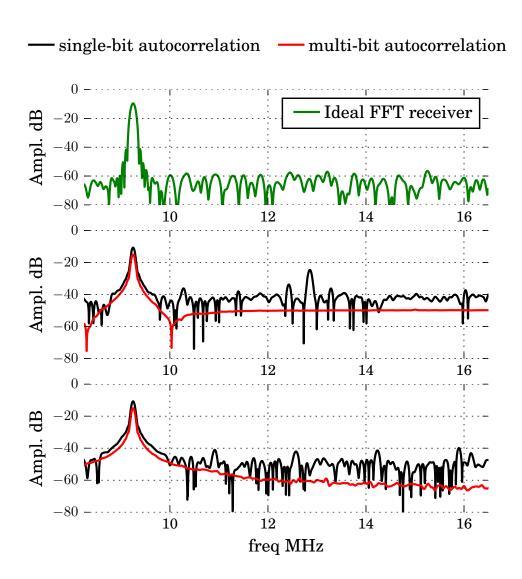

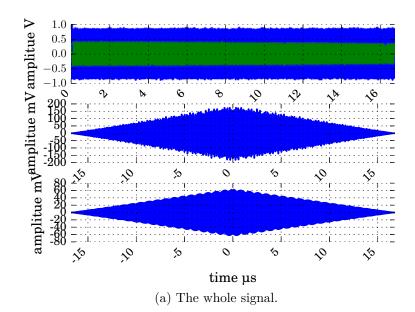

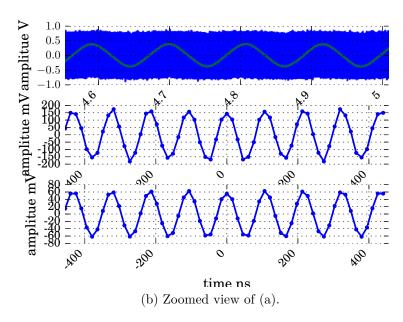

|   | 5.5                         | From a    | autocorrelation to Fourier domain                   |

|   | 5.6                         | Conclu    | uding baseband                                      |

| 6 | $\operatorname{Th}\epsilon$ | e last cl | hapter 133                                          |

|   | 6.1                         | Summa     | ary of thesis and published papers                  |

|   | 6.2                         | Discuss   | sion and limitations of this work                   |

|   | 6.3                         | Future    | work                                                |

|   | 6.4                         | Conclu    | usion 139                                           |

| Η            | $\mathbf{P}$ | ublications included in the thesis                 | 141 |

|--------------|--------------|----------------------------------------------------|-----|

| $\mathbf{A}$ | Pap          | er I                                               | 143 |

|              | A.1          | Introduction                                       | 145 |

|              | A.2          | Quantization in amplitude and time                 | 147 |

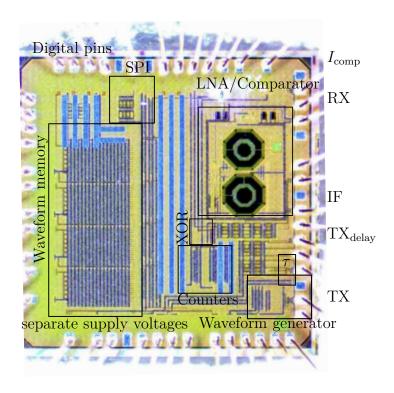

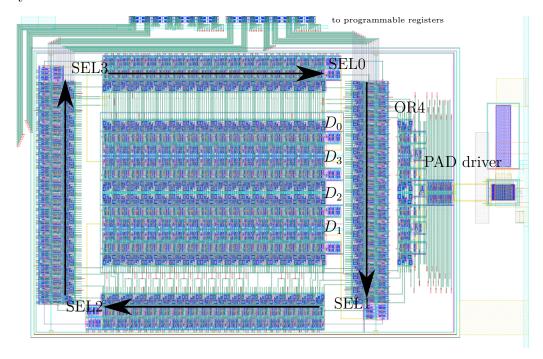

|              | A.3          | Fabricted chip                                     |     |

|              | A.4          | Measurement results                                | 152 |

|              | A.5          | System simulation                                  | 154 |

|              | A.6          | Conclusion                                         | 155 |

| В            | Pap          | er II                                              | 159 |

|              | B.1          | Introduction                                       | 161 |

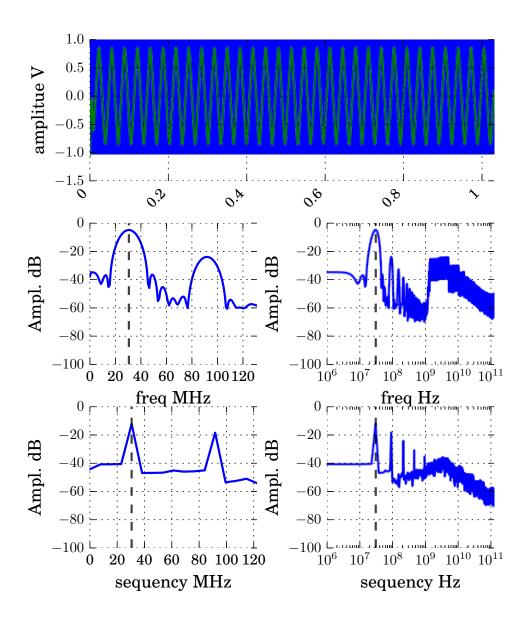

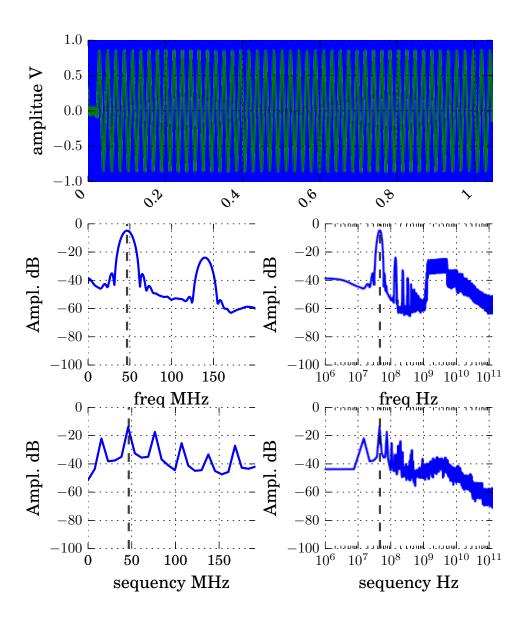

|              | B.2          | Dealing with harmonics                             | 163 |

|              |              | B.2.1 Moving out of band                           | 163 |

|              |              | B.2.2 Resolving in band ambiguity                  | 165 |

|              | В.3          | Post layout XOR simulation                         | 167 |

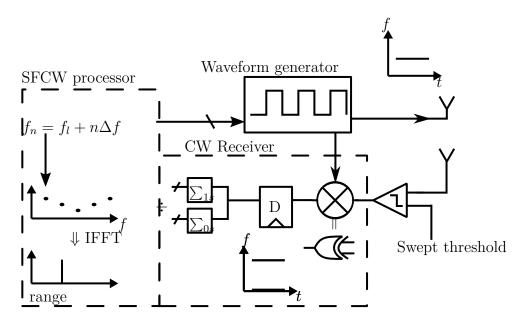

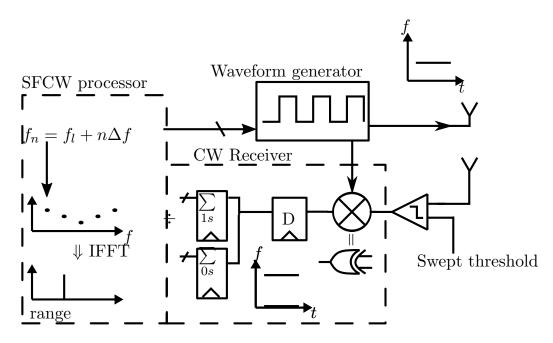

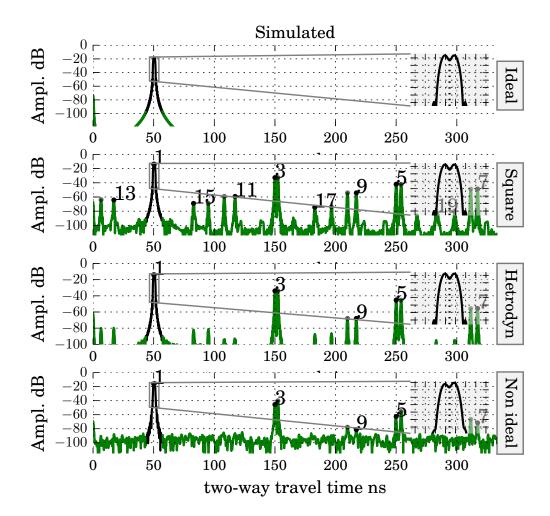

|              | B.4          | Stepped Frequency Continuous Wave (SFCW)           | 167 |

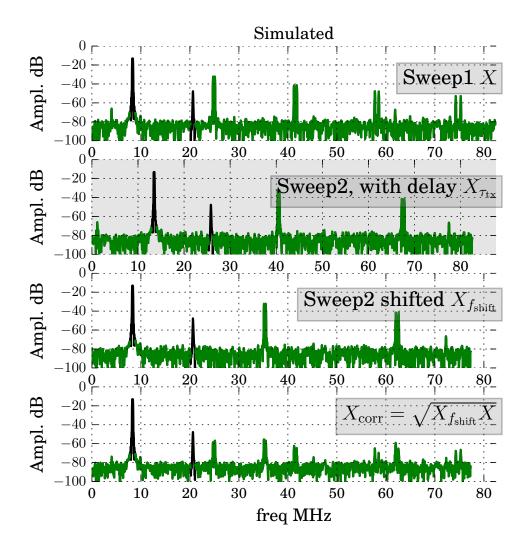

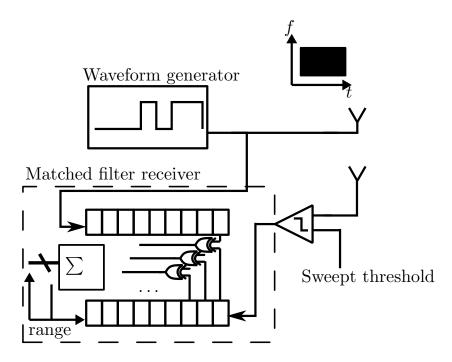

|              | B.5          | Correlation based radar                            | 171 |

|              | B.6          | Conclusion                                         | 172 |

| $\mathbf{C}$ | Pap          | oer III                                            | 175 |

|              | C.1          | Introduction                                       | 177 |

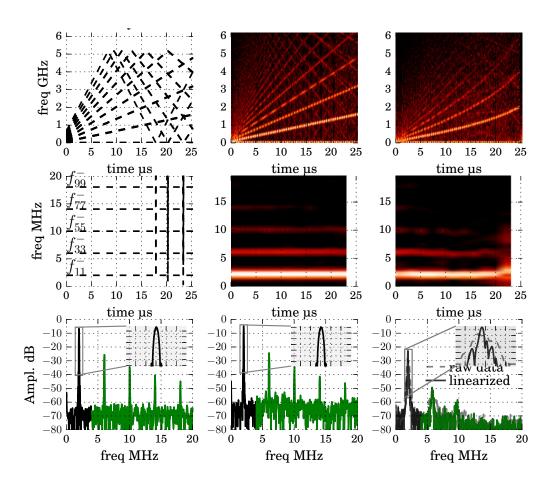

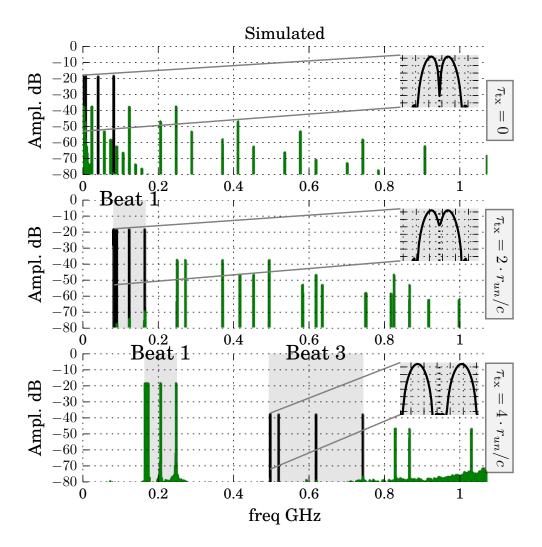

|              | C.2          | Analytical mixing of frequency modulated waveforms | 180 |

|              |              | C.2.1 Analytical FMCW                              | 181 |

|              |              | C.2.2 Analytical CW/SFCW                           | 184 |

|              | C.3          | Dealing with harmonics                             | 186 |

|              |              | C.3.1 Moving out of band                           | 186 |

|              |              | C.3.2 Resolving in band ambiguity                  | 187 |

|              | C.4          | Stepped Frequency Continuous Wave (SFCW)           | 191 |

|              | C.5          | Correlation based radar                            | 194 |

|              | C.6          | Unmodulated pulsed radar                           | 195 |

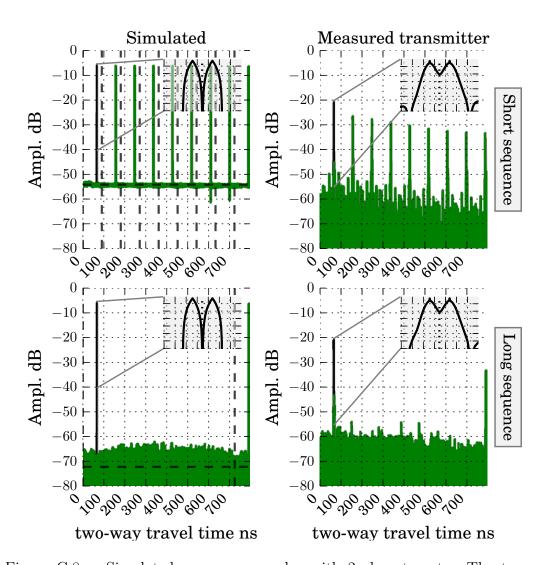

|              | C.7          | Measurements                                       | 197 |

|              |              | C.7.1 FMCW linearity correction                    | 199 |

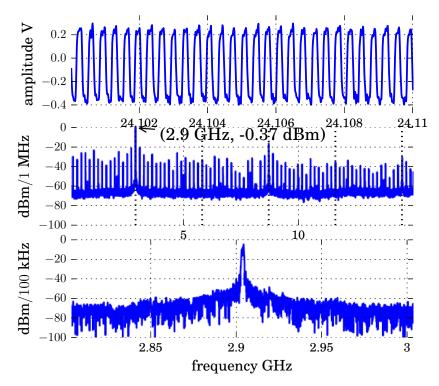

|              |              | C.7.2 XOR gate as a digital mixer                  | 200 |

|              |              | C.7.3 Full system measurements                     | 200 |

|              | C.8          | Discussion                                         | 203 |

|              | $C_{0}$      | Conclusion                                         | 204 |

| D  | Pap | er IV   |              |          |        |     |      |     |      |  |  |  |  | 2   | 209 |

|----|-----|---------|--------------|----------|--------|-----|------|-----|------|--|--|--|--|-----|-----|

|    | D.1 | Introdu | action       |          |        |     |      |     |      |  |  |  |  | . 2 | 211 |

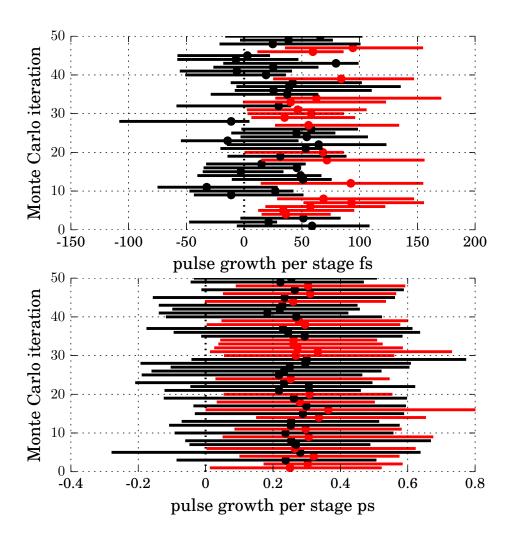

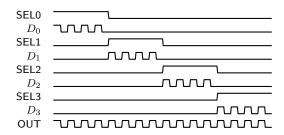

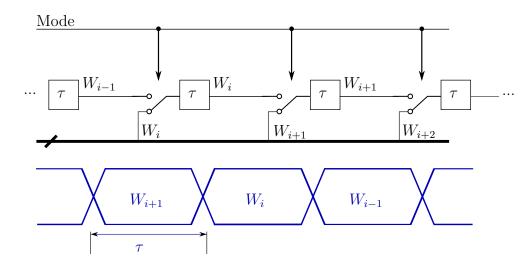

|    | D.2 | WP as   | delay gener  | rator .  |        |     |      |     |      |  |  |  |  | . 4 | 212 |

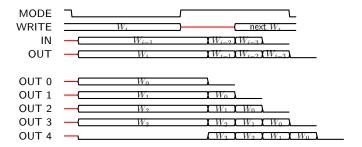

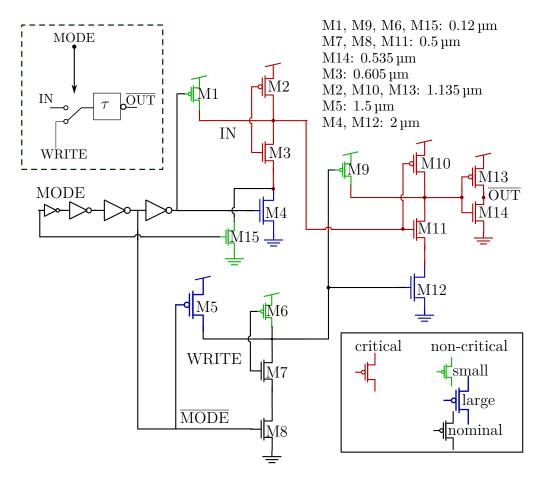

|    | D.3 | Implem  | nenting the  | MUX      |        |     |      |     |      |  |  |  |  | . 4 | 214 |

|    |     | D.3.1   | Choice of c  | ircuit   |        |     |      |     |      |  |  |  |  | . 4 | 214 |

|    |     | D.3.2   | Sizing for t | he criti | ical t | rai | ısit | ioi | ns . |  |  |  |  | . 2 | 214 |

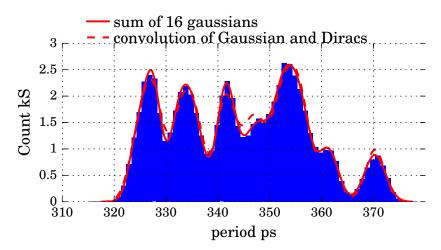

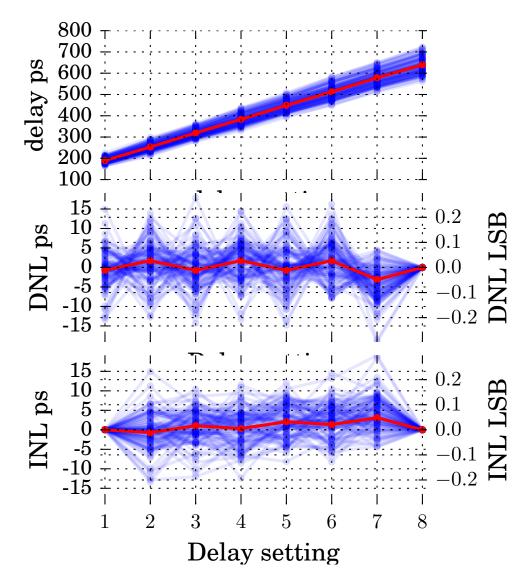

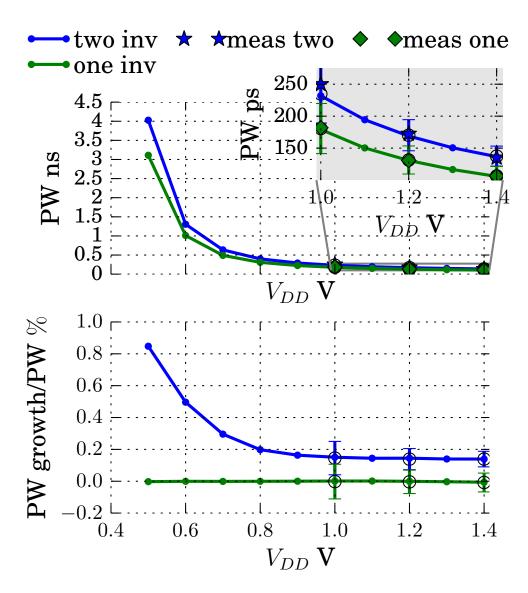

|    | D.4 | Charac  | terization   |          |        |     |      |     |      |  |  |  |  | . 2 | 217 |

|    |     | D.4.1   | N/P ratio    |          |        |     |      |     |      |  |  |  |  | . 4 | 218 |

|    |     | D.4.2   | Supply sen   | sitivity |        |     |      |     |      |  |  |  |  | . 4 | 218 |

|    |     | D.4.3   | Back-gate    | uning    |        |     |      |     |      |  |  |  |  | . 4 | 220 |

|    |     | D.4.4   | Comparison   | n        |        |     |      |     |      |  |  |  |  | . 2 | 221 |

|    | D.5 | Conclu  | sion         |          |        |     |      |     |      |  |  |  |  | . 2 | 221 |

|    |     |         |              |          |        |     |      |     |      |  |  |  |  |     |     |

| ΙI | ΙĒ  | Refere  | nces         |          |        |     |      |     |      |  |  |  |  | 2   | 25  |

# Nomenclature

ADC Analog-to-Digital Converter

AWGN Additive white Gaussian noise

BW Bandwidth

CAD Computer-Aided Design

CIC Cascaded Integrator-Comb

CML Current Mode Logic

CMOS Complementary metal-oxide-semiconductor

COTS Commercial off-the-shelf

CW Continuous-Wave

DAC Digital-to-Analog Converter

DCO Digitally Controlled Oscillator

DDS Direct Digital Synthesizer

DTC Digital-to-Time Converter

ENOB Effective Number Of Bits

FMCW Frequency-Modulated Continuous-Wave

FPGA Field-Programmable Gate Array

GPR Ground Penetrating Radar

HDL Hardware Description Language

LFM Linear Frequency-Modulated

LFSR Linear Feedback Shift Register

LNA Low Noise Amplifier

mux multiplexer

OSR OverSampling Rate

PA Power amplifier

PDM Pulse-Density Modulation

PLL Phase Locked Loop

PRF Pulse Repetition Frequency

PSD Power Spectral Density

PVT Process, Voltage and Temperature

PW Pulse-Width

RMS Root Mean Square

SAR Synthetic Aperture Radar

SerDes Serializer/Deserializer

SFCW Stepped-Frequency Continuous-Wave

SFDR Spurious Free Dynamic Range

SNDR Signal to Noise and Distortion Ratio

SNR Signal to Noise Ratio

SPI Serial Peripheral Interface bus

SQNR Signal to Quantization Noise Ratio

SR Stochastic Resonance

SSR Suprathreshold Stochastic Resonance

${\rm TDC} \qquad {\rm Time\text{-}to\text{-}Digital\ Converter}$

VCO Voltage Controlled Oscillator

WP Wave-Pipeline

## Part I

# Thesis

# Chapter 1

# The first chapter

When interfacing with the real world, an ideal analog circuit can track the environment with infinite speed and infinite precision. The traditional challenge is then to build an analog circuit that is as close to ideal as we need. This usually leads to a circuit that can handle a specific bandwidth (speed) at a specific input range and limited by a noise level. The analog circuit requirements are then traded off between cost (technology), power consumption (vs noise), size/portability, existing vs custom components and so on. There is no doubt that fully analog circuits can achieve remarkable feats. Many of the digital devices we take for granted today started out as a fully analog device, such as clocks, film cameras, record players and radios.

Today clocks, cameras, music players and radios take on an increasing number of digital components, where we "interface" the analog world with Analog-to-Digital Converter (ADC) and Digital-to-Analog Converter (DAC). The first advantage of going digital is in storage, analog storage mediums are lossy and may degrade with time and playback/copy, whereas digital storage promises to be cheaper, smaller and more reliable. The biggest advantage is however the flexibility, once a signal is digitized, we can not only store the information for future playback, but we can process (modify, merge and simplify) and we can easily exchange/share across the world by connecting to

the internet. In addition, digital design, allows for a greater abstraction layer between the designer and complex electrical effects; enabling a much larger degree of automation and re-use of multi-purposes digital building blocks than feasible in analog design.

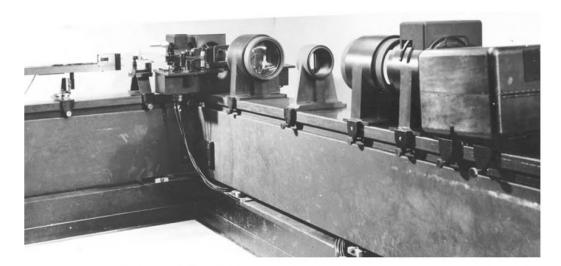

Radar systems have evolved in the same manner as consumer devices, from the first fully analog radar systems that outputs to a Cathode-ray tube PPI display, to systems that does an increasing amount of processing and storage in the digital domain. Processing and storage can be achieved in the analog domain, such as the early Synthetic Aperture Radar (SAR) systems that recorded to film and used optics for the processing [ULB+14]. Optical processing of SAR data was commonplace starting in the 1960s and extending into the early 1990s [Joh06], but is now completely replaced by digital processing. Digital processing allows for increasingly sophisticated image processing, without the bulk and imperfections through an optical system. Figure 1.1 shows one such optical system and the caption confirms what we stated above, that an analog system can be bulky, expensive and application specific.

Fig. 4.3. Optical processor at Willow Run, c.1960. The large aperture optics were mounted on steel slabs fastened to granite supports and steel I-beams. The large defect-free lenses cost some \$10,000 to design and a further \$10,000 to fabricate, and were optimized for the wavelength of mercury green light (546 nm) (Leith collection).

Figure 1.1: SAR optical processing from the 1960s [Joh06]. Permission to reproduce this image in this thesis given by Oxford University Press May 2017. All other uses restricted.

Radar transmitters started out as simple spark gaps, but have evolved to sophisticated waveform generators that allow fine control over the waveforms frequency content. Digital transmitters can be built as a Direct Digital Synthesizer (DDS), which allow for flexible waveform synthesis with precise phase control. A DDS based Frequency-Modulated Continuous-Wave (FMCW) radar is planned for both the NASA 2020 rover and Chinese 2020 rover [HBB<sup>+</sup>15, ZSJ<sup>+</sup>16]. Both solutions rely on frequency multiplication; as a DDS is limited in its maximum output frequency, but its digital nature ensures reliability and high accuracy.

A previously analog intensive technique, a Phase Locked Loop (PLL), is also being digitized as seen by [Sta11, BVGC10]. A PLL can directly generate higher frequencies than a DDS, where the DDS is limited by the clock rate, a PLL is limited by the frequency range of the oscillator. The disadvantage of a PLL is that it lacks the same phase accuracy as a DDS and requires a lock-time when changing the frequency. Hybrid systems combining DDS as a reference to a PLL are appearing [Gol00, WSJ06], aiming to combine the advantages of both approaches.

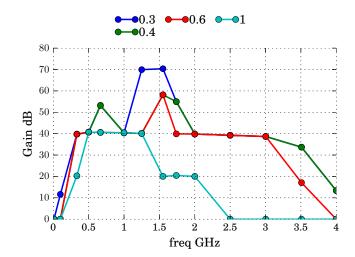

In this thesis, we propose a digital frequency modulated radar, that can take full advantage of the rapid advancement of digital technologies. By restricting the signal to a single bit and removing the high frequency clock, we get something similar to a DDS, but operated at a much higher speed. This allows direct frequency generation, only limited in speed, by the (decreasing) gate delay of the technology.

A single bit/square wave signal is rich in harmonics and must be carefully accounted for in the system design process. Traditionally, non-linearity (harmonics) is minimized on the hardware level by careful component selection and filtering, the remaining harmonics are either looked at as distortion (a time domain view often seen in ADC literature) or intermodulation. We will here take a system approach where we carefully analyses how the harmonics affect the system output and how we can circumvent or even utilize the harmonics. These solutions rely on adjustable delays, something which is readily available when working with single bit digital signals, opening up some interesting signal processing solutions that allow the harmonics to be present in every component of the design.

In addition, due to the flexibility of a digital circuit, we also show possible implementations of non-frequency modulated radars, both pulsed time of flight and noise based correlator architectures. We also propose and analyze

multiple baseband solutions, that again leverages the single bit digital nature of the signal.

## 1.1 Introduction to the proposed radar

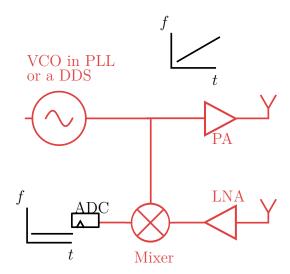

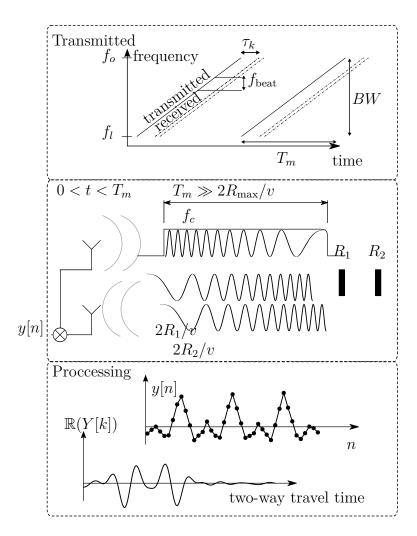

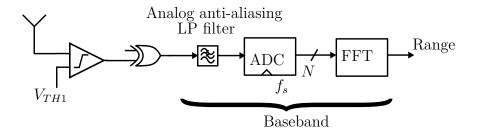

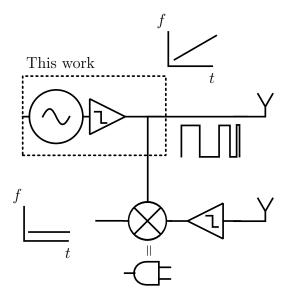

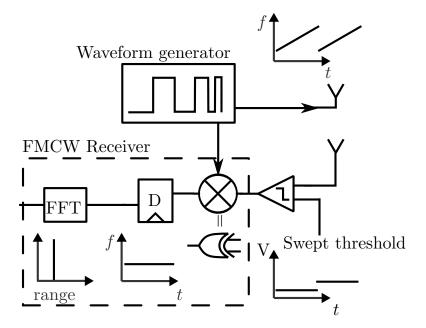

We will here walk through the thought process of converting a traditional analog frequency modulated radar into a fully digital radar solution that will benefit from modern digital technologies. The Frequency-Modulated Continuous-Wave (FMCW) principle is explained in more detail in the next chapter, but as seen in figure 1.2 the architecture simply requires a frequency source, a mixer, an ADC and some amplifiers. Readers unfamiliar with these concepts may want to skip ahead to chapter 2.

### 1.1.1 Analog radar

Figure 1.2: Example traditional analog FMCW radar, analog components in red. A VCO (Voltage Controlled Oscillator) is controlled by a PLL (Phase Locked Loop) to generate a low phase noise, linear chirp. A linear PA (Power amplifier) amplifies the transmitted signal while the linear LNA (Low Noise Amplifier) amplifies the returns. The transmitted and received signal is mixed and digitized by a high speed multi–bit ADC (Analog to Digital Converter). Filters not shown.

We note that the only digital component in figure 1.2 is the ADC, and as we will discuss further in chapter 5, even the ADC is not ideally suited for modern digital integration. As for the remaining components, we have mentioned that there is work to digitize the frequency source, by either a digital PLL or by DDS, but these are still circuit blocks with an analog output. Both PAs and LNAs can be integrated in modern Complementary metal-oxide-semiconductor (CMOS), but suffer from poor output power, linearity and noise figure compared to alternative (more expensive) technologies such as GaAs and SiGe.

In a traditional analog design, we want all of the circuit blocks to be linear. Linearity is the basis of linear circuit analysis, giving us superposition and simple, straight forward characterization and measurements techniques. Unfortunately, no real active circuit block will ever be fully linear (for all inputs), as any real active circuit will always eventually clip in amplitude. This becomes even more challenging in modern digital technologies as the supply voltage goes down. A workaround for non-linear blocks can be a filter on the output and analog intensive solutions often need multiple filters throughout the design. Filters are typically in-flexible and depending on frequency not suited for direct on-chip integration.

It should be mentioned that a mixer is a non-linear component, as it produces output frequencies not present on the inputs. That said, a mixer is usually followed by a filter, leaving either the sum or difference only. In addition, one of the inputs either have a single constant frequency or a single modulated frequency signal (as in figure 1.2) allowing us to treat the mixing operation as input-output linear, as it works simply as a frequency shifter. By this, we mean that any linear combination of input signals, will give a scaled (and shifted!) output signal. This shift can be time dependent, as in an FMCW radar.

We will therefore, at times, refer to a mixer as a linear component. In addition, the reader should not confuse a linear chirp or sweep, with a linear component. A linear chirp simply follows a straight line f(t) = a + bt (in the time-frequency domain), while a linear component satisfy H(ax + y) = aH(x) + H(y). Where H is the components transfer function, a and b are constants and x and y are either voltages or currents.

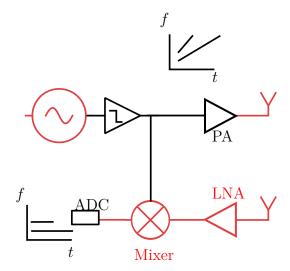

Figure 1.3: Limiting the transmitted signal to two levels. As will be discussed in section 2.2.1 the only information we care about in the transmitter is the zero crossings. We no longer care if the PA is linear and so we can view it as digital.

### 1.1.2 Digital transmitter

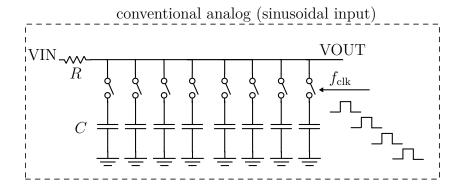

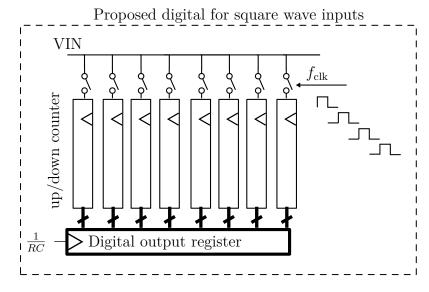

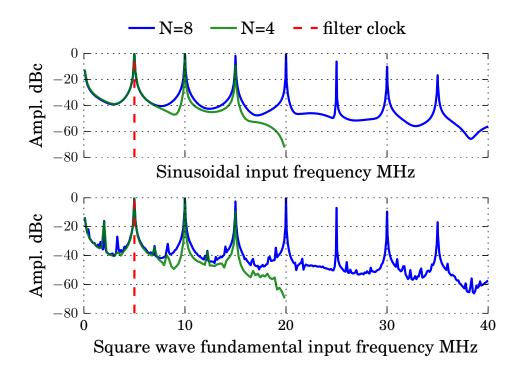

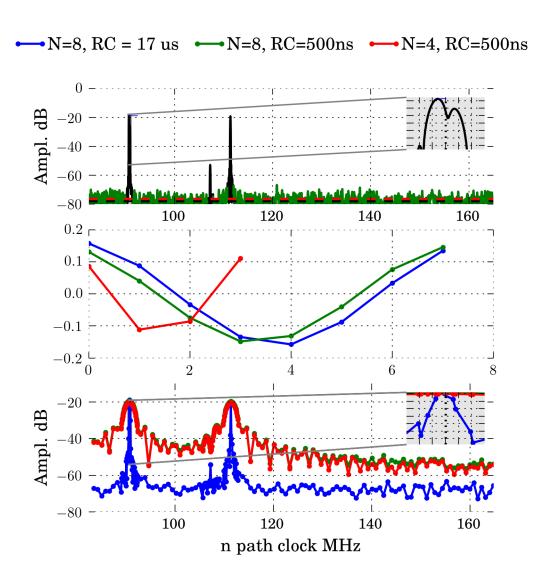

As a starting block, we begin by replacing the analog frequency source for a (digital) amplitude clipped version as shown in figure 1.3. We will discuss this transition more in section 2.2.1, but the essence is that we are not doing any amplitude modulation and we are only interested in a single instantaneous frequency, so we can safely amplitude limit the transmitted signal. If the transmitter has a bandwidth that is greater than an octave, then we have introduced harmonics both in the transmitted signal and in the final mixer output. The only analog solution for removing these is a tunable/selectable filter bank for each octave, before the mixer on at least 1 of the mixer inputs.

The filter bank only needs to remove harmonics on 1 of the mixer inputs since the harmonics we wish to remove is the mixing between harmonics on each of the inputs; as we will see shortly in section 1.1.5. The Power amplifier (PA) now has a digital input and can be class-E/class-F if the bandwidth is sufficiently low.

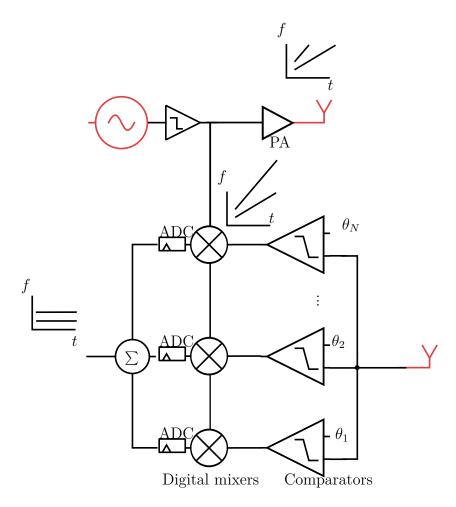

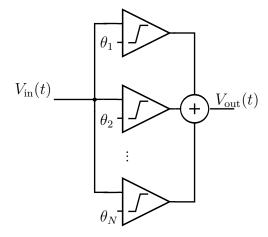

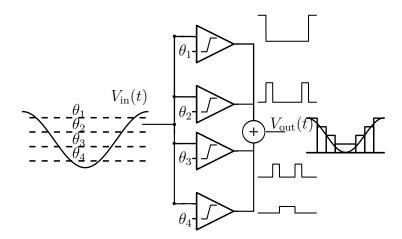

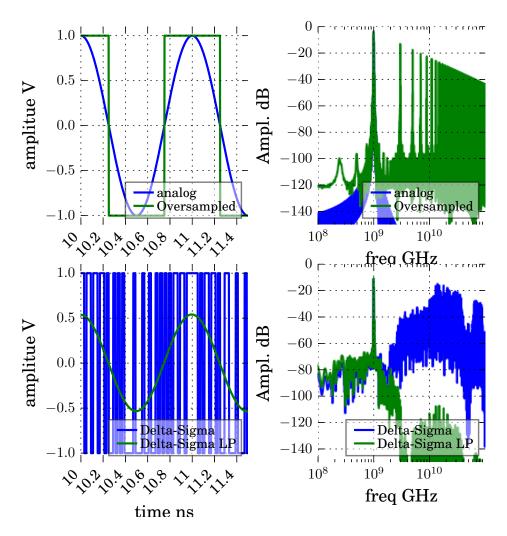

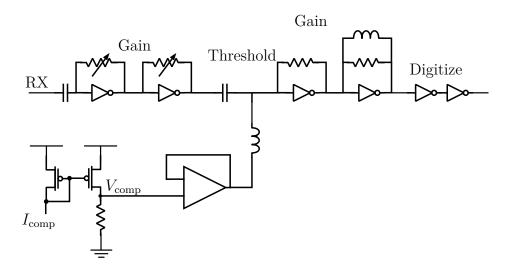

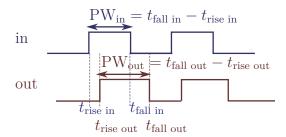

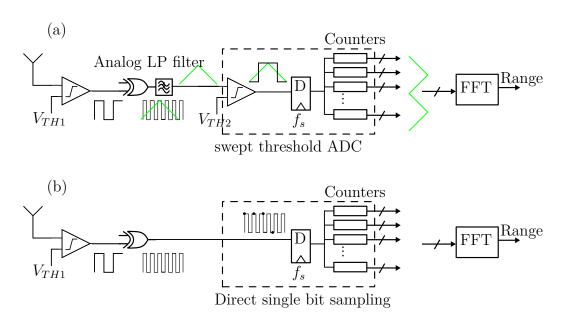

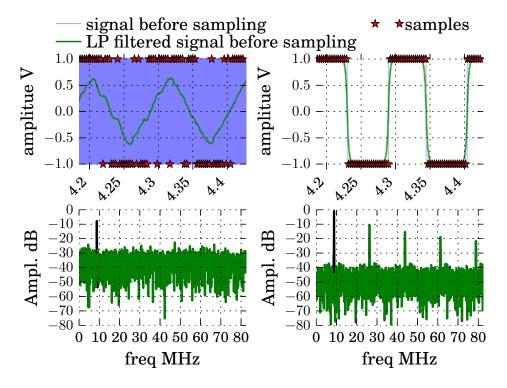

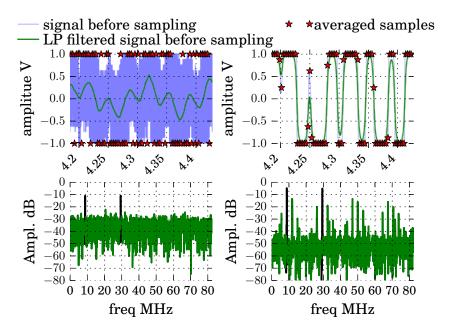

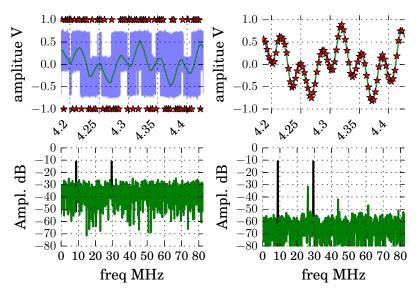

Figure 1.4: Principle of a swept threshold receiver, where each comparator, mixer and sampler can be done serially if the scene is stationary or, as depicted here, in parallel. If the comparator levels  $\theta_i$  ( $i \in [1, N]$ ) are fixed, linearly separated levels, we have the equivalence of a flash-ADC. Due to linearity of the operations, the processing (mixing and sampling) can either be done before averaging (as shown here) or after, which would be the case for a traditional flash ADC.

#### 1.1.3 Digital transmitter and receiver

To digitize the receiver, we must (as, again, will be detailed in section 2.2) use a number of threshold levels; as simply amplitude limiting the received signal yields a non-linear system. This arrangement is shown in figure 1.4. For low noise scenarios, these threshold levels should be linearly distributed, covering the signals amplitude peak-to-peak level. As will be seen, the levels can also be fixed at the signals mean, if the noise is sufficiently high (instantaneous noise level comparable or greater than the signal level).

At this point we not only have a digital receiver, we also have a unique opportunity to process the signal while it is still in its single bit form. This is illustrated in figure 1.4 where we do the mixing and sampling before we combine the information obtained by the different threshold levels. We will use this extensively in Paper II and Paper III to implement a wide range of receivers using the single bit bitstream.

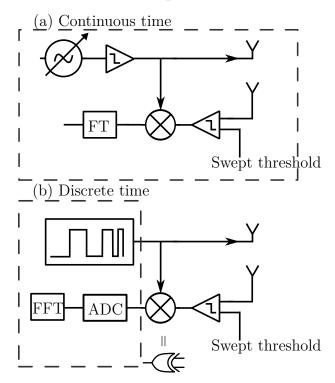

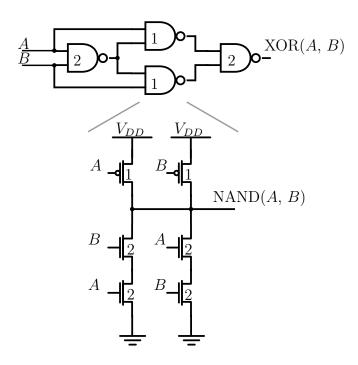

The mixing operation is much simpler in implementation for a single bit signal than a multi-bit digital signal. We can (1) do the operation in continuous time as there is no synchronization between bits required, (2) implement it as a single digital gate (a XOR gate, as will be shown in section 5.3.1) and (3) have most of the benefits of a digital component which is robustness, general purpose, scalable speed, area and power footprint. The single bit decomposition is explored in detail by Tsividis [Tsi06].

We now notice a small but significant change in the harmonics when going from figure 1.4 to figure 1.5. In the first case, the harmonics will only appear in the beat spectrum if the bandwidth of the system is greater than one octave and even in this case it can be removed if a tunable filter is applied. When the receiver is digital, the situation changes as we are effectively re-creating the harmonics on the receiver side. In essence, the digital gates will have sufficient bandwidth to drive the signal to saturation and give harmonics. And so in figure 1.5, the mixer(s) will have harmonics on both inputs, regardless of the transmit PA and channel and regardless of whether the fundamental is single or multi-octave. This is good news, as we can utilize the harmonics constructively.

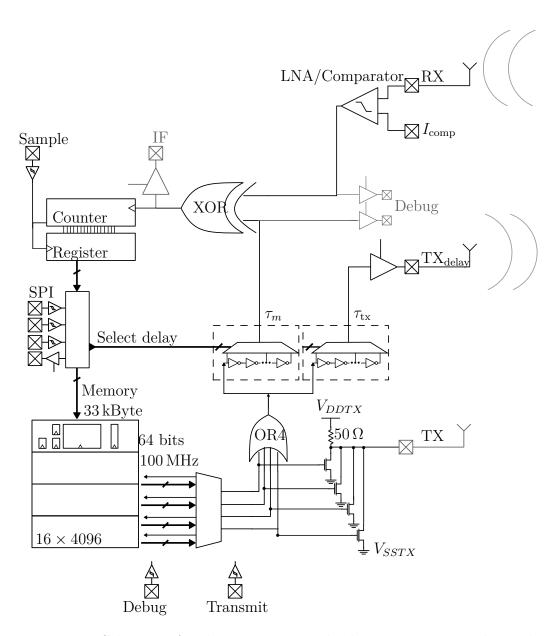

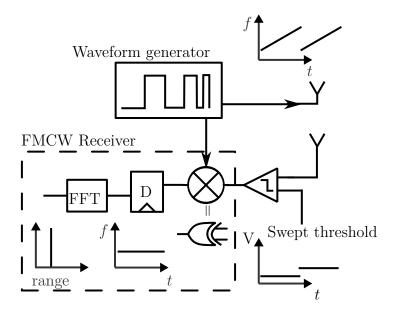

## 1.1.4 Proposed radar solution

We are now ready to arrive at figure 1.5. For maximum flexibility, the transmitted waveform is computed offline, in software, allowing us complete free-

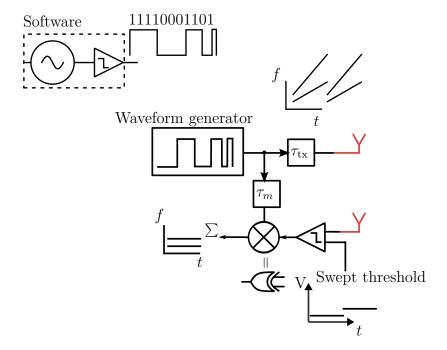

Figure 1.5: The proposed all digital FMCW radar solution. The quantization of the transmitted waveform is now done in software and the transmitter is a digital serializer. The receiver is a single swept threshold comparator with a digital mixer (xor gate). Two adjustable delays inserted in the transmitter and mixing path. The transmitting path ( $\tau_{\rm tx}$ ) can be used to separate the harmonics from the fundamental by lengthening the two-way travel time, while  $\tau_m$  can be utilized to shorten the time and align the transmitted signal up to the received.

dom when generating the transmitted single bit signal. This flexibility will be a cornerstone in Paper II and Paper III as it allows us not only a frequency modulated waveform but also pulses and noise sequences. As will be discussed in the papers, the adjustable delay  $\tau_{\rm tx}$  allows us to separate the harmonics from the fundamental by ensuring we do not get any scatters appearing to be close to the radar. This gives us a single band for the fundamental and a separate band for the harmonics.

The parallel receiver structure in figure 1.4 is now replaced with a single swept threshold receiver. As we will see in the implementation chapter, our comparator is quite bulky and, as it has two analog inputs, our only analog block. So at least for our prototype, employing multiple parallel receivers was not economical.

A swept threshold receiver has some interesting properties that we will explore further in section 2.2 and chapter 3. In low noise, the flash-ADC analogous fits well for a stationary scene, while some interesting effects arise when the noise is increased (and is independent between runs). With a fixed threshold, the system exhibit a Stochastic Resonance (SR) phenomena (coined Suprathreshold Stochastic Resonance (SSR)), where the performance peaks at a non-zero noise level. In addition, as the noise becomes comparable or larger than the signal, a performance very close to an ideal analog system is observed. This peculiarity of a swept threshold receiver is explored by the author that coined the term, Hjortland [HWL+06] in his Ph.D. [Hjo16]. Stochastic Resonance is explained well by Mcdonnel [MA09] which hold a PhD on the subject [McD06], while an introduction to SSR can be found by Stocks [Sto00]. Performance characterization in noise when correlating is studied by Watts [Wat62], as will be discussed on page 28.

The same occurs if we compare our single bit system to a multi-bit system, where in excessive noise the multi-bit system can be said to be "wasteful" as the extra bits produced does not carry any meaningful information about the signal, it simply represents the signal+noise with a high degree of accuracy. This observation can be used in the radar system design, so that we intentionally work close or below the thermal limit, to conserve energy both on the transmitter and on the receive side.

The flexibility of a discrete time bitstream transmitter does come at a price. For our frequency source, the discrete time nature does imply a finite time resolution which leads to an ambiguous frequency spectrum and, due to the square wave nature, aliasing. We point out this aliasing in the papers

and a work-around by dithering is presented in section 3.2.1.

#### 1.1.5 Beneficial harmonics

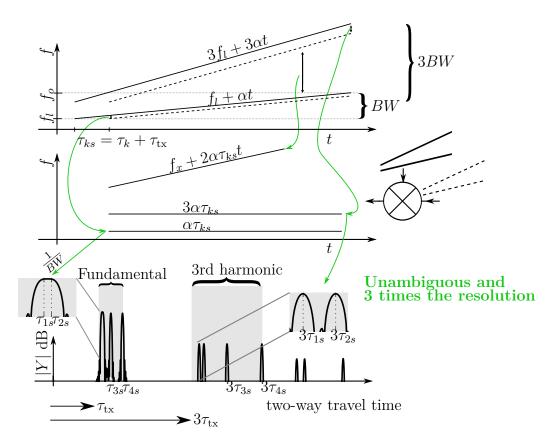

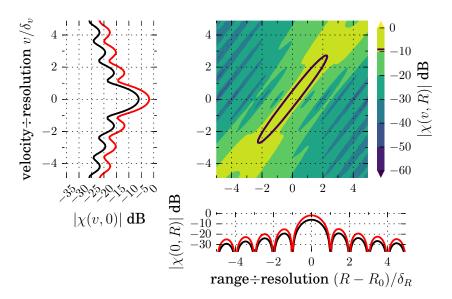

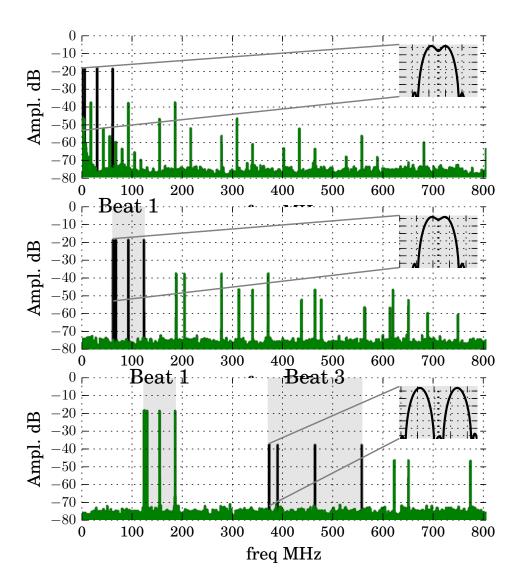

We have in the above talked about harmonics in the radars range spectrum. To show why the harmonics appear in the radar output, the solution and also a potential benefit, we here present figure 1.6 which attempts to address all of the above.

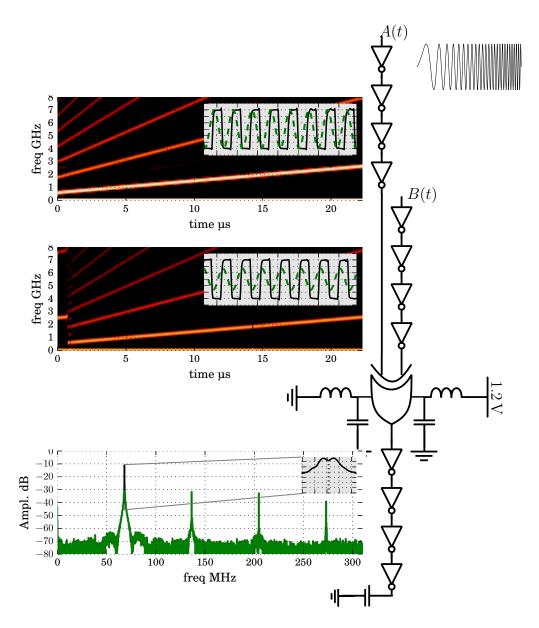

Figure 1.6: Top: a linear frequency sweep with third harmonic, transmitted signal in black and received in stippled. Middle: Mixer difference, showing mixing of the fundamental, 3rd harmonics and one of the intermixing products. Bottom: Resulting beat spectrum when using a delay  $\tau_{\rm tx}$  in the channel path to separate the third harmonic for a unambiguous view and looking at the harmonics for improved resolution. Bottom panel shows 4 targets of equal amplitude at two-way travel times  $\{\tau_1, \tau_2, \tau_3, \tau_4\}$  where the fundamental becomes shifted by  $\tau_{\rm tx}$ . Note that the top panels only show a single target  $\tau_k$ , for clarity.

Figure 1.6 starts off with the inputs to the mixer, one time delayed with respect to the other by the two-way travel time to the target  $\tau_k$  plus the radar transmit path delay  $\tau_{tx}$ , giving the shorthand

$$\tau_{ks} \equiv \tau_k + \tau_{tx}. \tag{1.1}$$

As the signal is digital it has harmonics, simplified here to only the third harmonic. Higher order odd harmonics will also be present and non-ideal circuits will also have even order harmonics, but the principle in figure 1.6 holds.

Mixing the reference and delayed version and looking at the mixer difference, we obtain the lines in the middle panel of figure 1.6. The frequency difference of the fundamentals of each input create the classical FMCW range response which is directly proportional to the two-way travel time  $(\alpha \tau_{ks})$ . In an equivalent manner, mixing the third harmonics with each other, creates another harmonic response at  $3\alpha \tau_{ks}$ . In addition to these, we will have a number of cross-products. These and other details are treated more carefully in Paper III. One of the cross terms is drawn here with a slope of  $2\alpha \tau_{ks}$ . Care must be taken such that the cross terms are easy to filter out and the reader is again encouraged to see Paper III.

#### 1.1.6 Summary

Harmonics can be reduced or eliminated by filtering or by dithering/staggering. One of the key findings in this work, is that the harmonics are not necessarily unwanted and we can (a) shift them outside the band of interest, creating an unambiguous view, and (b) as the harmonics cover a wider bandwidth, this gives us improved resolution; without needing to transmit and receive this wider bandwidth.

By dithering away the harmonics, we lose the potential advantage and we make it much more difficult to shift the unwanted part out of the band of interest, making the case for keeping the predictable harmonics as opposed to whitening and randomizing the energy.

The findings in this work also applies to traditional analog radar systems that want to explore multi-octave bandwidths and systems that struggles with the inevitable non-linearity of active components. The only requirement to utilize the harmonics (if they are present in the system) is some way of offsetting (in time or frequency) the transmitter and mixing path.

We should also point out that digitizing the transmitter can be done independently of digitizing the receiver. The concept drawn in figure 1.3, where only the transmitter is digital, still provides some of the benefits presented in this work and avoids the multiple-sweeps of a swept threshold receiver.

## 1.2 Applications

Cheap, digital radar solutions, have countless applications as short-range radar sensors. They can also conceivably serve as "backend" for traditional long-range radar systems. These systems will typically require more expensive and power-hungry high-power amplifiers on the transmit side and/or low noise amplifiers on the receiver side, but can still benefit from a digital backend for waveform agility and adaptivity. Cheap digital radars are ideal for beamforming/imaging applications, where one can duplicate and use a single chip per antenna element, or co-integrate several transmitter/receiver channels on the same die.

Low sensitivity and movement sensitive radars can be used as simple presence detection for lighting and air-condition control, and simple CW based radars mounted inside light-bulbs are already available commercially. These CW modules get some interesting reviews, as the light bulb may detect your presence before you enter the room (since it views you through the door). It therefore appears to the user as if the light is always on, which may even be the case, as some users report sensitivity to moving trees outside.

More reliable radar sensors, that can also get the range and not just movement and with clever on-chip digital signal processing; can have great benefits for elderly monitoring or smart-homes, where a radar sensor is less privacy intrusive than a camera and can provide through wall-monitoring. Conceivably these monitoring radars can not only provide detection of presence and movement (and hence unusual activity) but also, falling instances and medical monitoring of the gait, heart and breathing pattern [CRC+11].

Radar sensors also have several applications within environmental monitoring, chiefly looking for water content (high dielectric contrast) in soil, ice or even farmland. Or as metal/conductor detection for land-mines, re-bars in concrete or archaeological surveys. The same Ground Penetrating Radar (GPR) imaging techniques can also be applied to the human body, for breast-cancer detection [BBGN12] and even brain-imaging [TKL16, LNLC15].

# Chapter 2

# Background

#### 2.1 Radar architecture fundamentals

This chapter introduces the basic radar architectures in use today, these architectures will be re-visited in Paper III in a single bit form, but is here presented in a more idealized manner; to cover the basic principle.

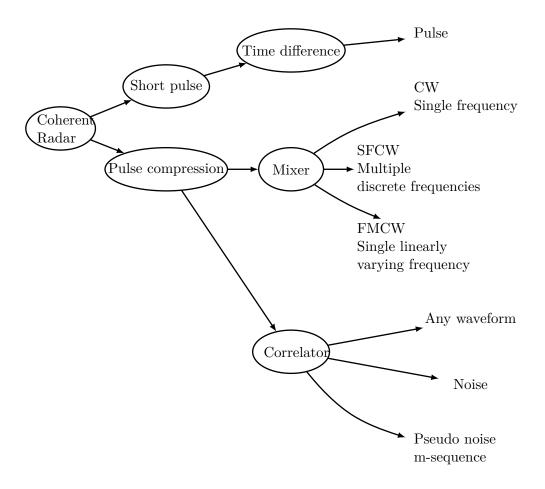

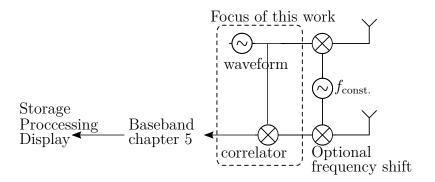

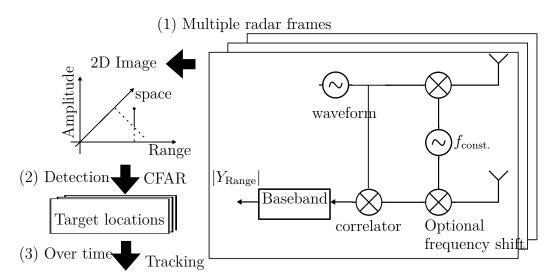

We categorize different radaR architecture based on the mechanism used to extract the Range; be it by time difference, mixer or correlator as shown in figure 2.1. All of the architectures will yield the same end result, where the performance will ideally depend only on the time and bandwidth, but will differ in implementation details and challenges.

We restrict ourselves to coherent radars, where we define a coherent radar; as a radar that retains the full signal, that is, we avoid extracting only the amplitude, we also retain the phase. The coherent assumption is critical for the sweep-threshold receiver as we need that synchronization to recreate the incoming signal. A coherent result is also beneficial for further processing of the radar return, allowing us to use the phase when comparing two radar frames separated either in space (2D imaging) or time (movement/speed estimation).

This chapter starts with the Pulsed time-of-flight radar, which is the most intuitive radar architecture, before introducing a family of radar architectures that can transmit and receive continuously. These either rely on a frequency modulation and a mixer or a full correlation circuit, to extract the transfer function of the environment.

Figure 2.1 shows an overview of the radar architectures covered in this chapter, these architectures will be presented in a single bit form in Paper

III but where here focus on the idealized principle. A pulsed system extracts the range by looking at the time-difference between when the pulse was transmitted and when it was received. Pulse compression radars on the other hand, extract the range from a beat frequency (in the FMCW case) or as an index-lag in the correlation; of a correlator based radar.

Figure 2.1: Categorizing all of the radar architectures discussed in this thesis; based on the waveform and mechanism to extract the range (time of flight).

Hybrids between these systems are possible, which can either be looked at as a pulsed radar with coding or as a time-gated pulse-compression radar. Both in an attempt to get the best of both worlds. The main motivation for not continuously transmitting being that the transmitter should be off when receiving (at least for the direct coupling), to avoid saturating the receiver.

A detailed analysis of these hybrid techniques is beyond the scope of this thesis.

#### 2.1.1 Pulsed time-of-flight radar

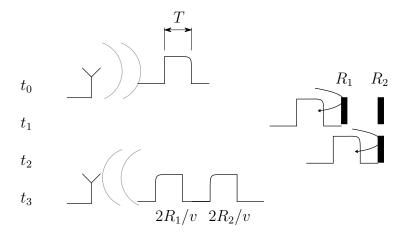

Figure 2.2: Principle of a pulsed radar with two equal reflectors and a sufficiently short pulse length so that the receiver gets two separate pulses.

The first and most intuitive radar type is a pulsed radar where the time-of-flight is extracted by the time difference between transmission and reception. As illustrated in figure 2.2, the transmitted pulse is reflected from two equal reflectors at a radial distance  $R_1$  and  $R_2$  respectively. As the pulse width T = 1/BW is shorter than the two-way travel time between the targets we say that these targets are "resolved" as we can distinctly detect two pulses on the receiver. The required pulse width can be formulated to give a range resolution of [ULB+14]

$$R_2 - R_1 = \Delta R = \frac{vT}{2} = \frac{v}{2BW}$$

(2.1)

where v is the speed-of-light in the medium, T the pulse length and BW = 1/T is the bandwidth. We will in this work, without loss of generality, assume the medium is vacuum or air and hence  $v = c \approx 3 \times 10^8 \,\mathrm{m/s}$ .

To change the frequency spectrum of the pulse, the pulse can be upconverted to a sine-wave carrier before reception and down-converted on the receiver (a process known as heterodyning). This does however *not* change

the principle in figure 2.2 and we will for brevity exclusively deal with non-up-converted waveforms in this thesis. The choice of carrier frequency will have a major impact on the front-end, including amplifiers, antenna (size) and the physical objects that can be characterized. Carrier frequency is hence important when a given application is envisioned; this thesis tries to be more general and focuses on the traditional versus single bit radar aspect without the constraint of any particular application.

Pulsed time-of-flight radar systems are mentioned in this thesis for the sake of completeness, our main focus is on radars that code the transmitted waveform and correlate on the receiver. In addition, as mentioned, we will neglect any frequency shift as illustrated in the system diagram of figure 2.3. It should be mentioned that the bandwidth in the resolution equation (2.1), is the bandwidth "on-air" and so, a heterodyne radar with up-and-down conversion can usually provide finer range separation at the cost of hardware complexity and increased environment attenuation at higher frequencies.

Figure 2.3: A complete radar system, where this thesis is focused mainly on the waveform and correlation method.

## 2.1.2 Continuous-Wave (CW) Radar

One of the fundamental disadvantages of the naive pulsed radar, is that if we transmit pulses too rapidly (before all of the reflected pulses have been received), we will have a hard time distinguishing between what we just transmitted and what is reflected from some far-off target. We call this a "range ambiguity", which is a very important consideration when selecting radar architecture and parameters. When comparing a pulsed radar to a radar that is continuously transmitting and assuming a given peak transmitted

power, receiver gain and noise limit, the only way to increase the sensitivity and range in a given time slot is to increase the percentage of time we are transmitting energy. A pulse radar will therefore need to tradeoff the pulse length (which gives the resolution) and the transmitted energy.

The idea behind a correlation radar, is that we can code the signal that is transmitted and look for that code in the received signal. Hence, we can transmit continuously, or at least a larger percentage of the time; increasing our sensitivity without sacrificing bandwidth.

We will in this thesis, use the Continuous-Wave (CW) term for a constant frequency modulated radar that transmits continuously. To explore the continuous-wave concept, we therefore write

$$y_{\text{CW}}(t) = A\cos(\omega_0 t) = A\cos(2\pi f_0 t) = A\cos\left(2\pi \frac{\lambda_0}{c}t\right)$$

(2.2)

which, results in a received scaled and delayed copy for reflector k (assumed stationary)

$$x_{\text{CWk}} = B_k \cos(\omega_0(t - \tau_k)) \tag{2.3}$$

In the above,  $\omega_0 = 2\pi f_0$  is the angular frequency,  $\lambda_0$  the wavelength and c the speed-of-light in the medium.

The received amplitude  $B_k$  can be found by accounting for the transmitted amplitude A, the antenna gain, the path loss (which will have at least an  $1/R^4$  spreading loss), the reflected amplitude, polarization and the receiver gain. For realistic scenes, estimating the received signal can become its own research topic, which we will avoid in this thesis, by dealing with scatterers of a given amplitude  $B_k$  and two-way-travel time  $\tau_k$  exclusively; as this is sufficient to deal with any linear scenes with stationary targets. Though it is important to keep in mind, that  $B_k$  is likely frequency dependent.

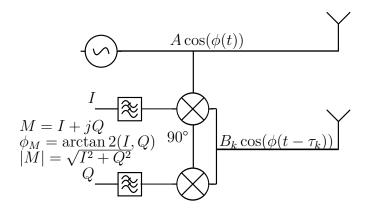

Clearly, the range information is contained in the phase of the returned signal, a hardware friendly way of extracting the phase is with an I/Q mixer as illustrated in figure 2.4.

#### 2.1.2.1 Why I/Q?

We will here take a small digression to explore the need for an I/Q receiver. In signal-processing, dealing with signals as complex exponentials are often

Figure 2.4: Principle of a I/Q continuous wave transceiver, the received signal is mixed with the transmitted signal and a 90° phase shifted version of the transmitted signal (in this case  $\sin(\phi(t))$ ). This gives us sufficient information to extract both the phase and amplitude of the mixer product M.

mathematically convenient, especially since they map nicely to the Fourier transform. Too often however, the real I and imaginary Q parts are extracted by the hardware; in the analog front-end, without any consideration of its advantages and downsides.

If we start by attempting to write the mixer product as

$$M(t) = A(t)\cos(\phi_M(t)) \tag{2.4}$$

then the phase is impossible to extract, since

$$\phi_M(t) = \arccos\left(\frac{M(t)}{A(t)}\right)$$

(2.5)

and A(t) is unknown. We therefore see the need for at least two values, to solve for your two unknowns, assuming of course we actually need the instantaneous phase  $\phi_M(t)$  and/or amplitude A(t). We therefore take two measurements, one shifted  $\theta$  degrees from the other

$$M_I(t) = A(t)\cos(\phi_M(t)) \tag{2.6}$$

$$M_Q(t) = A(t)\cos(\phi_M(t) + \theta). \tag{2.7}$$

Allowing us to write

$$\frac{M_Q(t)}{M_I(t)} = \frac{A(t)\cos(\phi_M(t) + \theta)}{A(t)\cos(\phi_M(t))}$$

(2.8)

which is easy to solve if  $\theta = 90^{\circ}$ , yielding

$$\phi_M(t) = \arctan\left(\frac{M_Q(t)}{M_I(t)}\right).$$

(2.9)

We note that two measurements shifted by 90° is sufficient and convenient, but any shift not equal to integer ratios of 180° would work. We can also use more than two measurements, giving us an overdetermined problem, reducing the noise.

An alternative to a phase shift of  $\theta = \pi/2$ , is to observe that for a constant frequency

$$M_Q(t) = A(t)\cos(\omega_0 t + \theta)$$

we obtain the same value by waiting  $t_{\theta} = \theta/\omega_0 = \frac{\pi/2}{2\pi f_0} = 1/4f_0$

$$M_Q(t + t_\theta) = A(t)\cos(\omega_0(t + t_\theta))$$

$$= A(t)\cos(\omega_0 t + \omega_0 t_\theta)$$

as Nyquist already requires us to sample at least every  $1/(2f_0)$  seconds, the new requirement to sample every  $1/(4f_0)$  seconds to obtain complex samples is in many cases not excessive.

It should be re-stated that this assumes the beat signal is a constant frequency, if the mixer output is constant, like in a CW radar with a stationary target, increasing the sample frequency will not help as we do not get any "new" information about the signal. In addition, for a CW radar, extracting the phase allows us to distinguish between a change in reflected amplitude and a change in phase (movement). Hence for a CW radar, an I/Q receiver does make sense, but let us first check if a CW radar can give any useful range information.

#### 2.1.2.2 Range ambiguity of a CW radar

If we return to the transmitted CW signal in (2.2) and the received in (2.3), we can relate the captured low-pass filtered mixer phase  $\phi_M$  to the two-way travel time by a simple scaling

$$\phi_M = \omega_0 t - \omega_0 (t - \tau_k) \tag{2.10}$$

$$\Rightarrow \tau_k = \frac{-\phi_M}{\omega_0} \tag{2.11}$$

or, in meters,

$$R_k = -\phi_M \frac{\lambda}{4\pi} \tag{2.12}$$

which on the surface looks great, since we can now extract the range to the target. Unfortunately, the phase (2.9) is bounded by  $\pm \pi$ , which means the range estimate is ambiguous and we must write

$$R_k = -\phi_M \frac{\lambda}{4\pi} \pm \frac{n\lambda}{4} \quad \text{for } n = 0, 1, 2$$

(2.13)

The reader is reminded that at 1 GHz the ambiguity in air is  $\pm 75$  mm.

A CW radar is on the other hand, a useful and simple radar architecture for detecting the relative velocity of moving targets. We will, with the exception of section 3.3.3, limit the scope of this thesis by assuming targets are stationary for the duration of a radar measurement. Hence for our purposes the CW radar is not very practical.

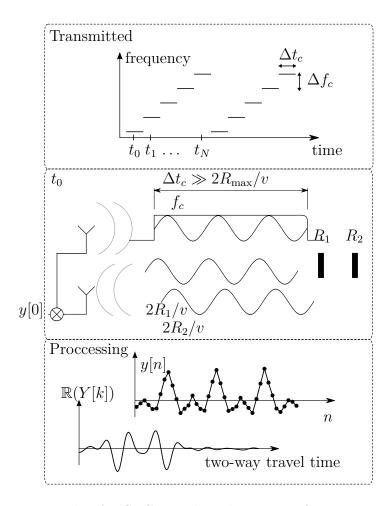

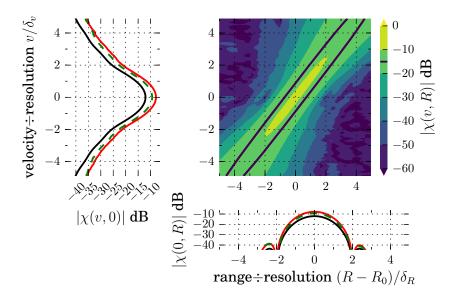

## 2.1.3 Stepped-Frequency Continuous-Wave (SFCW)

To solve this range ambiguity, we introduce the Stepped-Frequency Continuous-Wave (SFCW) radar, sketched in figure 2.5. The idea is that a single frequency is ambiguous, but by probing the environment with a large number of discrete frequencies we can resolve the ambiguity. A different perspective is in the frequency domain, where a SFCW radar recreates the environments transfer function by discretely probing with CW waveforms, hence building up the transfer function one frequency at the time. This is how most network analyzers work, hence a network analyzer makes a great lab-based radar systems.

Figure 2.5: Principle of a SFCW radar, showing N frequency steps spaced  $\Delta f_c$  apart. Note that the pulse time  $\Delta t_c$  is much longer than the two-way travel time so that the receiver compares the phase of the transmitted and received signal for each frequency step. After a low-pass filter (not shown) we are left with a single (possibly complex) samples y[n] for each step which by a Fourier transform and a scaling gives the range response.

A stepped frequency radar that steps through  $n \in [0, ..., N-1]$  frequency steps, from  $f_l$  to  $f_l + (N-1)\Delta f_c$ , will, for each step, obtain after mixing and low-pass filtering

$$y_{\text{SFCW beat}}[n] = AB_k \cos(2\pi (f_l + n\Delta f_c) \tau_k)$$

(2.14)

for a single target at  $\tau_k$ . After all of the y[n] samples are recorded, we can extract the delay  $\tau_k$  by a Fourier transform of (2.14). We note that by superposition, multiple targets can be extracted.

A SFCW radar has a bandwidth of  $N\Delta f_c$  and hence a resolution of

$$R_2 - R_1 = \frac{v}{2BW} = \frac{v}{2N\Delta f_c}$$

(2.15)

where the ambiguity goes from

range ambiguity CW =

$$\pm \frac{\lambda}{4} = \pm \frac{c}{4f_c}$$

(2.16)

range ambiguity SFCW =

$$\pm \frac{c}{\Delta f_c}$$

(2.17)

as outlined in Paper III, which quickly gives a much more useful ranging system.

The receiver for a SFCW radar is often I/Q, but can either be just a single phase as shown here, or as many phases as can practically be implemented.

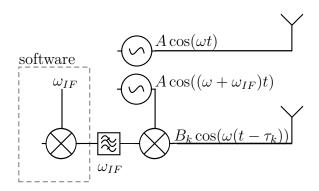

#### 2.1.3.1 SFCW with frequency offset

Especially for a square wave radar, we will see in Paper III, that a heterodyne implementation will be beneficial. We will therefore briefly introduce the principle here.

A CW heterodyne transceiver is shown in figure 2.6, where we note a need for two different frequencies for the mixer inputs (hence hetero-.) and in principle two frequency translation stages. We note that depending on the selected  $\omega_o$ , the last frequency stage can be done after digitization in the digital (software) domain.

It may seem that we have added additional unnecessary complexity, but there are several advantages to down convert to an intermediate non-zero  $\omega_{IF}$  as opposed to direct conversion to DC. Heterodyne architectures have

Figure 2.6: CW transceiver with a frequency offset  $\omega_{IF}$  between the transmitted/received and the second mixer input.

several benefits for I/Q mismatch, flicker noise and DC-offset [Raz97], but we will here concentrate on the idealized case

We have noted in the "Why I/Q" section that an I/Q receiver is required if the frequency is the same on both of the mixer inputs, while as we have argued, we can avoid an I/Q conversion in the analog domain when we have a frequency offset. To show this in the heterodyning case, we write

$$M = AB_k \cos((\omega + \omega_{IF})t) \cos(\omega(t - \tau_k))$$

(2.18)

$$= \frac{AB_k}{2} \left[ \cos(\omega_{IF}t + \omega \tau_k) + \cos(2\omega t + \omega_{IF}t - \omega \tau_k) \right]$$

(2.19)

which after a low-pass or bandpass filter is the wanted phase shift  $\omega \tau_k$  around  $\omega_{IF}$

$$M_{\rm IF} = \frac{AB_k}{2}\cos(\omega_{IF}t + \omega\tau_k) \tag{2.20}$$

where it is trivial to extract  $B_k$  and  $\tau_k$  as long as we have two or more measurements separated in time/phase and we know  $\omega_{IF}$ .

For our square wave radar, this form of (2.20) is beneficial since the harmonics at  $3\omega_{IF}$ ,  $5\omega_{IF}$ , ..., can easily be filtered, which is not the case if we have a zero  $\omega_{IF}$ . An alternative method to obtain two different frequencies at the mixer inputs is a frequency swept transmitter, where a non-zero delay  $\tau_k$  gives us a non-zero beat-frequency proportional to the delay, which is the focus of the next section.

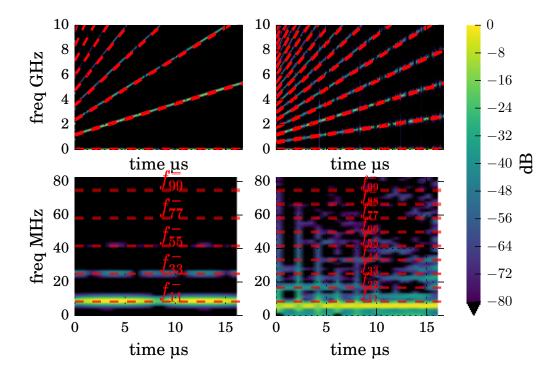

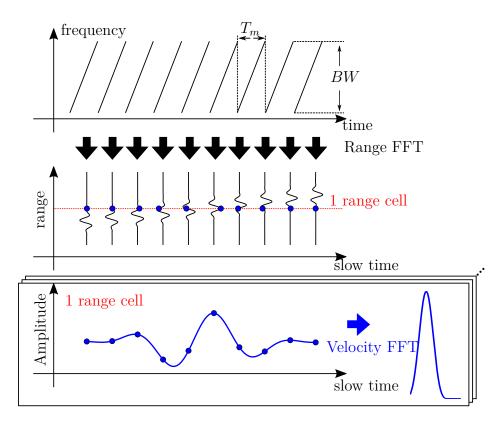

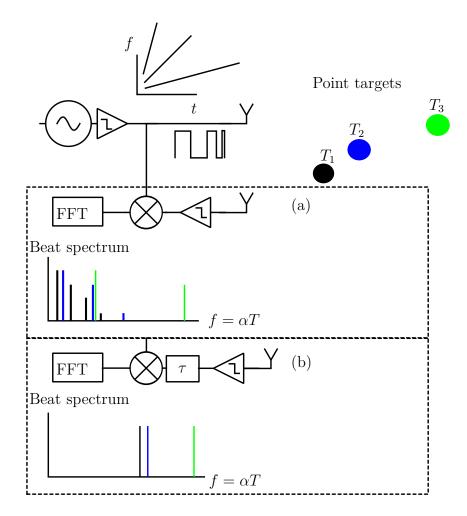

## 2.1.4 Frequency-Modulated Continuous-Wave (FMCW)

Instead of discretely stepping through N frequencies, we can do a linear frequency sweep, obtaining a FMCW radar, where the signal is often called a Linear Frequency-Modulated (LFM) pulse or simply a "chirp". The resolution is then the same as in (2.1) and (2.15), being inversely proportional to the bandwidth of the chirp, while, since we are not discretely stepping, the range ambiguity is removed entirely<sup>1</sup>. The majority of this work is focused on implementing a FMCW radar, but the system is flexible enough to easily adapt to the other radar architectures that we mention in this section.

We now transmit

$$y_{\text{chirp}} = A\cos(\phi_{\text{chirp}}(t))$$

$0 \le t \le T_m$  (2.21)

$$\phi_{\text{chirp}}(t) = 2\pi \left( f_l t + \frac{f_o - f_l}{2T_m} t^2 \right)$$

(2.22)

$$\equiv 2\pi \left( f_l t + \frac{\alpha}{2} t^2 \right) \tag{2.23}$$

where the chirp goes from  $f_l$  to  $f_o$  in  $T_m$  seconds and  $\alpha$  is the chirp rate.

Similar to a heterodyne system, the resulting low-pass filtered mixer product is no longer a constant, but a varying signal with a frequency directly relate to the two-way travel time, often called the beat frequency  $f_{\text{beat FMCW}}$

$$\phi_{\text{beat FMCW}} = 2\pi t \left(\alpha \tau_k\right) + 2\pi \left(f_l \tau_k - \alpha \tau_k^2\right)$$

(2.24)

$$f_{\text{beat FMCW}} = \alpha \tau_k$$

(2.25)

The concept and the chirp parameters are illustrated in figure 2.7. Comparing figure 2.7 and figure 2.5, we note that the processing and output is identical, in that we take our received (mixed and low-pass filtered) samples and do a Discrete Fourier Transform yielding a pulse for each scatterer. The major conceptual difference is that the SFCW radar outputs a single sample (or two for a complex I/Q receiver) for each frequency step, while a FMCW radar gives you the entire frequency response in one sweep. This naturally requires a higher sample rate to digitizer than a SFCW radar, but still far below the transmitted bandwidth BW.

FMCW radar systems are sometimes called a direct-conversion (or homodyne) architectures, but in the view presented in the previous section, the

<sup>&</sup>lt;sup>1</sup>assuming the chirp length is much longer than the maximum-two-way travel time

Figure 2.7: Principle of a FMCW radar, showing a linear frequency sweep from  $f_l$  to  $f_o$  in  $T_m$  seconds.

system is heterodyne. The frequency of the two mixer inputs will be different for all non-zero range-delays. In addition, the architecture is in essence doing two frequency translation steps, if we consider the FFT as a set of mixers and filters.

The heterodyne classification is particularly valid when we insert a delay in the transmit path. As we saw in the introduction, a positive  $\tau_{\rm tx} - \tau_m$  ensures the beat spectrum is moved up in frequency. Making the separation of harmonics and signals trivial and ensuring a non-zero difference in the frequency of the mixer inputs.

An architecture that requires the processing of the entire BW is presented next, where we are no longer limited to simple frequency modulated waveforms, but can employ any arbitrary signal.

#### 2.1.5 Correlator based radar

By capturing the entire received signal and doing a correlation with the entire transmitted signal, we have what we will refer to as a correlator based radar. In discrete time

$$c_{xy}[k] = \sum_{n=0}^{N} x[n]y[k+n]$$

for  $-N/2 < k < N/2$ . (2.26)

We notice that for k=0 this is a single mixer and a low-pass filter. A correlation radar can be implemented with a single mixer if we step the delay, effectively giving us a sequential sampling architecture [SSFS08], where each range cell is scanned one at a time.

The correlation inputs, x and y, can be in the baseband, where the signal "on-air" is a phase coded signal on some carrier frequency, as was illustrated in figure 2.3 (page 18), frequency coded or even amplitude coded.

A correlator will work as a matched filter for any waveform and is therefore highly flexible. The disadvantage of a full correlation compared to a mixer based radar is that for a digital correlation we must digitize the entire signal bandwidth which is why the sequential sampling architecture is often used [Sac13]. As an alternative, we propose to take advantage of the ease of computing the correlation when we only have a single bit, this means we can cover the entire range view at a time and can use multiple sweeps to reduce the noise and non-linearity as further discussed in Paper III.

Only correlating with a single bit is an old technique that has been well studied, Watts [Wat62] discusses analog correlation, digital and single bit (called polarity-coincidence), Ekre [Ekr63] the effects of sampling in time. Remley [Rem66] gives a further list of references in the introduction and studies both Gaussian and sinusoidal noise. Weinreb [Wei63] wrote his PhD on a single bit auto-correlation to obtain a power-spectrum which we will return to in section 5.5. The earliest work we have found is by Vleck in 1943, republished in [VM66], which similar to Weinreb looks at the autocorrelation. More recent work include the patent by Reves [Ree10] for a noise radar, which (for some odd reason) proposes to do the correlation after averaging, neglecting the computational advantage of a single bit correlation, but which covers the advantage of adding noise. Axelsson [Axe01] shows how adding noise (or working in a noisy environment), improves the linearity of the single bit correlation and also notes that the concept works for "chirps, step frequency and phase code modulation" [Axe01].

The above literature studies different applications and hence have different input probability density assumptions, but all conclude with either simulation or theory that correlating with single bit does work, though with mixed tradeoffs. A common result found in [Wei63] for Gaussian statistics is a reduction in SNR of  $10 \log_{10}(\pi/2) \approx 1.96 \,\mathrm{dB}$  for a single bit correlator in a noisy environment. Ekre deals with a few different input statistics and sample rates and finds a reduction in SNR between 1 dB and 10 dB while [Hjo16] shows both the 1.96 dB result for Gaussian statistics and a novel result of near zero SNR loss for filtered noise. We will return to this metric in section 3.2 where we show that a single bit FMCW radar has the same property of only a minor degradation in SNR in a noisy environment.

What sets the correlation system proposed in Paper II and Paper III apart is the use of a sweep threshold which will linearize the system even in high SNR scenarios.

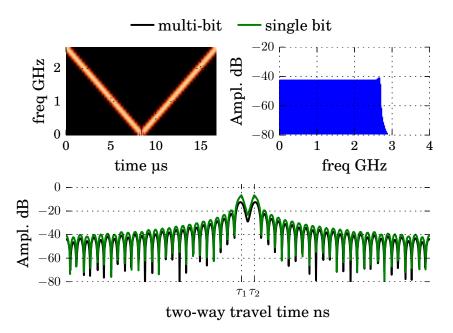

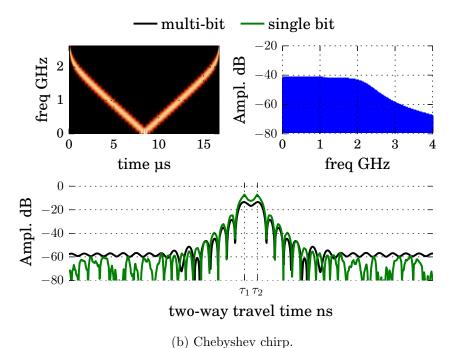

#### 2.1.5.1 Any waveform

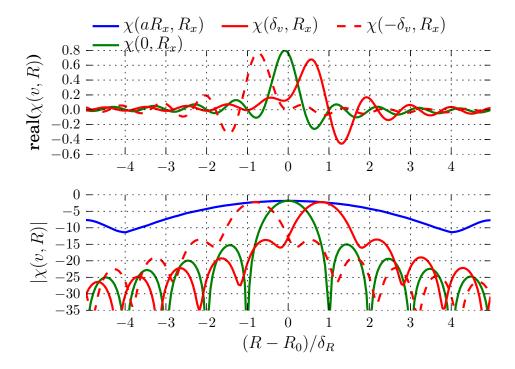

To demonstrate that any waveform can be used, figure 2.8 shows a simulated scenario with a standard linear chirp (a) as defined in (2.22) and a modified

(a) Conventional linear chirp.

Figure 2.8: The two top panels shows the transmitted signal as a spectogram and as a Fourier transform (no-window). The bottom shows the resulting correlation with two targets at  $\tau_1$  and  $\tau_2$  using both a multi-bit correlation (limited by computer simulation) and over sampled single bit.

chirp (b)

$$\phi_{\text{cheby chirp}}(t) = \frac{\pi \alpha_L}{T_m} \left( t - \frac{T_m}{2} \right)^2 - \frac{\pi \alpha_C T_m}{2} s \tag{2.27}$$

where

$$s = \sqrt{1 - \frac{4}{T_m^2} \left(t - \frac{T_m}{2}\right)^2}$$

(2.28)

from [Ric14], where we have used  $\alpha_L = 1.5 f_o$  and  $\alpha_C = 0.075 f_o$  in the example. We see from figure 2.8, that by modifying the transmitted signal we change the obtained range profile side-lobe structure. We note that we are effectively applying a window function but in place of adjusting the amplitude we simply modify the frequency to sweep faster through the higher frequencies. For a single target, this is equivalent to studying the autocorrelation of the transmitted signal.

The goal is then to find a signal with a "good" autocorrelation. As it turns out, a random signal can be a good choice, often referred to as a noise-radar.

#### 2.1.5.2 Noise radar, random signal

The goal achieved by a noise radar is to suppress the side lobes, we would ideally like to have a autocorrelation (or correlator output with a return at zero delay) as a Dirac

$$c_{xx}[k] = \begin{cases} 1 & \text{for } k = 0\\ 0 & \text{elsewhere} \end{cases}$$

(2.29)

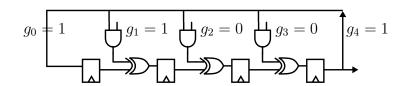

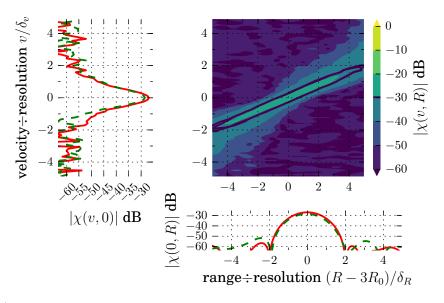

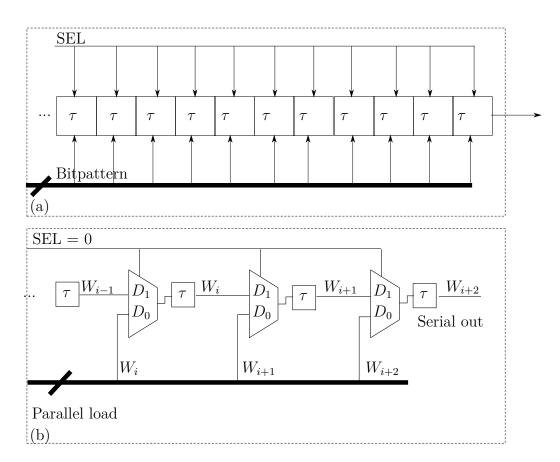

A perfect autocorrelation cannot be achieved with a binary sequence longer than length 4 [BA91], but a random sequence will approach this goal for longer sequences. We will, similar to Sachs [Sac13], limit our study to Maximum length sequence (m-sequence), which is a pseudo-noise sequence. It is pseudo, because it repeats itself after  $2^m - 1$  bits and is hence deterministic. It can also be categorized as a shift-register sequence as it can be computed with a shift-register with feedback. Figure 2.9 shows a Galois shift-register configuration of length m = 4, where the  $g_i$  ( $i \in [0, 1, 2, 3, 4]$ ) is the tap weights with values  $g_i \in [0, 1]$ . Taps that yield a maximum length sequences are available, [Ins05] gives values up to length m = 32.

With infinite bandwidth, a m-sequence of length  $N=2^m-1$  has the

Figure 2.9: Galois shift-register configuration of length 4 with taps g = [1, 1, 0, 0, 1] to yield a m-sequence. Not depicted but the registers must avoid being reset to the all-zero state, all other starting sequences will yield a m-sequence.

autocorrelation

$$c_{xx_m}[k] = \begin{cases} 1 & \text{for } k = 0\\ -1/N & \text{elsewhere} \end{cases}$$

(2.30)

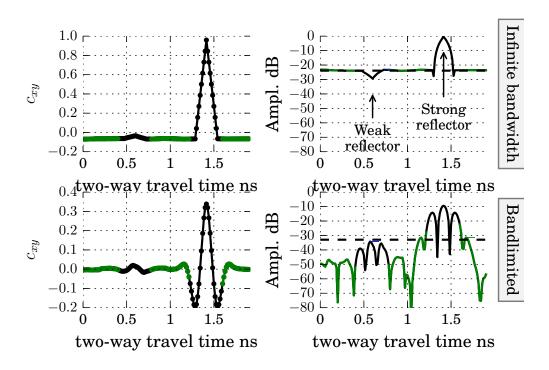

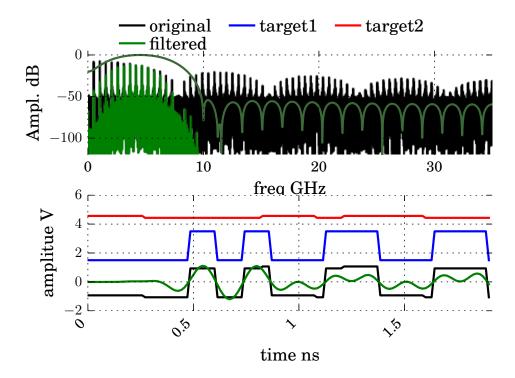

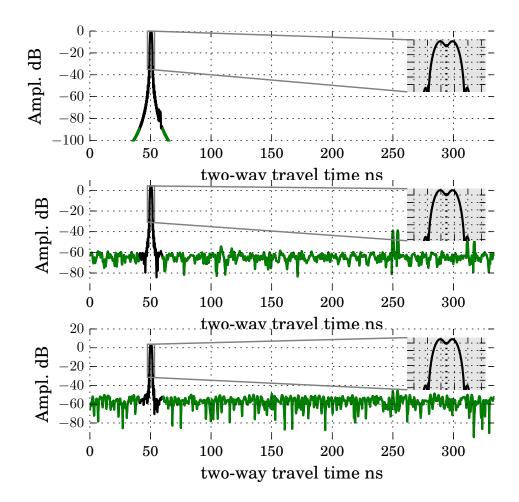

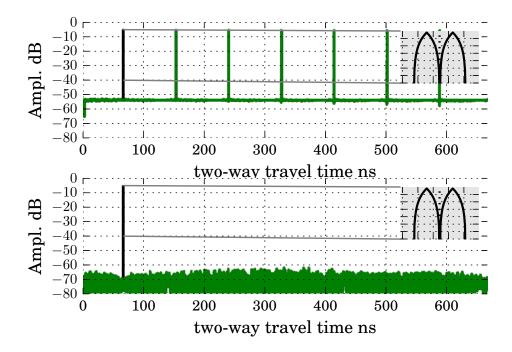

An interesting note in [Sac13, page 84], is that the -1/N is not a "side-lobe" level, in that it does not hinder the detection of weaker scatterers. In particular, Sachs shows that the -1/N term vanishes for a non-DC coupled channel. To show this, a similar simulation to Paper III is setup, with an order 4 m-sequence and a swept threshold receiver (128 sweeps) with single bit correlation.

One would assume that a scatterer with an amplitude of 1/N would be below the sidelobe level and hence undetectable, but as seen in figure 2.10, this scatterer is still visible. In addition, by band-limiting the channel (see figure 2.11, we approach the ideal characteristic of (2.29), the downside is that we now have *true* sidelobes that depend on the channel filter/transfer function and quantization. Note that we here use a band-pass filter, the high-pass response ensures we get rid of the -1/N level, while the low-pass portion of the filtering gives ripples in the correlation output; moving us away from the idealized triangular shape.

In particular for communication, one not only cares about the autocorrelation (2.29), but also the cross-correlation between different users. Example of codes having both good autocorrelation and cross-correlation properties are Gold codes. These codes should also be considered for radar applications with multiple users, such as automotive radars.

As a side-note. In automotive radar, FMCW seems to be the dominating architecture and interference from identical chirps are problematic; Brooker [Bro07] shows this and also discusses some mitigating techniques.

Figure 2.10: M sequence order 4 (N=15) simulation with 2 targets (one with amplitude  $1/15=-23.5\,\mathrm{dBc}$  marked with strippled line.) in linear (left) and log (right) y-scaling. Expected return colored black. Top is an ideal channel while the bottom is band-pass limited (see figure 2.11).

Figure 2.11: Original and filtered (band-limited) channel for a order 4 M-sequence repeated 100 times. Bottom shows the first sequence with the two targets separated in y-scale for clarity.

Pseudo or true random sequences are implementation wise more challenging, but should be carefully considered for automotive radar. It should be stated that for some of the cases discussed by Brooker, a single bit radar will have an advantage over a conventional architecture since it will naturally clip large short time interference signals without any post or pre-processing.

# 2.2 Swept threshold

A central aspect of the proposed radar system is the sweep threshold quantizer which amplifies the signal and compares it to a (possibly fixed) threshold. We will here discuss some peculiarities of such a quantizer, both for the single quantizer used on the transmitter and the sweep-threshold quantizer on the receiver. We will see that for the transmitter, a single frequency modulated signal can be clipped in amplitude without loss of information, while the receiver requires multiple thresholds to remain linear. We will discuss noise and focus on the benefits it brings to the receiver.

Figure 2.12: Single bit decomposition. Assuming a stationary scene this can be serialize by repeating the sweep while thresholding at different levels

With the arrangement in figure 2.12, there are several points of view depending on the input voltage

• A single sinusoidal can be hard clipped with a single quantizer with the threshold set to the mean level. This creates harmonics, but the original sinusoidal phase and frequency is unambiguously maintained.

- An arbitrary signal can be de-composed with a set of linearly distributed comparator levels, in a Flash-ADC manner. Linear processing can be applied both before or after the summing operation [Tsi06].

- In noise levels comparable to the signal, the threshold levels can even be fixed at the mean level, giving us a SSR system [Sto00].

In addition, we not only have amplitude quantization, but it is natural to include sampling in time. The above points are the focus of this section.

## 2.2.1 A single quantizer

We start by investigating a single quantizer without noise and the threshold set to the DC level of the signal. In the Fourier domain, we can write

$$sign [A cos(\omega t)] = \sum_{n=1,3,5,\dots}^{\infty} a_n cos(n \cdot \omega t)$$

(2.31)

$$= \frac{4}{\pi} \left( \cos(\omega t) + \sum_{n=3,5,\dots}^{\infty} \frac{1}{n} \cos(n \cdot \omega t) \right)$$

(2.32)

Equation (2.32) shows that the sign (zero crossings) of  $\cos(\omega t)$ , will yield  $\cos(\omega t)$  with additional odd harmonics  $\cos(n\omega t)$ . We can therefore reconstruct our original frequency  $\cos(\omega t)$ , by low-pass filtering. We therefore see, that the sign function is sufficient when we are only dealing with a single frequency.

Note also that the original amplitude A in (2.31) is lost, as the resulting square wave will always be  $\pm 1$  peak-to-peak. Hence, we lose the ability to do amplitude modulation with this simple scheme; for our radar transmitter, this is actually an advantage, as we also gain robustness against amplitude errors, as long as we can keep the digital signal at high and low.

#### 2.2.1.1 Looking at the zero crossings

An alternative explanation, that does not need a Fourier transform, is that we can extract the original frequency  $\cos(\omega t)$  by looking at the zero crossings. Clearly the sign function does not change the number of zero crossings and by using the "The Dominant Frequency Principle" [Ked86] we can uniquely

extract the frequency, by counting the number of zero crossings. This property is further explored in figure 2.13 where we give two examples of detecting a frequency even in Gaussian noise and sinusoidal interference.

The zero crossing principle can be extended to a linearly increasing/decreasing frequency

$$y_{\text{FMCW}} = \cos\left(2\pi\left(f_l t + \frac{\alpha}{2}t^2\right)\right)$$

which, following [Wil81] is zero at

$$n\pi = 2\pi \left( f_l t_n + \frac{\alpha}{2} t_n^2 \right) \quad \text{for } n = 0, \pm 1, \pm 2, \dots$$

$$\Rightarrow t_n = \frac{f_l}{\alpha} \left( -1 \pm \sqrt{1 + \frac{\alpha n}{f_l^2}} \right).$$

Giving us the instantaneous frequency as

$$f_{n+1} = \frac{1}{2|t_{n+1} - t_n|}$$

As the waveform is linearly modulated, we can linearly interpolate between the  $\{f_n\}$  values to reconstruct  $y_{\text{FMCW}}$ . Meaning we can safely clip a linearly modulated waveform to only 2 levels, as long as this process keeps the zero crossings.

#### 2.2.1.2 Multiple frequencies

Unfortunately, since the sign function is not linear, we cannot expect equality with multiple frequencies

$$sign \left[ A\cos(\omega_1 t) + B\cos(\omega_2 t) \right] = \sum_{n=1,3,5,\dots}^{\infty} a_n \cos(n\omega_1 t) + \sum_{n=1,3,5,\dots}^{\infty} b_n \cos(n\omega_2 t)$$

(2.33)

we instead obtain

$$= \sum_{n=1,3,5,\dots}^{\infty} \alpha_n \left[ A \cos(\omega_1 t) + B \cos(\omega_2 t) \right]^n$$

(2.34)

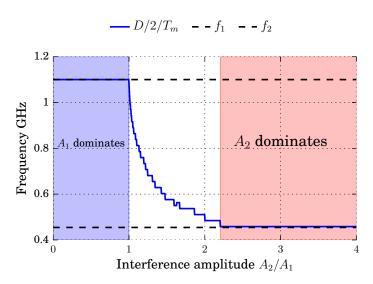

(a) Extracting the dominant frequency by counting the number of zero crossings D for  $A_1 \cos(2\pi f_1 t) + A_2 \cos(2\pi f_2 t)$ , as long as  $A_2$  is less than  $A_1$  (and  $f_1 > f_2$ ), the zero count gives the frequency of  $A_1$ .

(b) Extracting the dominant frequency by counting the number of zero crossings D for  $A_1 \cos(2\pi f_1 t) + N(0, \sigma)$ , where  $N(0, \sigma)$  is bandlimited gaussian noise with zero mean. With sufficient SNR (low  $\sigma$ ), the zero count gives the frequency of  $A_1$ .

Figure 2.13: Two examples showing the robustness of the "The Dominant Frequency Principle" [Ked86], by using the number of zero crossings to find the dominant frequency in (a) sinusoidal interference and (b) Gaussian noise.

To gain some insight, we can expand the even 2nd harmonic, which will be present for a "non-ideal" clipping

$$[A\cos(\omega_{1}t) + B\cos(\omega_{2}t)]^{2}$$

$$= A^{2}\cos(\omega_{1}t)\cos(\omega_{1}t)$$

$$+ 2AB\cos(\omega_{1}t)\cos(\omega_{2}t)$$

$$+ B^{2}\cos(\omega_{2}t)\cos(\omega_{2}t)$$

$$= A^{2}/2 + B^{2}/2$$

$$+ A^{2}/2\cos(2\omega_{1}t) + B^{2}/2\cos(2\omega_{2}t)$$

$$+ AB\cos(\omega_{1}t - \omega_{2}t) + AB\cos(\omega_{1}t + \omega_{2}t)$$

(2.35)

(2.36)

we now have some DC terms, a frequency doubling of each input and intermixing products  $\omega_1 \pm \omega_2$ . We note that the original signal  $\cos(\omega_1 t) + \cos(\omega_2 t)$  is lost in the above expansion, but this *will* be present for odd order non-linearity.

We see that non-linearity can quickly become unmanageable when we have an arbitrary input signal. Not only do we get harmonic products, we also get various intermixing products that will depend on the input signal. These are non-trivial to filter out and as such we need a different strategy.

## 2.2.2 Multiple quantizers

We have seen that a single quantizer without noise is unable to deal with two (or more) sine wave signals without introducing significant intermixing products. There are 2 ways of linearizing the quantization process, both based on the principle in figure 2.12. We will start with the intuitive flash-ADC principle in section 2.2.2.1, before venturing into the stochastic resonance world in section 2.2.2.3.

#### 2.2.2.1 Single bit quantization in a noise free environment

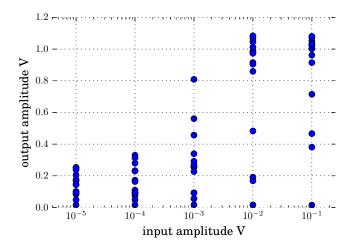

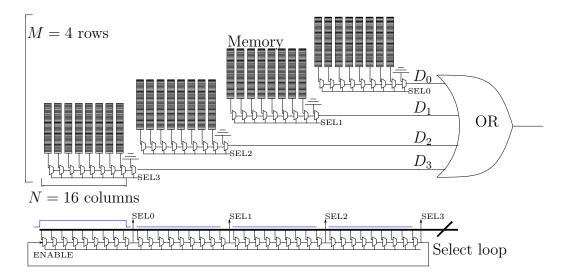

As seen in figure 2.14, the swept threshold quantizer can be used as a flash-ADC, where we need to use  $2^{N_{\text{bits}}}$  unique threshold levels to get an  $N_{\text{bits}}$  representation of the input signal.

Modeling the deviation between the quantized and the "true" signal as an error which is white and assuming our threshold levels span a sinusoidal

Figure 2.14: Single bit decomposition as a flash-ADC, illustrated with a 2 bit (4 comparators) quantizer. The threshold levels are selected to linearly span the input signals range. Assuming a stationary scene this can be serialize by repeating the sweep while sweeping the threshold and averaging coherently.

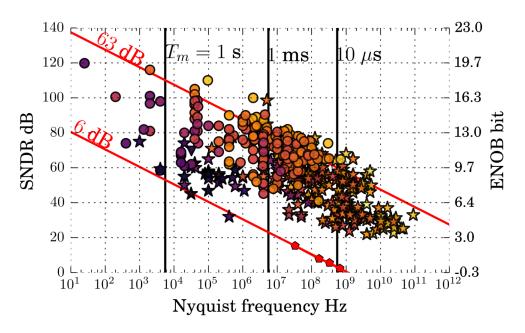

signal linearly and sampling at the Nyquist rate of  $2f_{\text{signal}}$  we obtain the classical maximum signal to quantization ratio [JM08]

$$SQNR_{db} = 6.02N_{bits} + 1.76$$

(2.38)

That is, for every bit we add, the theoretical SNR limit is improved by  $6.02 \,\mathrm{dB}$ . At  $N_{\mathrm{bits}} = 16$  bits, the quantization noise level will be at  $98 \,\mathrm{dB}$  and our flash-ADC would need  $2^{16} = 65\,536$  comparators.

Implementing  $2^{16}$  comparators on a single chip is not feasible, especially at RF frequencies, but alternatives exist. The method used in this thesis uses a single quantizer and repeats the sweep  $2^{N_{\rm bits}}$  times, coherently averaging the results. A hybrid solution can also be used, where  $N_{\rm comparators}$  reduces the number of sweeps to  $2^{N_{\rm bits}}/N_{\rm comparators}$ . Lastly, as will be discussed in section 2.2.2.2, oversampling and noise shaping can improve the SNR without adding more bits.

At this point, a swept-threshold quantizer may not sound overly appealing, as the quantization noise floor puts a severe limit on the systems theoretically achievable Signal to Noise Ratio (SNR). In addition, to achieve this limit requires (1) a stationary scene during a long integration window, (2) a precise adjustable threshold and (3) synchronization to achieve a coherent integration (integrating in-phase). We could end the thesis at this

somber point, but let us first consider oversampling and then the signal in non-coherent noise.

#### 2.2.2.2 Oversampling

We will here briefly cover the effects of sampling and pay particular attention to sampling above the Nyquist rate. In essence, Nyquist promises that we can perfectly reconstruct a signal band-limited to  $f_{\text{signal}}$  if we sample at least  $2f_{\text{signal}}$ . A "caveat" mentioned by most signal processing textbooks, is that a band-limited signal implies a signal that extends infinitely in time [Wes16]. Any practical system will process a finite set of samples band limited by a finite filter. An often applied solution to a finite anti-aliasing filter, filter distortion and a reconstruction that reflect the harmonic content of a signal is therefore to sample well above the Nyquist rate [Wes16]. There is however a second advantage to oversampling, namely a possible reduction in quantization noise, which is the focus of this discussion.

A perfect reconstruction assumes a "perfect" quantization, any deviation in the sampling will show up as a deviation in the reconstruction. For a digital quantization, this leads to an unavoidable quantization in amplitude. In particular for the coarse discretization proposed here, with only a single bit, we clearly need an alternative method for obtaining a reasonable resolution. Oversampling is a well known technique to achieve an improvement in resolution, especially combined with single bit quantization as a single bit quantization allows the sample rate to be pushed orders of magnitude higher than the signal frequency.

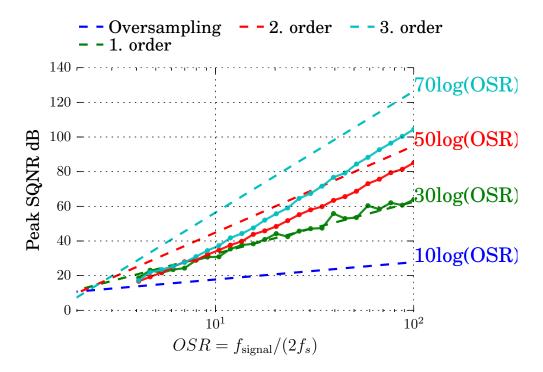

With the same assumptions as for equation (2.38), the quantization noise will have the same total power when oversampling, but spread (evenly) over a larger bandwidth. If we then low-pass filter (usually done digitally), down to the Nyquist rate, we obtain an improved SQNR of [JM08]

$$SQNR_{db} = 6.02N_{bits} + 1.76 + 10\log_{10}\left(\frac{f_s}{2f_{signal}}\right)$$

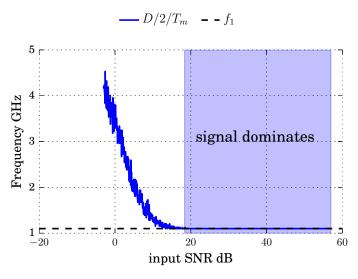

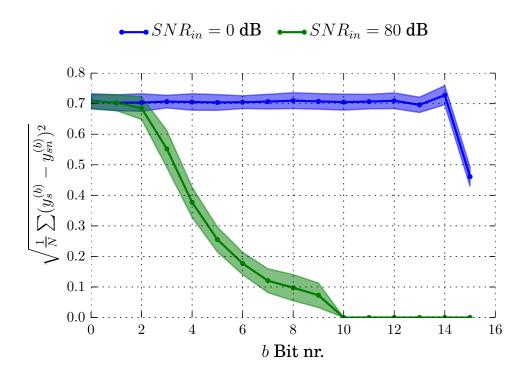

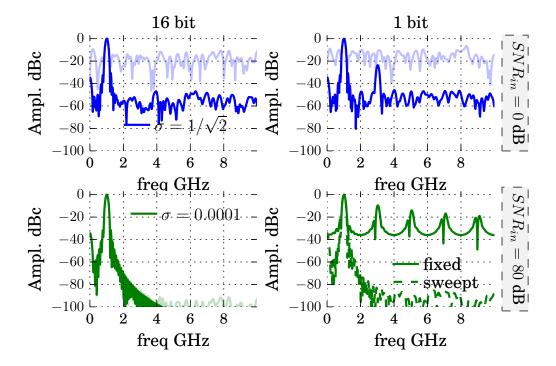

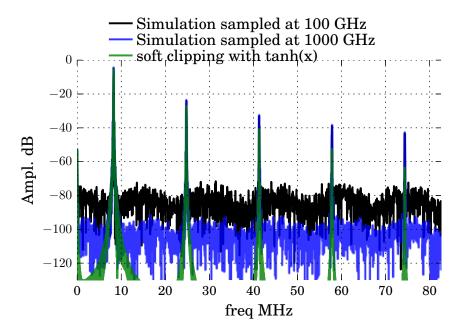

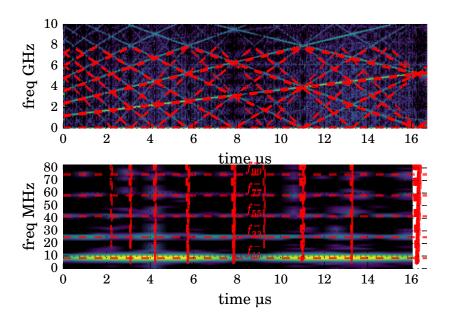

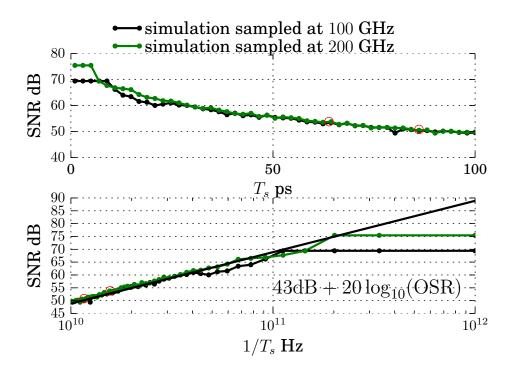

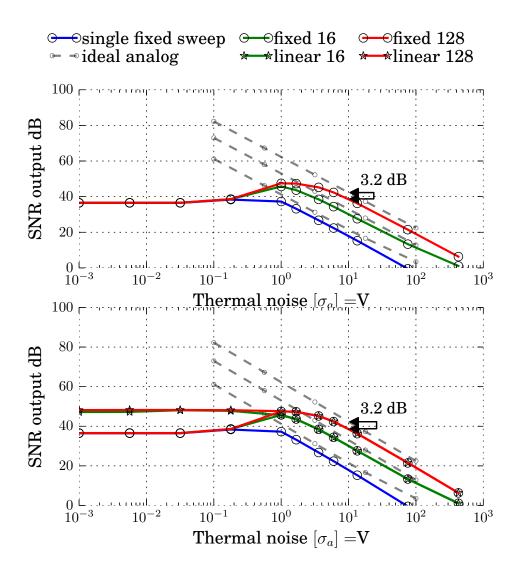

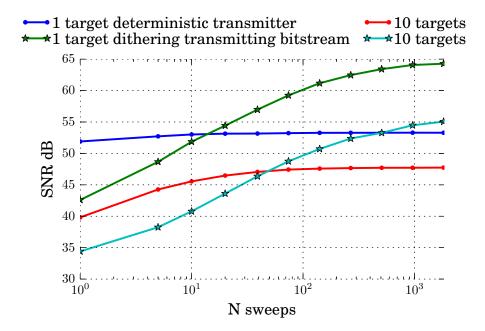

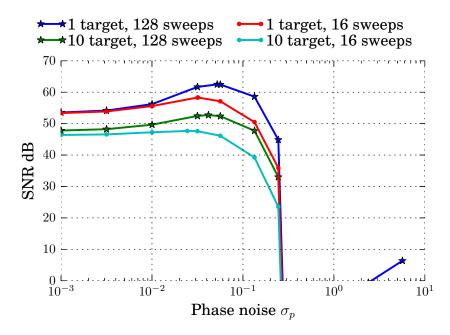

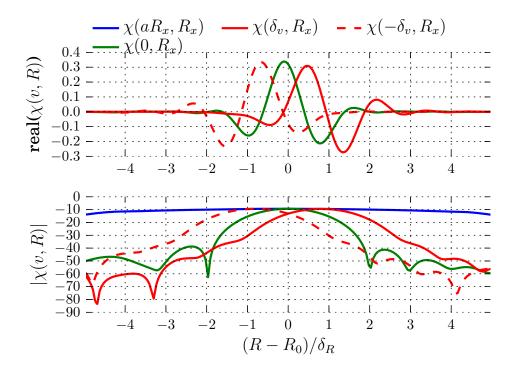

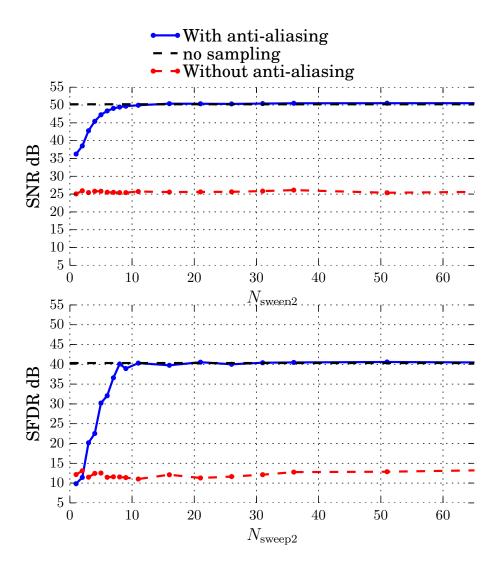

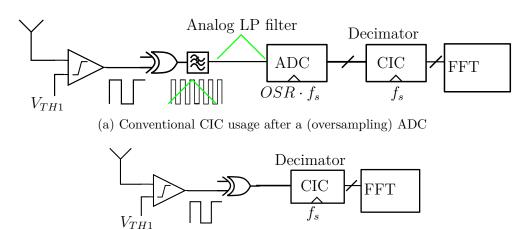

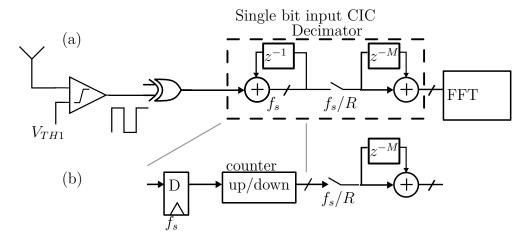

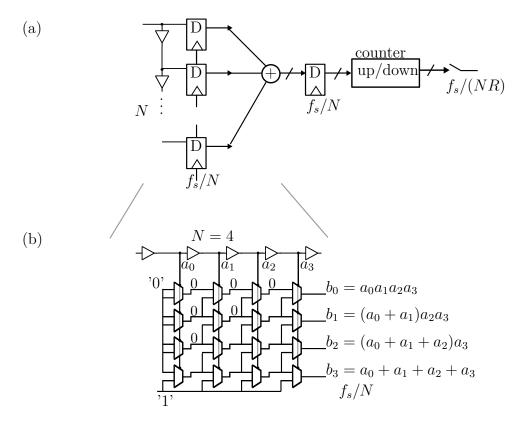

(2.39)