**Master Thesis**

# Development of a wide band front end echo sounder receiver circuit

Jatin Sharma

Master of Science in Physics Programme: Electronics

Department of Physics University of Oslo August 2015

# Preface

With this Thesis, I am finishing my Master's Degree and during these years of my studies, I have learned a lot both theoretically and practically. I am quite satisfied with the knowledge and experience I gained in the field of Electronics, while working here at the Physics Institute, University of Oslo.

First and foremost i would like to thank my two supervisors, Dr. Helge Balk and Dr. Ketil Røed who helped me in selecting my Master Thesis in such an interesting topic of Hydro acoustics and guided me and gave me useful tips during my Masters to achieve my goal. It was very amazing that the courses which I have taken during my Master here at the Physics Institute were put into practical use during my thesis work and this helped me a lot to enhance my knowledge and learn new things.

A special thanks to the members of the E-Lab especially to Stein S. Nielsen and David M. Bang for providing the necessary electronic components, helping me with the hardware development and ordering the PCB board.

Since, my field of study Hydro-acoustics is a very broad subject. The special course 'Hydro-acoustics' offered by Helge Balk was very helpful in understanding the concepts behind propagation of sound in the sea and various phenomenons which take place during its propagation that need to be compensated in the receiver electronics. I tried to develop my echo-sounder considering the earlier efforts that other students had made and making the echo-sounder work as I desire. I learned a lot from the course FYS3220(Linear circuit Electronics) about the analog electronics section in my circuit and it helped me a lot to understand the various aspects of my design. Course FYS4220(Real time and embedded data systems) was helpful in understanding the digital part of my project.

I would also like to thank the faculty of Physics department for providing me the necessary lab equipments and my fellow students who were sitting besides me in the room 323, for helping me from time to time, when i needed them.

I am very grateful to my parents and the family members, my Uncle and Aunt living here who supported me with every thing during these years. Without their help, it would not have been possible. It was also a challenge for me to come to Norway and start again as a student.

Jatin Sharma

July, 2015

# Abstract

The work which is documented in this thesis deals with the development of front end Echo sounder receiver circuit. The goal was to develop a system which can be used for wide band applications. The scope of this project could have been made limited to the development of front end receiver circuit only, but it would also be interesting to see other methods for transmission of pulses. Receiver electronics together with the transmitter have been designed on a single board to check the performance of the complete system.

The project begins with the introductory part describing about the background of Hydro acoustics and then description of various methods used in echo sounding and how they are implemented. Then, it illustrates the various options and tools available to achieve the desired goal. Design and development part provides information about how these specific methods are actually realized in practice. And at last, the developed system is tested to check the results and the concluding remarks are written.

While designing the Electronics, I tried to make the system quite flexible such that it can be operated on various frequencies.

A short description about the Sonar equations is given. An illustration showing how these equations relate to the loss of signal strength when a pulse propagates through sea water is provided and the corresponding challenges encountered by the receiver electronics in lifting this low amplitude signal.

New receiver circuit has been constructed which will help in classifying the various targets in the sea by processing the received echoes. Instead of using a front end resonance filter, a switch has been implemented. To handle the large dynamic range in the received echo, Variable Gain Amplifier has been used. It is used for providing the TVG with the help of DAC. Echo signals are converted into digital values using ADC. FPGA system has been used to provide the digital support which is further connected to the PC.

Apart from this, a different technique for generation of electrical pulses like use of MOSFET technology, is implemented in the transmitter electronics. The methods for amplifying the pulses are also reconsidered and SMPS technique is used. I introduced the possibility of easily varying the transmitted power from the transducer by doing simple modifications.

The designed system has worked quite well meeting the expectations. All the results which are shown in this project are obtained in the laboratory and further work is to measure the results in the sea.

# Contents

| 1 | Introduction |        |                                                             |    |  |

|---|--------------|--------|-------------------------------------------------------------|----|--|

|   | 1.1          | Backg  | round                                                       | 8  |  |

|   |              | 1.1.1  | Hydro Acoustics                                             | 8  |  |

|   | 1.2          | Echo S | Sounder                                                     | 10 |  |

|   |              | 1.2.1  | Earlier Developed Echo sounders                             | 13 |  |

|   | 1.3          | Digita | l Signal Processing                                         | 15 |  |

|   |              | 1.3.1  | Programmable Logic-Background                               | 15 |  |

|   |              | 1.3.2  | What are FPGAs?                                             | 16 |  |

|   |              | 1.3.3  | Hardware Description Language                               | 17 |  |

|   | 1.4          | Challe | enge and Motivation                                         | 18 |  |

| 2 | Ma           | terial | and Methods                                                 | 20 |  |

|   | 2.1          | Softwa | ares used in Project                                        | 21 |  |

|   |              | 2.1.1  | OrCAD                                                       | 21 |  |

|   |              | 2.1.2  | CADSTAR                                                     | 21 |  |

|   |              | 2.1.3  | QUARTUS II                                                  | 22 |  |

|   |              | 2.1.4  | Ūltra Librarian                                             | 22 |  |

|   | 2.2          | System | n Description                                               | 23 |  |

|   |              | 2.2.1  | Pulse Generation                                            | 25 |  |

|   |              | 2.2.2  | Alternate option for voltage amplification                  | 27 |  |

|   |              | 2.2.3  | Transducer                                                  | 28 |  |

|   |              | 2.2.4  | Receiver Protection Circuit                                 | 31 |  |

|   |              | 2.2.5  | Compensation for Transmission Loss and Amplification        | 33 |  |

|   |              | 2.2.6  | Digitalization of received echoes                           | 36 |  |

|   |              | 2.2.7  | Envelope Detection                                          | 39 |  |

| 3 | Des          | sign a | nd Development                                              | 40 |  |

|   | 3.1          | Choice | e of components                                             | 42 |  |

|   |              | 3.1.1  | Transmitter                                                 | 42 |  |

|   |              | 3.1.2  | HV Protection Transmitter( $T_x$ )/Receiver( $R_x$ ) Switch | 45 |  |

|   |              | 3.1.3  | Receiver                                                    | 46 |  |

|   |              | 3.1.4  | Choice of FPGA                                              | 52 |  |

|   | 3.2          | Hardw  | vare Development                                            | 54 |  |

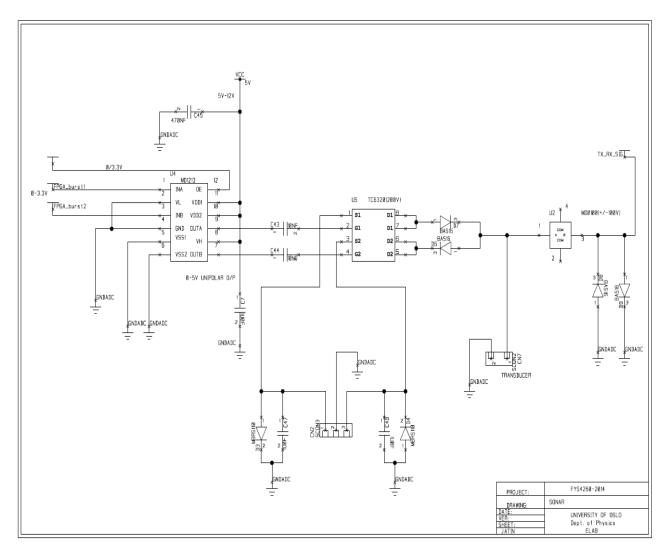

|   |              | 3.2.1  | Schematics of Transmitter Part                              | 54 |  |

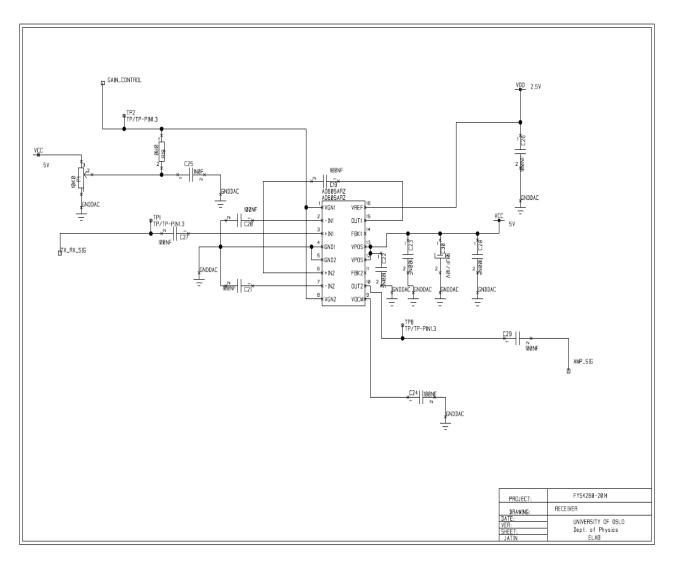

|   |              | 3.2.2  | Schematics of Receiver part                                 | 57 |  |

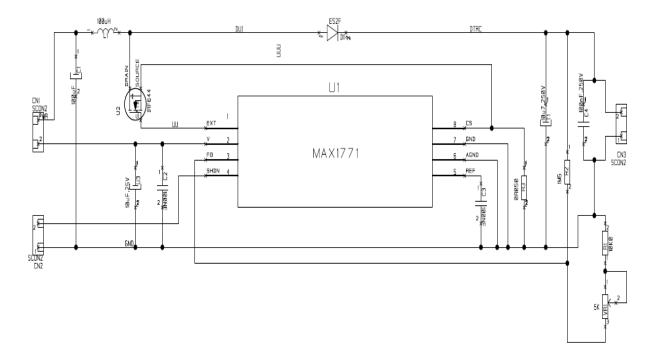

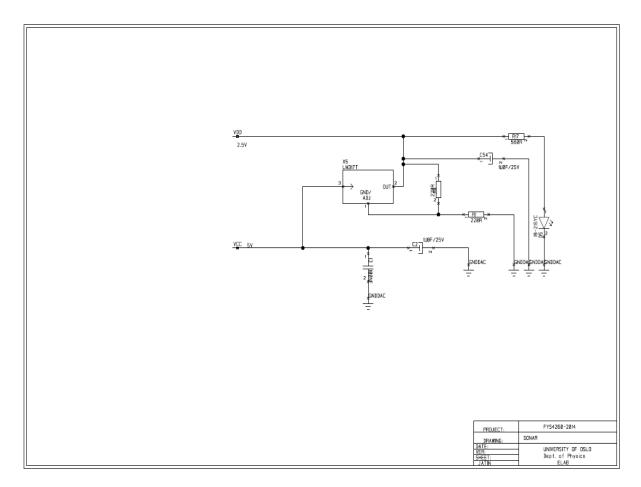

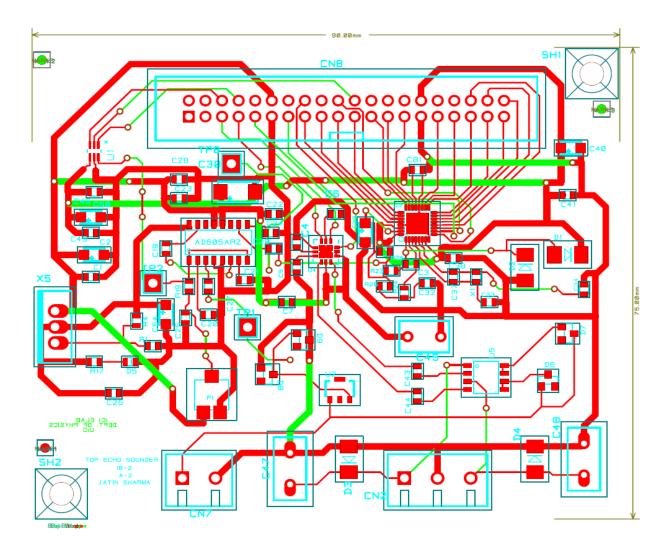

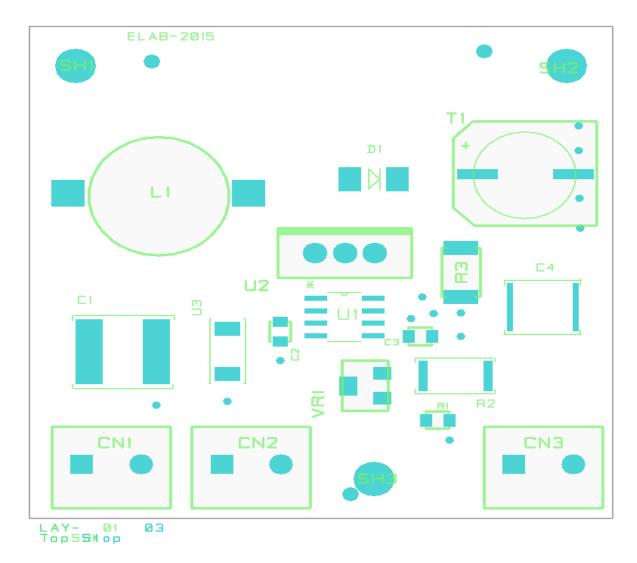

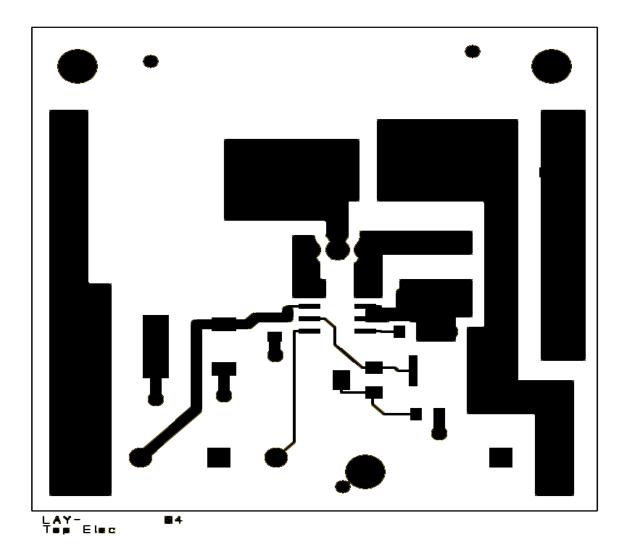

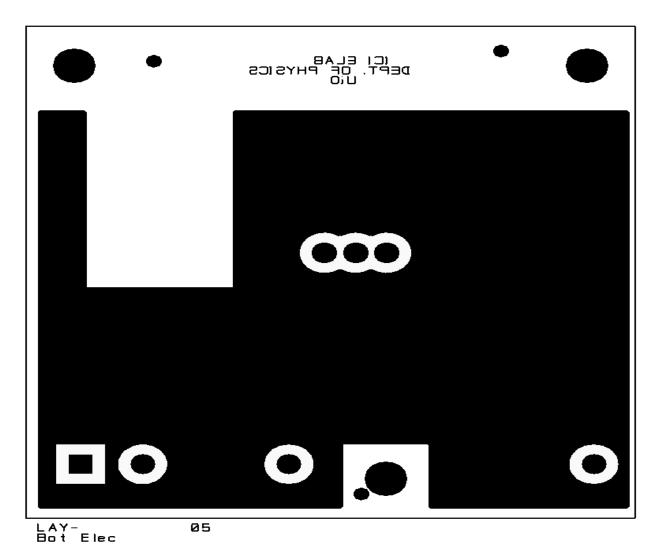

|   |              | 3.2.3  | High Voltage MAX1771 Board                                  | 62 |  |

|   |              | 3.2.4  | Designed High Voltage MAX1771 Board                         | 63 |  |

|   |              | 3.2.5  | Designed Echo sounder Board                                 | 64 |  |

|    | 3.3     | Software Development                                          | 66       |

|----|---------|---------------------------------------------------------------|----------|

|    |         | 3.3.1SimulationSimulation3.3.2VHDL Code DevelopmentSimulation | 66<br>68 |

| 4  | Tes     | ting and Observation                                          | 78       |

|    | 4.1     | Testing of Transmitter Unit                                   | 79       |

|    |         | 4.1.1 Testing of MD1213                                       | 79       |

|    |         | 4.1.2 Testing of MD1213 + TC6320                              | 81       |

|    | 4.2     | Test using a Transmitter and a hydrophone                     | 83       |

|    | 4.3     | Testing of Ultrasound Switch                                  | 85       |

|    |         | 4.3.1 Transmitted Voltage seen from Receiver Side             | 86       |

|    | 4.4     | TVG using DAC                                                 | 87       |

|    | 4.5     | Testing of Amplifier using Variable Gain                      | 87       |

|    |         | 4.5.1 Setup for testing of Amplifier                          | 88       |

|    |         | 4.5.2 Observation                                             | 89       |

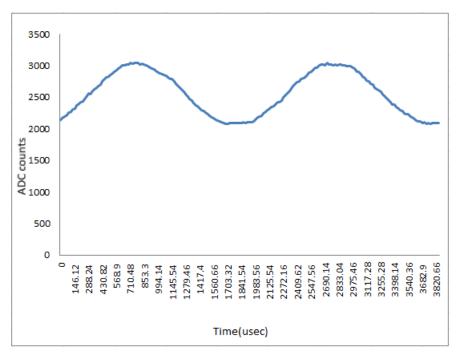

|    | 4.6     | Envelope Detection using ADC and DAC                          | 90       |

|    |         | 4.6.1 Setup                                                   | 90       |

|    | 4 7     | 4.6.2 Observation                                             | 91       |

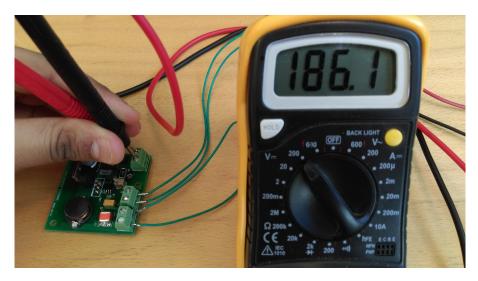

|    | 4.7     | HV MAX1771 Board                                              | 95       |

| 5  | Co      | nclusion                                                      | 96       |

| 6  | Fu      | rther Development                                             | 98       |

| Li | st of A | Abbreviations                                                 | 100      |

| Bi | bliog   | raphy                                                         | 101      |

| At | tachr   | nents                                                         | 104      |

|    | Ι       | Circuit Schematics Echo Sounder                               | 105      |

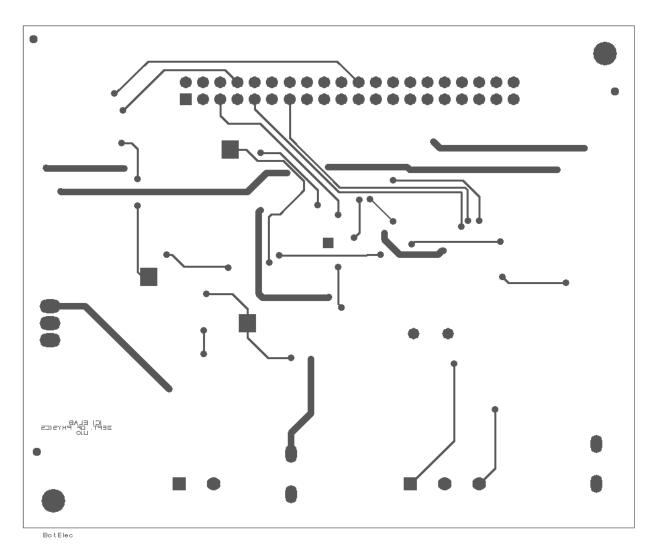

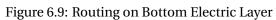

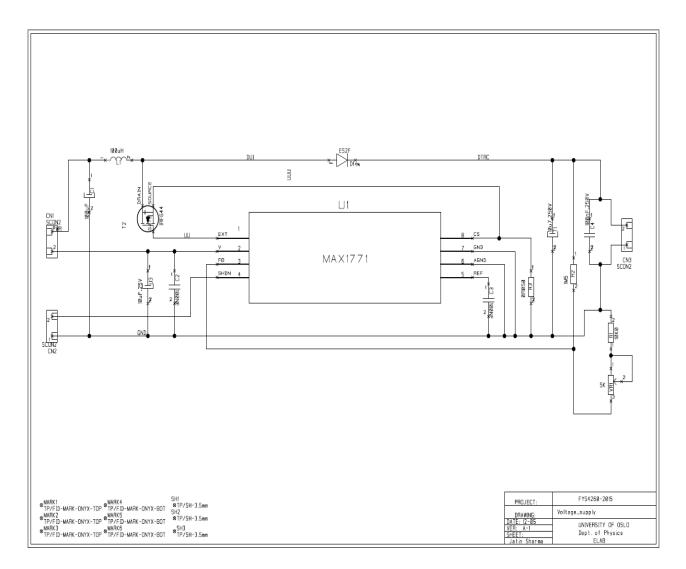

|    | II      | PCB Layout Echo Sounder                                       | 110      |

|    | III     | Circuit Schematics of High Voltage Board                      | 114      |

|    | IV      | PCB Layout of High Voltage Board                              | 115      |

|    | V       | PSpice Simulation                                             | 119      |

|    | VI      | VHDL Code                                                     | 125      |

# **Chapter 1**

# Introduction

# • 1.1 Background

1.1.1 Hydro Acoustics

# • 1.2 Echo Sounder

1.2.1 Earlier Developed Echo sounders • Pros and Cons

# • 1.3 Digital Signal Processing

1.3.1 Programmable Logic- Background1.3.2 What are FPGAs?1.3.3 Hardware Description Language

# • 1.4 Challenge and Motivation

# 1.1 Background

The discovery of traveling of sound in water goes all the way back to the 15th century, when Leonardo da Vinci noticed that he can hear the sound from distant ships by inserting a long pipe in the ocean. In 1827, Daniel Colladon and Charles Sturm collaborated to measure the velocity of sound in water. They conducted this experiment in Lake Geneva, Switzerland. By timing the interval between a flash of light and the striking of a bell underwater, they determined the velocity of sound to a surprising degree of accuracy[6, Page 2].

In the Nineteenth century, phenomenon of "Transduction" was discovered which is nowadays extensively used for sending and receiving sound in water. With the beginning of the twentieth century, several attempts were made to develop such systems which could communicate or detect the targets in water and a number of devices were proposed which used the method of echo ranging. With time, the research expanded in this field of Hydro-acoustics and was used in the study of various targets like fishes, submarines, etc. Today, it is widely used in the biomass estimation, detection of fish school and differentiating between various species of fishes.

## 1.1.1 Hydro Acoustics

Hydro acoustics is the term associated with the study of sound in water and its applications. Sound travels as longitudinal waves in the form of compression and expansion of the molecules of the medium. This alternate compression and expansion phenomenon causes the sound to travel in the medium.

Speed of sound in water is approx. 1500 m/s and it depends upon depth, temperature and saltcontent. Higher frequencies get attenuated, while the lower frequencies can travel long distances in water.

Active hydro acoustic sensing involves making a sound and listening for the echo. The intensity of received echo depends on the intensity of the transmitted wave(Source Level), the loss in intensity as the sound wave spreads in the water and absorbed by water(Transmission loss), the reflectivity of the target(TS), the position of the target in the beam and various losses in the instrument itself. All these processes are combined by a set of equations as:

$$EL = SL - 2TL + TS$$

[6, Pg 23] (1.1)

$$RL = SL - 2TL + sV + V \qquad [6, Pg 23] \tag{1.2}$$

These two Eq. 1.1 and 1.2 are the basic Sonar equations in the field of Hydro acoustics and one can calculate echo level(EL) provided the other parameters are given. These equations are the working relationships that combine the effects of the medium, the target and the equipment. These are very useful in echo sounder designing and also for predicting the performance of Hydro acoustic

#### equipments.

Echoes from most underwater objects differ from the incident pulse in a number of ways other than intensity, as described by the parameter Target Strength(TS). The reflecting object imparts its own characteristics to the echo; it interacts with the incident sound wave to produce an echo that is, in general, different in wave shape and other characteristics from the incident pulse. These differences are useful to sonar engineers in two ways: they may be employed as an aid in detection, as in filtering with narrow-band filters to enhance an echo buried in reverberation; they may also be used to help in target classification to distinguish one type of target from another, as in distinguishing a submarine from a school of fish[6, Pg 322].

# 1.2 Echo Sounder

Echo sounder is based on the principle that water is a very good medium for the transmission of sound waves and that a sound wave will bounce off a reflecting layer, returning to its source as an echo. An Echo Sounder comprises of transmitter(or pulse generator), transducer, analog front end receiver and the digital processing unit. Earlier echo sounders had an indicator or graph recorder instead of Digital Electronics.

Echo sounders are basically SONARs(SOund Navigation And Ranging) i.e. if we take a simple single beam echo sounder and point it in various directions, we get a SONAR. Echo Sounders are more generally used as fish finders or depth sounders.

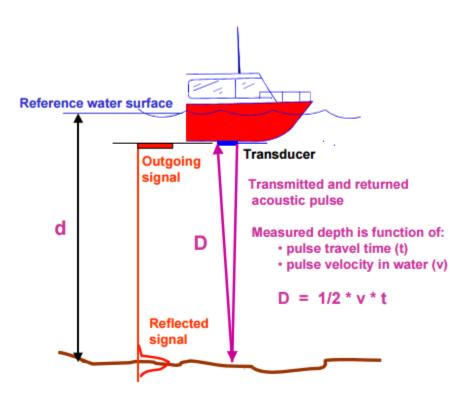

Figure 1.1: Echo sounder Principle[29]

From the expression  $D = \frac{v * t}{2}$ , one can calculate the depth of the sea bed or any other acoustically reflective bottom.

Transmitter is used for sending short pulses of duration  $\tau$  (ms) of a particular frequency. The pulses repeat after certain time interval. Repetition Time is independent of the transducer frequency.

The duration of pulses should be large enough such that transducer can convert the electrical pulses into sound waves. The relation between pulse duration and bandwidth is given by :-

$$BW = 2/\tau$$

[36, Pg. 22] (1.3)

This relation is important while designing the echo sounder because the pulse width should be short but there is a limit. The bandwidth of the transmitted pulse must match with the receiver's bandwidth. There is a trade-off while selecting the echo sounder's bandwidth. It is desired to have a bandwidth large enough which can preserve the information in the received echo, and at the same time it is also necessary that the bandwidth should be as small as possible to limit the ambient noise entering from the sea.

High amplitude pulses from the pulser or transmitter part actuate the transducer. The transducer part is used for converting these electrical signals into sound waves during transmitting and vice versa while receiving.

In the receiver part, the echoes received are of very low amplitude as compared to transmitted pulses. Therefore, they need to be amplified. An echo returning back from 10m has a different intensity than one returning from 80 or 100m. As a result, Dynamic gain range must be set according to the depth of operation.

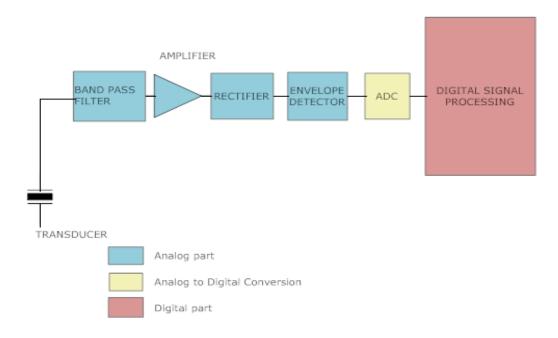

The traditional analog receiver part comprised of filter, amplifier, rectifier, envelope detector and then digital processing as shown below:

Figure 1.2: Earlier Receiver Part

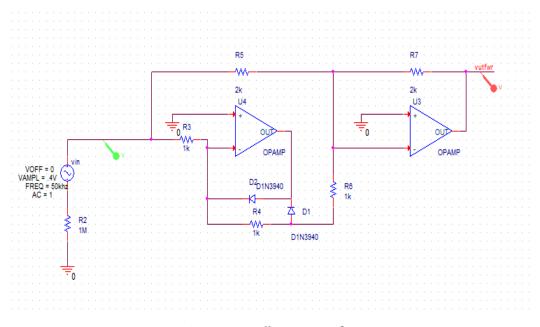

There are certain losses associated with processes like rectification and envelope detection when they are performed in analog domain using op-amps and passive components like capacitors and diodes. A simple schematics of a full-wave rectifier using 2 op-amps, resistors and diodes is shown as:

Figure 1.3: Full-wave rectifier

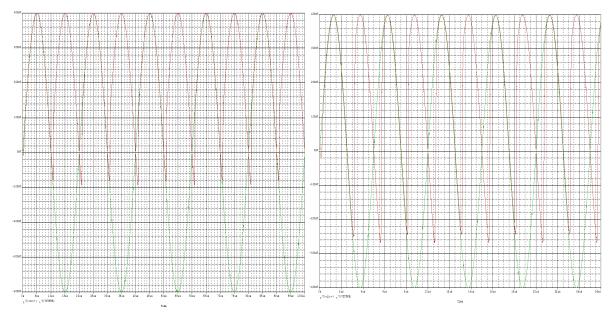

The gain of this rectifier can simply be changed by changing the value of resistor R7[53]. The corresponding simulation outputs of this circuit for 50 and 200kHz using PSpice(Attachment V) are shown here:

Figure 1.4: Simulation-50kHz

Figure 1.5: Simulation-200kHz

As seen from Fig. 1.4 and 1.5, distortion is present in the rectified signal and therefore, this operation is rather done in the Digital Electronics. Same is the case with envelope detection process which implements passive components like super diodes and capacitors.

#### 1.2.1 Earlier Developed Echo sounders

The Hydro-acoustics group at Physics Institute, UiO has been working with the development of Echo sounder and SONAR technology from quite a long time. In earlier Echo sounders, Analog Electronics comprised a major portion. With time, the Analog Electronics began to be replaced with Digital Electronics.

Before starting the project, it is necessary that one should have a thorough knowledge about what has been done earlier in this field and to learn from others mistakes. This will help in improving the results, coming up with new and efficient solutions and saving time.

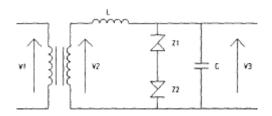

The analog front end receiver proposed by Morten Hellum[4] comprised of a transformer, 2nd order resonance circuit and a pair of back to back Zener diodes as the receiver network. This receiver unit had a high Q(Quality) factor and a Bandwidth of 4kHz. This was a very good solution and was used in the Analog front end by many students.

Figure 1.6: Hellum's Front End Receiver[4, Pg. 10]

This front end focuses on improving the Signal to Noise Ratio(SNR) of the received echo. The impedance caused by the Inductor at 50kHz is very large(2.5kOhm) and is much greater than the transducer impedance such that the load during transmission is virtually only constituted by the transducer[4, Pg. 18]. The Zener diodes together with the inductor protect the receiver amplifier during pulse transmission. The LC circuit also acted as a Bandpass filter and helped in removing the noise signals from the signal. On the transmitter side, Hellum describes about the use of Push-Pull Transistors for the generation of pulses.

The receiver hardware developed by Dr. Balk[36] gives outputs at 3 different channels. Each channel had a Bandpass filter with 4kHz bandwidth. All the channels had different amplifications for improving the dynamic range of the system with Channel 0 having 0dB gain for high amplitude signals, while Channel 1 and 2 had 50dB and 100dB Gain for comparatively low amplitude signals in the range of mV and  $\mu$ V respectively. Thus making the total dynamic range of the receiver to be 150dB. In this design, Hellum's front end[36, Pg. 64] was also implemented. These echo sounders were designed to operate at a single frequency.

#### **Pros and Cons**

There were certain advantages and limitations in the previously developed systems and these pros and cons were kept in mind while designing the system.

The transmitter Electronics earlier developed was designed in combination with the transformer. Transformer connects the transmitter, transducer and receiver together, but a smaller and more efficient solution needs to be implemented which is only used for isolating the receiver side while transmission and get rid of bulky and space consuming transformer.

The earlier front end receivers implemented LC resonance circuit and were very efficient and simple in implementation. It was useful for improving the signal strength and at the same time provided protection against high voltages. But, these solutions were useful for narrow band applications i.e. they allowed only a specific frequency to pass through them. This project deals with the development of a Wide band receiver circuit. Therefore, the circuit must be designed for a wide frequency band operation which can work with different frequencies.

# 1.3 Digital Signal Processing

With the advancement in technology, the analog front end is merging within the digital electronics section and more and more processes now take place in the Digital domain.

## 1.3.1 Programmable Logic-Background

After the Analog Front End, there has to be a digital part which can process the signal and use it for displaying, saving or editing afterwards. Earlier in digital Electronics, the trend was to use a set of specialized discrete logic circuits, to obtain specific outputs. In order to create a slightly complex design, one needed to add few tens of such chips on a single board. This resulted in complex board layout and reduced performance. To improve performance, *programmable logic* method was introduced. The advantage of this method was its high speed of implementation[5, page 10].

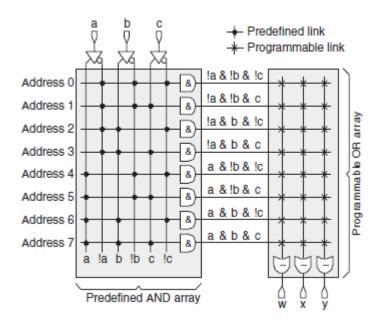

Programmable Logic Devices(PLDs) started arriving in 1970s in the form of Programmable readonly memory(PROMs). PROMs can be visualized as devices consisting of a fixed array of AND functions driving a programmable array of OR functions. These devices were initially intended for use as memories to store computer programs and constant data values. However, they were also found to be useful for implementing logic functions such as lookup tables and state machines[1, Pg. 16]. A 3-input, 3-output PROM in its unprogrammed state is shown here.

Figure 1.7: Unprogrammed PROM[1, Pg 30]

In order to step up the PLD ladder and address the limitations imposed by PROM architecture, Programmable Logic Arrays(PLAs) were introduced around 1975. These were the most user configurable of the simple PLDs as both the AND and OR arrays were programmable here. Unlike PROMs, the number of AND and OR functions in their respective arrays are independent of the number of inputs to the device[1, page 33].

There were some speed limitations associated with PLAs. So a new class of device called Programmable Array Logic(PAL) was introduced in the late 1970s. Conceptually, PALs are almost the exact opposite of PROMs as they have a programmable AND plane and a fixed OR plane and usually include registers[5, page 12].

With time, there was a need to build bigger logic circuits and PLAs and PALs could not be implemented in large circuits because large number of fan-ins and fan-outs involved. Therefore, Complex Programmable Logic Devices(CPLDs) replaced them. CPLDs consist effectively of a number of PAL-like macro cells that can communicate through programmable interconnect[5, Pg. 12].

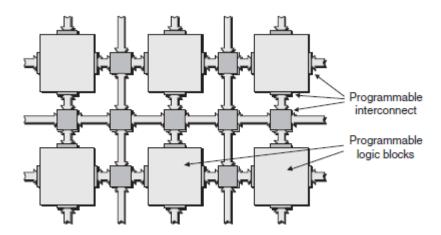

Another technology for implementing digital logic was introduced in 1980s which was based on "Gate Arrays" and was called Field Programmable Gate Arrays(FPGAs).

#### 1.3.2 What are FPGAs?

FPGAs are digital integrated circuits(ICs) that contain configurable blocks of logic along with configurable interconnects between these blocks. Depending on the way in which they are implemented, some FPGAs may only be programmed a single time, while others may be programmed over and over again. The term "Field Programmable" implies that the device is programmed by the customer i.e. in the "field" and not by the manufacturer. The advantage of using FPGAs over CPLDs is that the former can be implemented for complex designs and based on Look-up tables(LUTs) while the later ones are for simpler designs[1, Pg. 17].

Figure 1.8: Top-down view of simple FPGA architecture[1, Pg 43]

LAB(Logic Array Block) is the Altera name for a programmable logic block containing a number of logic elements(LEs), where LE is the core building in a modern FPGA Architecture from Altera. Among other things, LE comprises of a 4-input Lookup table(LUT), a multiplexer and a register[1,

Pg 503].

FPGAs are quite flexible, can contain millions of Logic gates and implementing design changes in them is much easier as compared to other logic devices. This results in widespread use of FP-GAs in the market. Among the various areas of their use, Digital Signal Processing(DSP) is the area where they are in a huge demand. In this project, FPGAs will provide the DSP support.

# 1.3.3 Hardware Description Language

It is a fact that capturing a large design at the gate level of abstraction is prone to error and a timeconsuming process. Thus, some EDA vendors started to develop design tools and flows using the Hardware Description Languages(HDLs) [1, p. 153].

Different levels of abstraction like Behavioral, Functional, Structural are followed by the HDLs for data flow. To make these HDLs easily accessible by the customers, an industry-standard HDL was needed.

To fulfill this requirement, Verilog HDL was introduced in the mid-1980s. Verilog was reasonably strong at the structural level of abstraction, very strong at functional level and it supported some behavioral constructs. One very good feature of this language was that Verilog programming level interface allowed the external software programs to pass data into an application and access data from that application[1, p. 164].

In 1980, U.S. Department of Defense(DoD) launched the very high speed integrated circuit(VHSIC) program with purpose of advancing in digital IC technology. In 1985, the first official release of VHSIC HDL(VHDL) occured[1, p. 167]. VHDL is very strong at functional and behavioral levels of abstraction and it supports some system level design constructs. In order to encourage acceptance by the industry , the developers subsequently donated all rights to the VHDL language definition to the IEEE in 1986.

VHDL was used in this project for providing the digital logic.

# 1.4 Challenge and Motivation

From a long time, Echo sounders have been extensively used in Hydro-acoustics research applications like seabed mapping, fish stock measurements, water quality monitoring, etc. In case of fish detection, Echo sounders can easily see targets and measure its size and strength. But a major challenge involved here is the recognition of species. It is difficult for echo sounders to get information about the same sized fishes of different species.

With the help of multi-frequency technologies, targets can up to some extent be classified into three categories:- plankton, fishes with and without swim bladders, but it is almost impossible to see the differences between species within these classes.

A solution to this problem could be the implementation of echo signature method where the shape of the returned echoes is studied. Echo's shape is very helpful to get the specific details of the target species. The echo sounders developed here at the Physics Institute used a band pass filter in the Analog front end receiver. The purpose of using filters was to suppress noise and therefore, improve Signal to Noise Ratio(SNR). But these filters also contributed in smoothing the echo shape. Thus hindering any further study of the echoes which were containing information about species recognition.

So, there is a need to develop a new Echo sounder which can give this information. For this purpose, the design of front end receiver should be reconsidered.

The receiver will be developed for wide band applications and can be used for different frequencies rather than a particular frequency. It will maintain the SNR and also provide the necessary gain for different sized targets at different depths. This dynamic gain can be achieved with the help of Logarithmic compressors or by using multiple amplifiers one after another. Voltage Amplifier chain will be the preferred method for this purpose because of huge literature resources and technical solutions available for its application. Moreover, dynamic span can be changed easily and set according to echo sounder's operation.

To build and test receiver's operation, it is desired to have both the transmitter and receiver on the same board. Earlier echo sounders used BJTs in the transmitter electronics which were connected to the transformer. This project will also look into other methods of pulse generation and amplification than the already developed solutions.

# **Chapter 2**

# **Material and Methods**

#### • 2.1 Softwares used in this project

2.1.1 OrCAD 2.1.1.1 OrCAD Capture 2.1.1.2 OrCAD PSpice

2.1.2 CADSTAR

2.1.3 QUARTUS

2.1.4 Ultra Librarian

#### • 2.2 System Description

Level

2.2.1 Pulse Generation

2.2.2 Alternate option for voltage amplification

2.2.3 Transducer

2.2.3.1 Choice of Transducer

2.2.3.2 Measurement of impedance of transducer

2.2.4 Receiver Input Protection

2.2.4.1 Filtering

2.2.4.2 Using Switch as a receiver protector

2.2.5 Compensation for Transmission Loss and Amplification

2.2.5.1 Understanding Source Level, Transmission Loss and Echo

2.2.5.2 Gain Amplification

2.2.6 Digitalization of received echoes

2.2.7 Envelope Detection

# 2.1 Softwares used in Project

# 2.1.1 OrCAD

OrCAD is a software tool suite for Electronic Design Automation owned by Cadence Design Systems. It is used for creating Electronic schematics and prints for generating PCBs.

## 2.1.1.1 OrCAD Capture

OrCAD Capture is a Schematic tool and has an in-built library for discrete components. New components can be added when necessary in the form of .olb files. The required library files are obtained from the vendor's website for the desired component and is added into OrCAD Capture with the help of the tool PSpice Model Editor.

## 2.1.1.2 OrCAD PSpice

After finishing with the Schematics part, OrCAD Capture exports the net-list to an external simulator known as OrCAD EE PSpice. OrCAD PSpice is a simulation tool for checking the analog verification of the circuit. The results of the simulations can be graphically displayed in a separate window.

This tool is very useful to get a knowledge of working of the circuit and is also used in the course, FYS3220.

A licensed version of OrCAD 16.6 available at E-Lab was used in this project.

## 2.1.2 CADSTAR

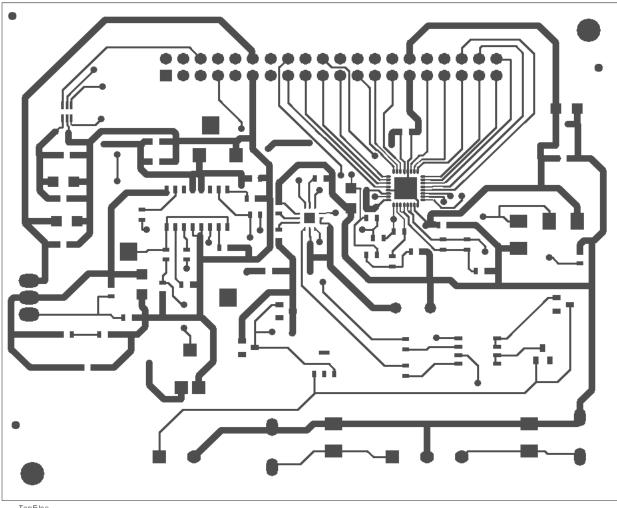

For developing the hardware part, a development tool from Zuken called CADSTAR is used. This is a licensed tool and was chosen because it was already available at E-Lab with a very large library of components with symbols and footprints. The hardware part starts from designing of the basic schematics design and then transferring the schematics(.scm) to the actual .pcb format. In .pcb file, components are placed by following some specific rules of production. Thereafter, routing between the various components is done in PR Editor XR. Tracks with different widths are used for routing depending upon the type of signal.

CADSTAR Version 15.0 was used for the hardware development.

# 2.1.3 QUARTUS II

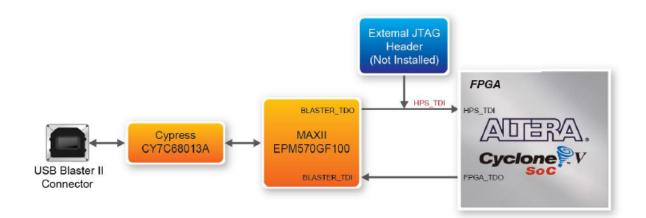

Quartus II is a programming software tool by Altera. It is a free software for implementing the VHDL and Verilog languages for describing the hardware. It can be used to program FPGAs and CPLDs. Altera Board used in this project is DE1-SoC and the language used for writing the code is VHDL. The code is first compiled and then, implemented in the hardware part using the JTAG mode.

ModelSim is also a tool form Altera used for simulation and debugging of the digital logic. It can be used to check the timing requirements.

Quartus II Web Edition 14.0 was downloaded from Altera's website to be used in this project.

# 2.1.4 Ultra Librarian

Ultra Librarian is a free tool from Accelerated Systems used for importing and building libraries for CAD tools. It is useful for creating symbols and footprints of components and can support multiple CAD tools. These symbols and footprints can then be added in the libraries for PCB designing purposes.

# 2.2 System Description

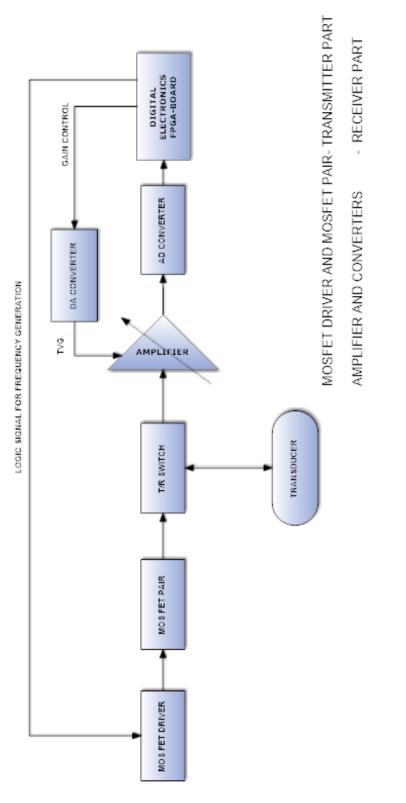

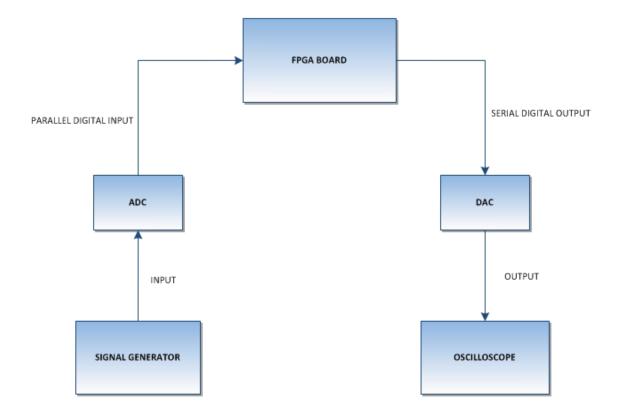

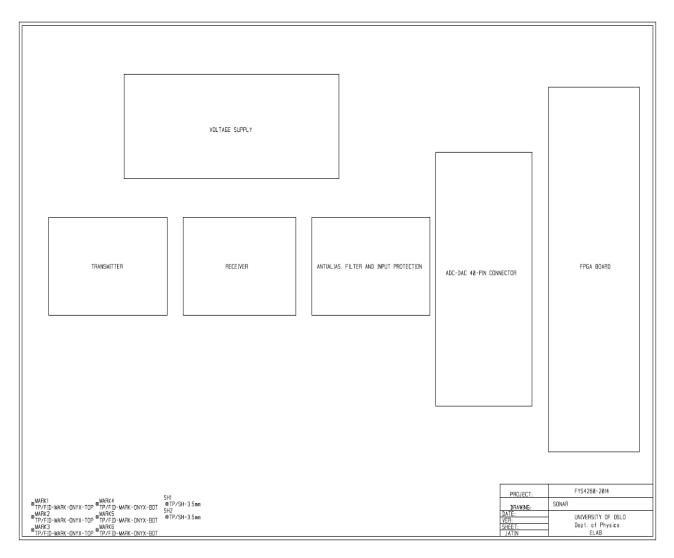

The whole Echo sounder system is developed by combining the various units in subsystems like Transmitter, Receiver and Transducer.

This section will give a brief description about the various processes taking place in the Echo sounder system for solving the problems as discussed in Section 1.4. The motive is to develop a Hardware system containing all the necessary units on a single PCB board and then checking its operation.

The various tasks carried out by the system are described as follows:

- Generate pulses of desired frequency and duration and send them to transducer for conversion

- Generate High Voltages from an external board and connect it to the Echo sounder system for raising the amplitude of pulses

- Implement a protection circuit between the Transmitter and Receiver for wide band application

- Receive the low amplitude echo signals from the transducer and compensate for the Transmission Loss with the help of TVG

- Use digital method for Envelope Detection of the received pulses

The sketch in Fig. 2.1 shows how the various components are connected.

# SIMPLIFIED SKETCH OF ECHO-SOUNDER SYSTEM

Figure 2.1: Overview of complete Echo Sounder System

## 2.2.1 Pulse Generation

Electrical pulses are generated using digital logic before converting them into acoustic pulses with the help of a transducer.

For generating the electrical pulses, there should be a trigger pulse present which decides the rate at which pulses will be fired from the echo sounder. It is also called Pulse Repetition Frequency(PRF) and is important because it must always occur at a precisely defined interval of time. PRF depends on the depth of water to be surveyed i.e. time interval long enough between pulses so that all the echoes resulting from first transmission have returned, before the next transmission. Otherwise, it will affect the echo sounder's proper operation.

The time interval between the successive bursts is decided by the sound's velocity in water, c and the total distance traveled by the pulse i.e. with increasing distance, the time between bursts will increase.

The expression is given by:

$$Time = 2 * depth/c$$

[36, Pg. 24] (2.1)

Let depth = 75m Therefore, Total distance traveled = 150m

So,

$$Time = 150/1500 = 0.1sec \tag{2.2}$$

It means that time interval between successive bursts should be around 100ms.

$$PRF = 1/Time_Interval \tag{2.3}$$

Therefore, Maximum PRF should be 10Hz or 10 bursts per second.

The trigger starts the process of generation of pulses of desired frequency and duration. The pulses are generated through Pulse Width Modulation(PWM) technique. These Square wave pulses have a 50% duty cycle i.e. each pulse, for half of the time it is in positive cycle and in the next half it is in the negative cycle. These electrical pulses usually have a defined frequency like 50, 70 or 200kHz and their duration is decided by the number of cycles. This pulse duration is called tau( $\tau$ ) and is usually in the range .1-.5ms for better resolution. So, for a 50kHz pulse the number can be between 5-25 cycles.

When this  $\tau$  is multiplied by  $\frac{c}{2}$ , range resolution is obtained. Range resolution is important to determine the minimum distance between targets i.e. between two fishes, so that their reflected echoes do not overlap each other and can be prevented from being shown as a single signal at the receiver end. Therefore, with smaller  $\tau$ , better resolution can be achieved.

| Frequency(kHz) | Time Period,1/f(µsec) | No. Of Cycles | Pulse duration,τ(millisec) | Bandwidth,2/τ(kHz) | Pulse Length,c*τ(meter) | Range Resolution,c*τ/2(meter) |

|----------------|-----------------------|---------------|----------------------------|--------------------|-------------------------|-------------------------------|

| 50             | 20                    | 10            | .2ms                       | 10                 | 0.3m                    | 0.15m                         |

| 50             | 20                    | 15            | .3ms                       | 6.6                | 0.45m                   | 0.225m                        |

| 50             | 20                    | 20            | .4ms                       | 5                  | 0.6m                    | 0.3m                          |

| 50             | 20                    | 25            | .5ms                       | 4                  | 0.75m                   | 0.375m                        |

|                |                       |               |                            |                    |                         |                               |

| 200            | 5                     | 40            | .2ms                       | 10                 | 0.3m                    | 0.15m                         |

| 200            | 5                     | 60            | .3ms                       | 6.6                | 0.45m                   | 0.225m                        |

| 200            | 5                     | 80            | .4ms                       | 5                  | 0.6m                    | 0.3m                          |

| 200            | 5                     | 100           | .5ms                       | 4                  | 0.75m                   | 0.375m                        |

Figure 2.2: Table showing relation between pulse duration, cycles and bandwidth

As seen from the above table, the smaller is the pulse duration, the larger will be the bandwidth. This means that such a transducer should be chosen that allows these small duration pulses to pass through it without affecting them. But the noise entering the receiver system puts a limit on transducer's bandwidth.

After generating pulses of desired time duration, it is then necessary to amplify them up to a certain level so that the output power is raised to around 50-100 watts. This output power varies with the transducer resistance. Conversion of this electrical energy into sound energy is also dependent on transducer's efficiency. As no transducer is 100% efficient, so there is a definite power loss while conversion. Impedance matching between the transmitter and transducer should also be kept in mind for effective energy conversion.

In this project, MOSFETs are used instead of BJTs in the Transmitter Electronics. Also, the transmitter is connected directly to the transducer.

## 2.2.2 Alternate option for voltage amplification

Using a transformer in the transmitter part is the most common approach used in the echo sounder designing because of simplicity in design but they have certain losses like core loss, copper loss, etc. associated with them. Copper losses change with load and for wide band systems, where the transducer offers different loads at different frequencies, efficiency of transformer is affected.

The transmitter circuit which is in use today can generate a sound pulse with power in the range 40-60 Watt when it is driven at its full strength[15, Pg. 16]. Therefore, if it is necessary to increase the transmitted power, say up to 100 W, this solution must be replaced.

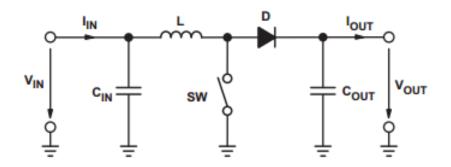

An alternative could be to generate high voltages using Switched Mode Power Supply(SMPS) method. Here, a boost converter (step-up converter) technique is used to raise the voltages from low to high. The operation is based on the principle that the voltages which are obtained, are from the rapidly collapsing magnetic field in an inductor. This is done a number of times in a second and the obtained output pulses are then smoothed. The advantage of this design is that it is small, cheap and very efficient. Therefore, this method has been used in this project. The basic configuration of boost converter is shown here.

Figure 2.3: Basic schematic of Boost Converter[50, Pg. 1]

An IC is used in combination with the switch to complete the circuit. The working of boost converter is based on the switch's Open and Closed state. In the Closed state, Inductor stores energy by generating a magnetic field and there is an increase in Inductor Current and in the Open state, the magnetic field created will be destroyed to maintain the current flow towards the load. The capacitor at output together with the inductor forms a filter which filters the train of pulses to produce a DC output voltage[51]. The output voltages can be adjusted by using a potentiometer.

Here, a N-channel MOSFET will act as a Switch. The board will get its input power from an external 12V supply.

These output voltages are then given to the transistors on the Echo sounder board to amplify the incoming pulses. These transistors should have very fast switching speeds and capable of handling high voltages.

## 2.2.3 Transducer

#### 2.2.3.1 Choice of Transducer

The transducers convert one form of energy into another and the transducers used in hydro acoustics convert voltage(electrical) signals into sound signals and vice-versa. These also acts as filters at the resonant frequencies while receiving the signal and thus remove the surplus noise and increase the signal to noise ratio. The impedance of the transducer elements decrease at the resonant frequency.

The piezoelectric transducer element used in this project is FURUNO 520-5PSD which has two resonance frequencies centered around 50 and 200 kHz. This transducer acts as both transmitter and receiver of signals. This transducer can be considered as the first band pass filter in the receiver electronics. The various characteristics of this transducer are:-

- Maximum power: 600 W

- Beam angles : 46/10 degrees

- Plastic Thru-Hull

- 8-meter Cable with 10-pin connector

Every transducer has a certain bandwidth. For this transducer, it is around 5kHz[28, Pg 71].

#### 2.2.3.2 Measurement of impedance of transducer

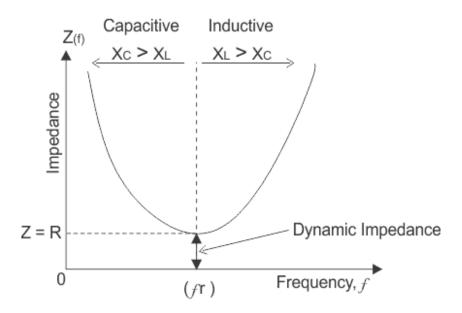

The impedance vs frequency curve of a transducer can give a lot of information about its various characteristics such as, it can provide information for impedance matching of transmitting and receiving systems with transducer. It is used for computation of transducer efficiency and driving current or voltage from transmit responses. And this response can be used to find the values of the discrete components of the equivalent electrical model. Therefore, there is a need to measure transducer's complex impedance.

The transducer's electrical impedance affects the transducer's noise performance, driving response, bandwidth and sensitivity. In the frequency function, the impedance tends to change values rapidly, in particular where resonances are involved. This transducer will show an impedance drop at its two resonant frequencies. At resonance, the impedance is purely resistive and the inductive and capacitive impedances cancel each other as voltage and current come in phase. This impedance is small and therefore, the current increases. To determine the response, an AC voltage source is added to the circuit. Typically, the circuit used to measure impedance is basically a constant current circuit[39], i.e. here the current does not depend on the impedance measured value but only on the external resistance R.

Figure 2.4: Impedance vs Frequency response[26]

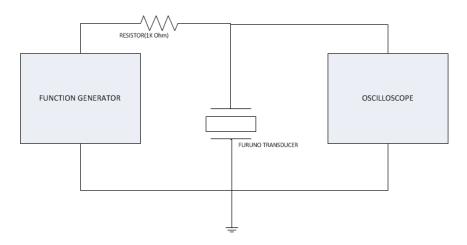

In this setup, HP 33120A function generator is used to provide an AC sweep voltage of 5V between two particular frequencies to the transducer through a 1K Ohm resistor(R). The response is observed with the help of Tektronix DPO 2004B oscilloscope which is connected to the resistor(R) and the transducer. At resonance frequencies of 50 and 200kHz, the impedance of transducer changes drastically.

Figure 2.5: setup

The resistor(R) used here together with the transducer acts as a voltage divider circuit. A si-

nusoidal voltage sweep between 10kHz and 250kHz was given as the input. The provided setup is used to calculate the resistances at the resonant frequencies 50 and 200 kHz.

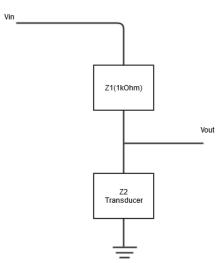

Figure 2.6: Voltage Divider Circuit

The impedance calculated at the resonant frequency of 50 kHz is given by:-

$$V_{out} = \frac{Z_2}{Z_1 + Z_2} * V_{in} \qquad [23, Pg. 187]$$

(2.4)

Here,  $V_{in}$  = 5V,  $Z_1$  = 1K Ohm and  $V_{out}$  is calculated to be 0.8 V at 50 kHz.

Using the equation 2.4,  $Z_2$  is found to be 190.48 Ohm. This is the impedance(or resistance) of the transducer at 50kHz.

Similarly, for 200 kHz  $V_{out}$  is found out to be 4.1 V and the impedance is calculated to be 4494.51 Ohm.

## 2.2.4 Receiver Protection Circuit

A protection circuit needs to be used to protect the receiver electronics against the high voltages coming from the transmitter.

- Filtering

- Using Switch as a receiver protector

#### 2.2.4.1 Filtering

The signal received by the transducer will not comprise of a pure echo signal but it will be surrounded by ambient noise from sea and the Electronics equipment will also contribute to this noise. The noise can contain frequency components which can be both higher and lower than the pulse's center frequency. Therefore, it becomes necessary to filter out the unwanted noise from the received echo.

Earlier developed receiver front ends had a filtering circuit for filtering out the noise like the one developed by Randgaard used Op-amps for making Bandpass filters with center frequencies of 10 and 70kHz[3, Pg. 16]. Hellum also developed a passive filter which comprised of a LC circuit[4, Pg. 9]. These filters help in filtering out the desired frequency signal from the unwanted frequency signals and at the same time provide a certain amplification to the received signal, i.e. improve SNR depending upon the configuration of the circuit. The Inductor used in this LC circuit was specially constructed at E-Lab and built for operation at 50kHz only. This puts a limitation on this filter to be used as a front end for other frequencies.

These circuits are applicable only in narrow band receiver circuits. The other disadvantage associated with these filters is that the system gets locked for a particular frequency like 50 or 70kHz. So, for wide band receiver development these circuits are not optimal. The echo sounder system should be developed in a way that it can operate with different frequencies in the area 50-200kHz without changing anything in the hardware circuit. This way, the center frequency can be changed easily in the digital part when desired.

#### **Option considered**

As far as filtering of the received echo is concerned, the transducer itself assists in filtering and helps in removing the unwanted signals in advance.

I decided not to use any filter before the amplification stage for making the system flexible for operation at various frequencies. The other major advantage is that by doing so the echo signal

will now remain unaffected and useful information about species recognition can be obtained from the later envelope detection part.

Hellum's front end, apart from filtering also helped in protecting the receiver from the high voltages. So, there is a need to isolate the receiver from the transmitter during transmission by inserting a protection circuit between the two. Among the available solutions, a choice was made to use a simple circuit which does not require any external control signals for its operation.

#### 2.2.4.2 Using Switch as a receiver protector

A switch was introduced between the transmitter and receiver. The switch considered, should be capable of protecting the receiver side and remains normally closed i.e. in receive mode because the pulses are sent at a very low frequency of around 10Hz. It means that the total time the Switch has to remain open during a time interval of 1sec will be less than 10ms. This should allow the low amplitude signals from the transducer pass the switch unattenuated. But as soon as the voltage rises and it passes a certain level of amplitude, the switch protects the receiver by going in Open/Disconnected state. Thus, providing isolation between transmitter( $T_x$ ) and receiver( $R_x$ ) Electronics.

Moreover, it is preferred that it should be a user friendly component having small size and very less number of pins such that it can be easily tested in the lab before it is used in the design.

#### 2.2.5 Compensation for Transmission Loss and Amplification

The acoustic pulse while traveling through the medium experiences Transmission Loss(TL). This loss is mainly due to spreading and attenuation. The spreading loss is a geometrical effect representing the regular weakening of a sound signal as it spreads outward from the source and this loss increases with the range[6, Pg. 100]. This affects the signal's strength and as a result, the echo which is received has a very low amplitude. Therefore, this loss needs to be compensated.

#### 2.2.5.1 Understanding Source Level, Transmission Loss and Echo Level

There is a relation between the projector's Source Level(SL) and the input power and is given by:-

$$SL = 171.5 + 10Log(P_e) + 10Log\eta + DI_T \quad [6, Pg 75]$$

(2.5)

; where  $P_e$  is Electric Power,

$\eta$  is efficiency of transducer and assumed to be 50%

For FURUNO 520-5psd Transducer, the Directivity Index(DI) is 13dB[28, Pg 88]. Using 100W as transmitting power, we have:-

$$SL = 171.5 + 10Log(100) - 3.01 + 13$$

(2.6)

It implies that:

$$SL = 171.5 + 20 - 3.01 + 13 = 201.4 dBre1uPa$$

(2.7)

The transmission loss responsible for the weakening of the pulse strength is given by the equation :-

$$TL = 20Log(R) + aR \quad [6, Pg\ 111] \tag{2.8}$$

, where  $\alpha$  is the absorption coefficient and 20Log(R) is the spreading loss.

The signal looses its strength both ways, while going towards target and coming back from it, so losses are considered equally in both directions. Value of  $\alpha$  is dependent on various factors such as viscosity, frequency, ionic relaxation of salts like Magnesium Sulphate. Therefore, the losses caused by  $\alpha$  are dependent on the medium and cannot be decreased.

For long distance(R = 100m), Transmission Loss is calculated out to be :-

$$TL = 20Log(100) = 40dB$$

(2.9)

Therefore, TL > 40 dB because losses caused by  $\alpha$  also need to be included. As  $\alpha$  depends on frequency, it will have different values at different frequencies, E.g.  $\alpha$  for 50 and 200kHz is .009dB/m

and .05dB/m respectively.

The next step is to find the Target Strength(TS) from a small fish. Assuming that the length of the fish is 13cm, then TS of this fish for two different frequencies, 50kHz and 200kHz can be found out by equation:-

$$TS = 19.1\log_{10}(L) - 0.9\log_{10}(f) - 62.0 \qquad [6, Pg. 316]$$

(2.10)

For 50kHz :-

$$TS = 21.2 - 4.22 - 62.0 = -45.02 dB \tag{2.11}$$

Similarly for 200kHz :-

$$TS = 21.2 - 4.77 - 62.0 = -45.57 \, dB \tag{2.12}$$

As seen TS mainly depends on the fish size. So, bigger size fishes will produce greater TS.

Now to find the EL, there is a need to use the Sonar equation Eq.1.1:-

$$EL = SL - 2(20\log R + aR) + TS$$

(2.13)

So for 50kHz frequency,

$$EL = 204.5 - 2(40 + .9) - 45.02 \tag{2.14}$$

Therefore, EL =

$$77.68$$

dBre1 $\mu$ Pa

And finally it is desired to find the voltage produced across the transducer terminals, which is given by:-

$$V_{Trans}(dB) = EL + SRT$$

[4, Pg. 25] (2.15)

;where SRT = Receiving Response of transducer and is equal to -184 dBre1V/ $\mu$ Pa[28, Pg 94]

It implies that:-

$$V_{Trans} = 77.68 - 184 = -106.32 \, dBV \tag{2.16}$$

which is equivalent to  $4.8\mu$ V.

So, a small fish produces this much voltage across transducer terminals and receiver must be efficient enough to process echo with this level of amplitude.

For compensating this loss of amplitude due to these various phenomenons like transmission, scattering, absorption, etc. an algorithm needs to be followed which can raise this received signal's amplitude to a level which can be easily processed by the following receiver Electronics.

#### 2.2.5.2 Gain Amplification

To provide the necessary gain to the echo signal, an amplifier is needed. This can be achieved by providing fixed amplification as implemented by Dr. Balk[36, Pg. 69] using Op-amps and discrete components in its various channels. But it is desired to have a digital control over the gain range. Therefore, it is advantageous if an amplifier is used whose gain can be changed digitally.

A single amplifier can provide the necessary gain but the Bandwidth will decrease accordingly with gain due to the Gain-Bandwidth(GBW) product. So, it is practical to use more than one amplifier to raise the low amplitude echoes. Connecting amplifiers in series, where each amplifier sends its output to the input of the next amplifier is the technique used for amplification. This also improves the attenuation of out-of-band interferes, since cascaded stages have a sharper high-frequency roll-off for the same effective gain-bandwidth product, compared to a single-stage amplifier[16, Pg. 16].

As stated above, the gain required should be large enough so that output voltages are in the operating range of ADCs. To achieve this goal, the number of cascaded amplifiers needs to be chosen according to the gain required. A large number of amplifiers are available from different vendors. But only the amplifiers with the variable gain characteristic should be used for this purpose. This is because echoes from targets i.e. fishes at different depths will require different gain due to different ranges covered by the signal. As the intensity of the signal falls directly with the distance traveled and thus, with time. Therefore, Variable Gain should be dependent upon time i.e. the purpose of applying Time Variable Gain(TVG) here is to reduce the dynamic range of echo signal and adapt it to the dynamic range of the ADC[38].

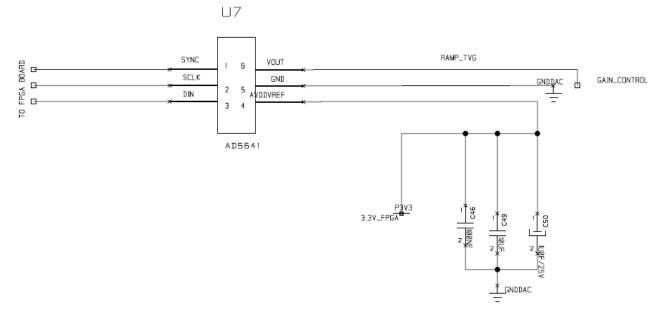

TVG is accomplished by generating a voltage waveform of a defined wave shape and applying it to the receiver amplifier. The TVG can be controlled either digitally or by analog voltage. For the simplification of instrumentation and for ease of adjustment, TVG action can be obtained by charging a capacitor with a negative voltage during the transmission cycle, and after this cycle, discharging the capacitor through a shunt resistor. The over-bias voltage then decays exponentially to the normal bias level. Thus, the amplifier is designed to have a gain in dB that is approximately linear with the bias voltage[40, Pg. 314]. But it is more accurate to provide the TVG digitally with the help of a Digital to Analog Converter(DAC) or Digital Potentiometer. A precise TVG can then be achieved and changed accordingly with range and incoming signals. The output analog voltage from DAC can then be given to the variable amplifier as gain control voltage.

This TVG should compensate for the following Transmission Loss(TL) vs. Range curve.

#### Transmission Loss (TL)

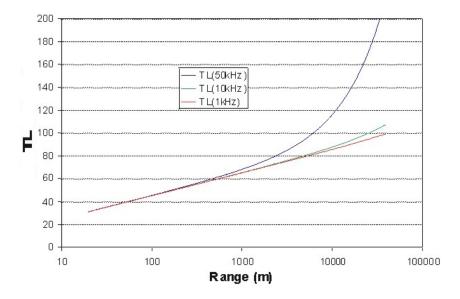

Figure 2.7: Transmission Loss vs. Range[41]

For the ultrasound systems, all the amplifiers require a common analog voltage for gain control and it becomes easier to achieve gain with a single control voltage routed to each VGA.

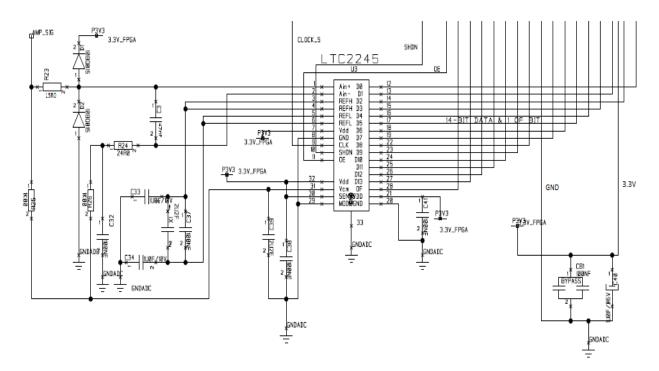

#### 2.2.6 Digitalization of received echoes

After amplification, it is required to convert the analog voltage into digital values. An Analog to Digital Converter(ADC) is required for this conversion. These digital values are then sent for further signal processing. These values could be provided serially or in parallel form depending upon the choice of the ADC. Generally, serial operation requires more clock cycles than the parallel operation to send a digital value.

The ADC is the important component of this design and therefore, it needs to be protected against the time varying input signals. These signals may sometimes exceed the input range that is specified in the manual of that ADC. So, a protection circuit must be employed at the inputs of the ADC so as to avoid damage. There are ADCs available in the market which can operate at higher input voltage than their supply voltage. Most of the ADCs today have internal protection diodes, which conduct when the input voltage goes beyond the supply voltage. But these diodes are not efficient for large currents for a longer amount of time.

#### **ADC Input Protection**

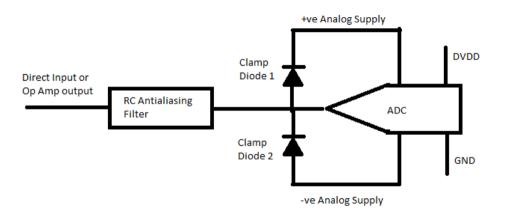

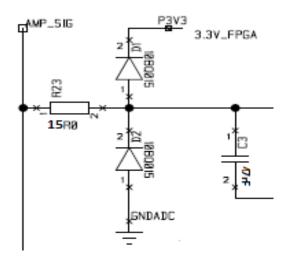

A good solution for protecting ADC is to use a pair of Schottky diodes at its inputs. This method is feasible if the input signal is directly connected to the ADC input or the signal conditioning amplifiers are operating at voltages greater than the ADC analog supply voltage. In this design, this

method is employed to protect the ADC for the later case when the incoming amplified signal is very large due to reflections from targets in water which are very close to the transducer.

For protection purposes, the diodes are placed at the input after anti-aliasing RC filter. It is little bit advantageous to place them after the filter because resistance acts as a current limiting device if the input goes beyond the input range of ADC. Also, if the input current goes too high, the resistance will itself get damaged but will protect the clamping diodes and the ADC[10, Page 2]. The anode of upper diode and cathode of the other are connected to the input signal and the other end of upper and lower diode are connected to positive and negative supplies respectively.

This method is applicable for single supply ADCs also. If the ADC is working only on positive supply say 3.3V, then the anode of the lower diode is connected to the ground.

Figure 2.8: ADC Input protection[10, page 2]

#### Simulation and testing

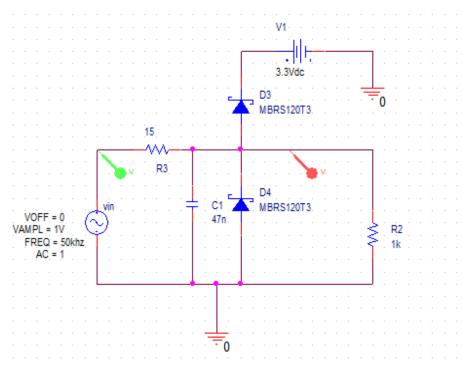

The ADC chosen operates only on single positive supply. So, only cathode of upper diode needs to be connected to the voltage supply. It will be advantageous if the response of this protection circuit is checked beforehand. Therefore, the circuit in Fig.2.8 is drawn using OrCAD to perform simulation.

Schottky diodes 10BQ015 were used in the design but for performing simulations, MBRS120T3 diodes were used and added in PSpice library. This was done because their values resembled with the actually used Diodes 10BQ015 and their library(.olb) files required for simulation were easily available.

The setup is shown here showing both anti-aliasing filter and ADC input protection circuit. The response is checked by giving high and low input voltages from an AC source. The Schottky diodes clamp the positive cycle of input voltage if it goes above the supply voltage,  $V_{DD}$ = 3.3V, whereas no change takes place in the positive cycle if amplitude is less than  $V_{DD}$ .

Figure 2.9: Simulation setup

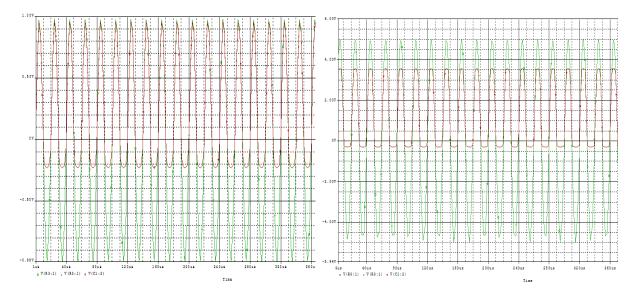

Simulation is performed and it can be seen that the diodes completely remove the negative half of input as the other diode is connected to ground and only the positive half of the sinusoidal signal is passed. The output of this circuit is fed as input to the ADC. Generally, some ADCs have Common Mode voltage which helps to raise the input to a specific DC level.

Figure 2.10: Input 1V

Figure 2.11: Input 5V

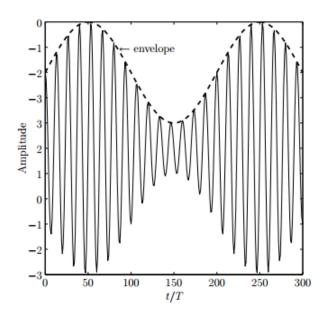

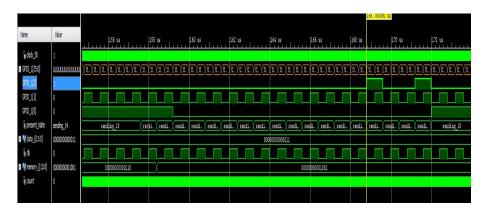

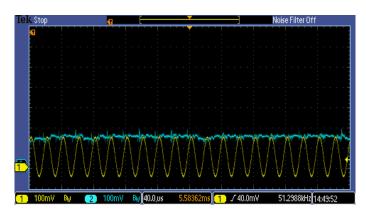

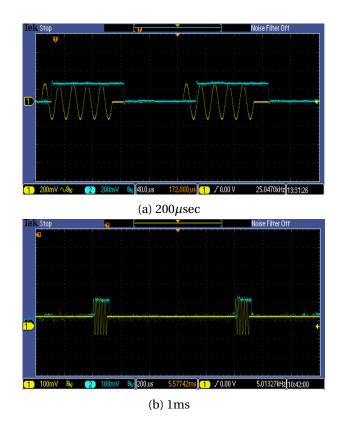

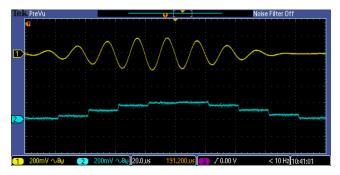

#### 2.2.7 Envelope Detection

The received echo will be a pulse of Amplitude Modulated signals i.e. every cycle can have different amplitude. It is the maximum amplitude of each cycle of echo that contains information about the target and we are interested in the envelope which covers all these maximum amplitude points. The earlier methods used a diode and a capacitor[21, Pg. 29-32] in the analog electronics, where the principal was to charge the capacitor through the diode and then this voltage stored at the capacitor was used for converting into digital values, but there was certain amount of inaccuracy and distortion involved. Moreover, these methods produced bad results at higher frequencies like 200kHz. So, now the trend is to do it digitally.

This can be achieved by first passing the analog signal through ADC and then using a Microcontroller or FPGA to extract the peak values of each pulse cycle. This method is more efficient as micro-controllers and FPGAs are more accurate and much faster.

Figure 2.12: Envelope Detection of a pulse[37, Pg. 6]

FPGAs are chosen to provide signal processing support in this project. This method has been earlier demonstrated for Xilinx[3] and Altera[15] FPGAs. So, an Altera FPGA available at the Institute can be used for the purpose of envelope detection. The echo-sounder frequencies will be in the range of 50-200kHz. So, a sampling frequency of 10 times the maximum frequency will be sufficient for obtaining the input signal digitally. This sampling frequency is provided to the ADC for conversion. ADC with 14-bits resolution or more is desired to get the top values of the every pulse cycle.

# **Chapter 3**

## **Design and Development**

#### • 3.1 Choice of Components

3.1.1 Transmitter 3.1.1.1 MOSFET Driver 3.1.1.2 MOSFET Pair 3.1.1.3 High Voltage Inputs 3.1.1.4 Step-up DC-DC Controller

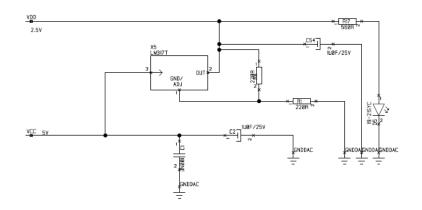

3.1.2 HV Protection Transmitter( $T_x$ )/Receiver( $R_x$ ) Switch

3.1.3 Receiver

3.1.3.1 Variable Gain Amplifier3.1.3.2 Anti-aliasing Filter3.1.3.3 Analog to Digital Converter3.1.3.4 Digital to Analog Converter

3.1.4 Choice of FPGA

#### • 3.2 Hardware Development

3.2.1 Schematics of Transmitter part 3.2.1.1 MD1213 3.2.1.2 TC6320

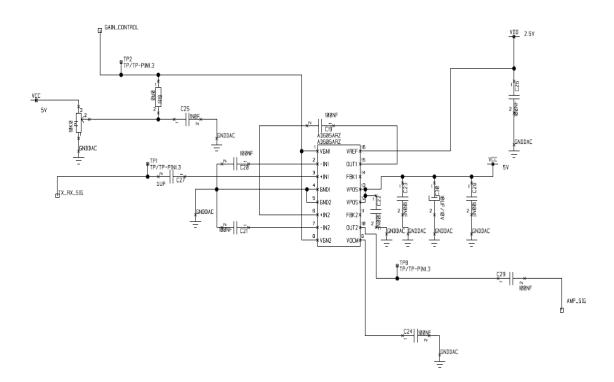

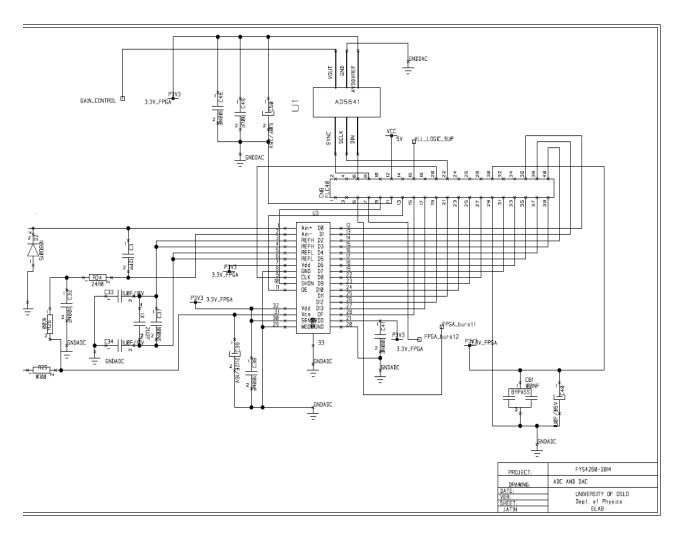

3.2.2 Schematics of Receiver part 3.2.2.1 MD0100 3.2.2.2 AD605 3.2.2.3 LTC2245 3.2.2.4 AD5641

3.2.3 High Voltage MAX1771 Board

3.2.4 Designed High Voltage MAX1771 Board

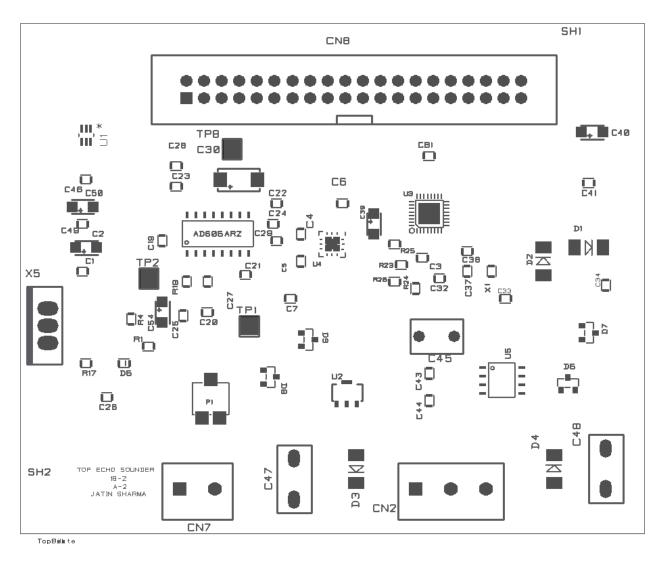

3.2.5 Designed Echo sounder Board

## • 3.3 Software Development

3.3.1 Simulation

3.3.1.1 Simulation of AD605 3.3.1.2 Simulation using ModelSim

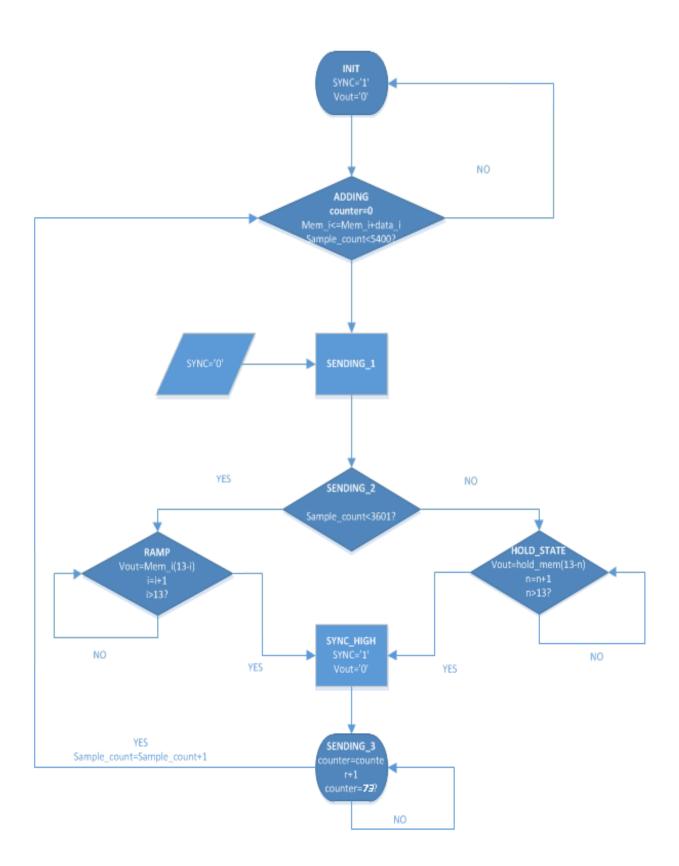

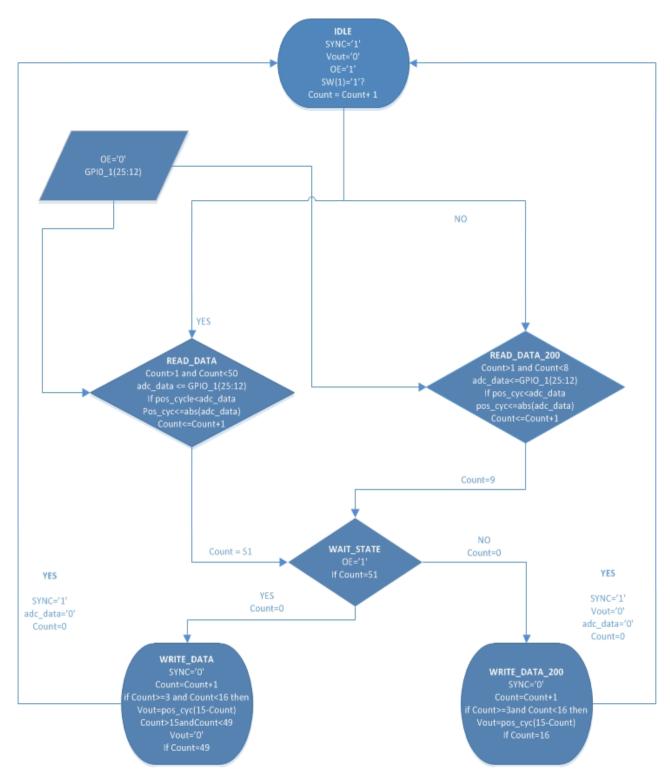

3.3.2 VHDL Code Development 3.3.2.1 Clock Divider 3.3.2.1 MD1213 3.3.2.3 DAC AD5641 3.3.2.4 ADC LTC2245

## 3.1 Choice of components

## 3.1.1 Transmitter

Pulses can be transmitted using Bipolar Junction Transistors(BJTs) and Metal Oxide Semiconductor Field-Effect Transistors(MOSFETs). Both are very reliable in amplification and switching applications.

MOSFETs are voltage controlled devices and are more efficient in handling power and suitable for high-power applications. MOSFETs when properly biased have a very low drain-source ON resistance  $R_{DS}(on)$ , which means that they behave quite much like an actual switch when turned on. Also because of the advancement in technology, MOSFETs are the most common transistors used in the design circuitry.

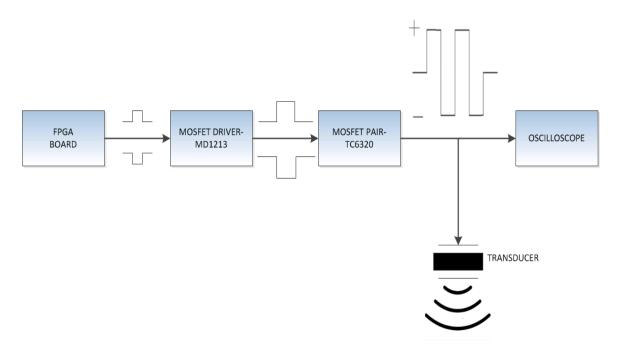

## 3.1.1.1 MOSFET Driver

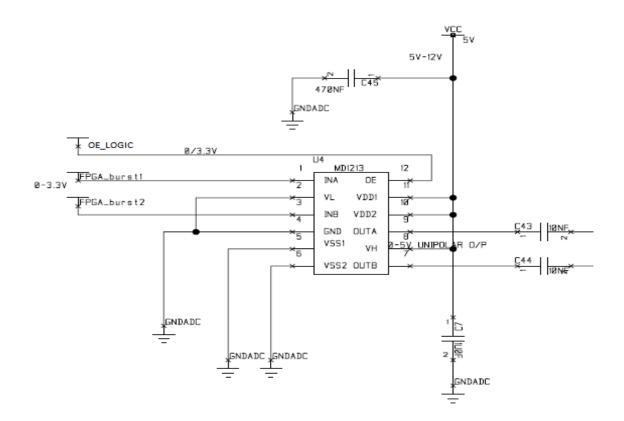

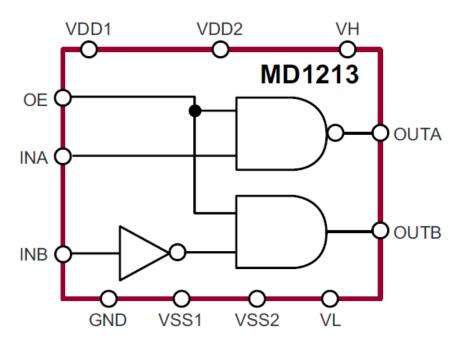

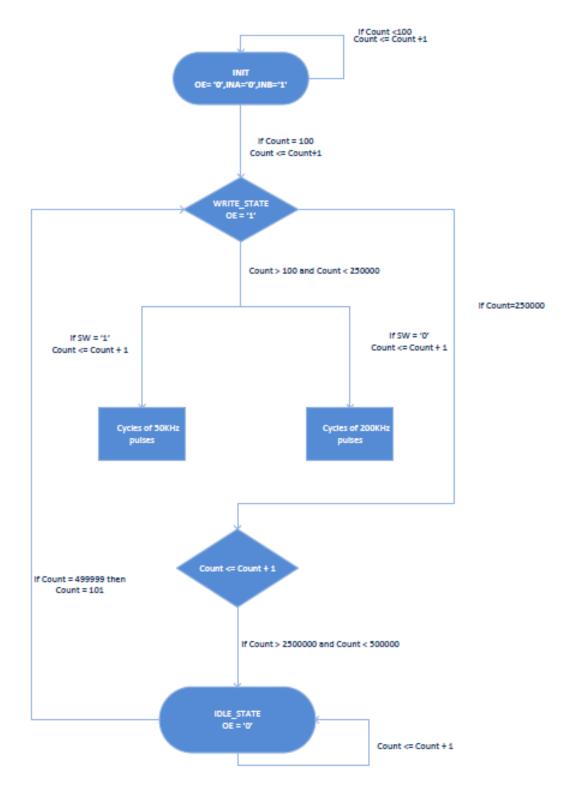

For transmission of pulses, a push-pull MOSFET pair is required and to drive these transistor pairs, a dual MOSFET driver is used. MD1213 solves this purpose[11]. This MOSFET driver operates at supply voltages between 4.5 and 13V and therefore, compatible with the FPGA board used in this project. The input stage can operate from 1.8 to 5.0V logic interface and the voltage level provided with the logic signals from the FPGA board is 3.3V. The output stage of the MD1213 has separate power connections enabling the output signal L and H levels to be chosen independently form the supply voltages. The 3 inputs OE, INA and INB will provide the Logic inputs. The outputs need to be connected to the external PMOS and NMOS Transistor pair through a series AC Coupling capacitors of 10nF each.

The OE pin serves a dual purpose. First, its logic H level is used to compute the threshold voltage level for the channel input level translators. Second, when OE is low, the outputs are disabled, with OUTA being high and OUTB low. This assists in properly pre-charging the AC coupling capacitors that will be used in series in the gate driver circuit of the N- and P-channel MOSFETs.

This MOSFET Driver is widely used in driving piezoelectric transducers both in hydro acoustics and in medical ultrasound systems. MD1213 comes in a small 12-pin QFN package[11, Page 7]. A couple of MD1213 ICs were purchased from the available vendors. Also, the symbols and foot-prints of MD1213 were designed and added into CADSTAR Library(and in DVD also) as they were required for Schematics and PCB development.

The other similar options were MD1210[44] and MD1211[46]. But MD1213 was the preferred choice because Bipolar output voltage of  $\pm 5V$  can also be achieved with this chip if desired.

#### 3.1.1.2 MOSFET Pair

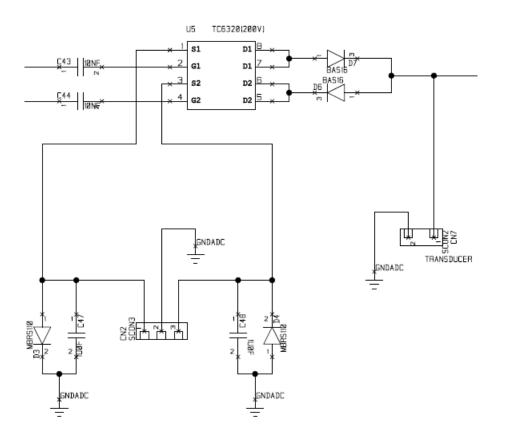

The outputs from the MD1213 MOSFET Driver need to be fed in to a transistor pair so as to produce High Voltage pulses for transmission. An essential feature of these transistors should be that they should have a low output impedance so that the signals can be successfully injected into the transducer circuits without adversely affecting them. There are various MOSFET arrays components available and can be chosen depending upon the various parameters like  $R_{DS}(on)$ , cost and the breakdown voltage depending upon the application. MOSFET array which fits the requirements was TC6320 and therefore, it was used.

TC6320 is a high voltage, low threshold N and P channel Enhancement-Mode MOSFET Pair. It can operate at high speeds and high voltages. TC6320 has integrated Gate to Source resistor and Gate to Source Zener Diode on both channels. During power up and power down conditions, it is possible for transient voltages greater that 20V to appear across the gate-to-source on the output transistors. These built-in 15-18V Zener diodes help to protect against such transient voltages. These diodes will not have any Zener current during normal operation and also serve as the gate DC voltage restoring functions[33, Pg. 2].

These ICs are best suitable for amplifying and switching applications such as in driving an echo sounder transducer. TC6320 is highly robust, efficient and free from thermal runaway unlike other MOS Structures.

TC6320 comes in 8-lead SOIC and DFN packages[12, Page 2].SOIC package was chosen for this project. The footprints and symbols were already available in CADSTAR Library and were edited to be used for this component.

The outputs of this MOSFET pair needs to be connected to two external BAS16 diodes on P and N channel and then single output is taken thereafter to drive the piezoelectric transducer, FURUNO 520-5PSD.

The alternate option available was TC2320[45] but TC6320 was chosen because of its low Drain-Source Resistance ( $R_{DS}$ ).

#### Alternate option

The other option available was to have a circuit which could solely provide the above processes within a single chip. After searching, it was found out that a high voltage, high speed pulse generator called HV7361 can be used as the complete Transmitter Unit[14]. HV7361 consists of a controller logic interface circuit, level translators, AC coupled MOSFET gate drivers and P-channel and N-channel MOSFETs, all built-in.

In addition, a Transmit/Receive Protection Switch was also included in this chip. But this option was discarded because of its 22-Lead LFGA package and the combined costs of all three described ICs were less than half of this single HV7361 chip. Moreover, the advantage of using individual ICs

is that there is always an option available to change the complimentary MOSFET pair with another one depending upon the amplitude of the pulse outputs desired.

However, symbol and footprint for HV7361 have been made and added in CADSTAR library and DVD.

## 3.1.1.3 High Voltage Inputs

The source voltage pins(S1 and S2) of TC6320 MOSFET pair need to be connected to high negative and positive voltages, like  $\pm 50V$ . Such high voltages need to be produced without adversely affecting the operation of the rest of the circuit as these may lead to noise and other effects. Therefore, it is desired to make such high voltages away from the echo sounder board. So, the pins 1 and 3 of TC6320 which represent Source terminals of N-channel and P-channel respectively can be used to connect to the high voltage supplies.

To fulfill this purpose, a separate PCB board was designed which can give the necessary voltages to the echo sounder board.

## 3.1.1.4 Step - Up DC-DC Controller

For boosting the voltage from 12V to a higher level(say,100V), a step-up converter is required.

MAX1771 is a step-up switching controller and can be used in this project for stepping-up DC-DC Voltage from flexible input range between 2V and 16.5V to the desired value. A unique current-limited pulse-frequency-modulation(PFM) control scheme gives this device the benefits of pulse-width-modulation(PWM) converters. MAX1771 is highly efficient IC which can provide load current over the range 30mA to 2A and uses miniature external components. This IC drives an external N-channel MOSFET Switch allowing it to power loads up to 24W. [20, Page1].

MAX1771 comes in 8-pin DIP and SO packages. As this IC was exclusively used in this project and not available in E-Lab, it was purchased in SO packages and added in the library.

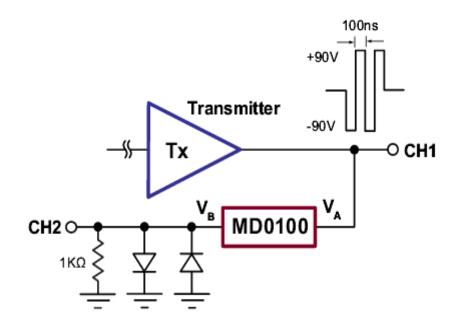

## **3.1.2** HV Protection Transmitter $(T_x)$ /Receiver $(R_x)$ Switch

The transmitter and receiver part are separated from each other during transmission using a switch.

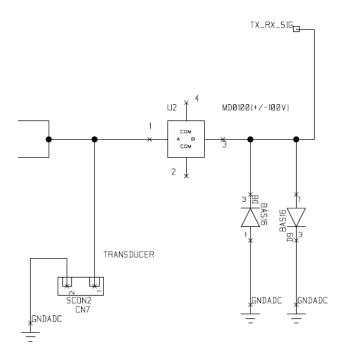

The high voltage protection T/R Switch, MD0100 is a very good solution[9]. This switch is bidirectional and designed for its operation in ultrasonic applications. It can handle up to  $\pm 100V$ input voltages. It is primarily designed to protect a low noise receiver circuit from high voltage transmit pulses. It has a very wide bandwidth of 100MHz. It is a normally closed(NC) Switch with a typical switching resistance of 15  $\Omega$  that allows small signals to pass through it. Once the voltage drop across the two terminals exceeds a nominal value of  $\pm 2.0V$ , the device will start to turn off. In the off state, the MD0100 can withstand up to  $\pm 100V$  across its terminals while a small amount of current of  $200\mu$ A is allowed to flow through.

It is almost a complete protection circuit which comes in user friendly SOT-89 package and needs only a pair of back-to-back diodes from the receiver side connected to switch and ground. The purpose of diodes is to allow a current path. Otherwise, if there are no diodes present, then there will be no current path and the voltage drop across terminal A and B will be less than  $\pm 2V$  and the switch will remain in the closed position. Also, the diodes help in clamping the voltage spikes to  $\pm 0.7V$  during transmit cycle[9].

Because this switch was not available in E-Lab, it was purchased and necessary symbol and footprints were added in Cadstar Library.

Switch MD0101[47] is also a good option as it has integrated clamp diodes and therefore no need of external diodes but it is useful when there are more number of channels in the system. Similarly, if voltages greater than  $\pm 100V$  are used for transmission, then the switch MD0105[48] can be used. This switch can be used for protection against voltages up to  $\pm 130V$ .

## 3.1.3 Receiver

## Signal Conditioning Components

Signal conditioning is a term which is frequently used in Electronics and refers to the manipulation of the analog signals such that they meet the requirements of the later stages, especially ADCs. In signal conditioning stage, processes such as amplification, filtering, range matching, isolation can be done depending upon the input signal and the requirements of the later processing part. The various components used for signal conditioning in this project are:-

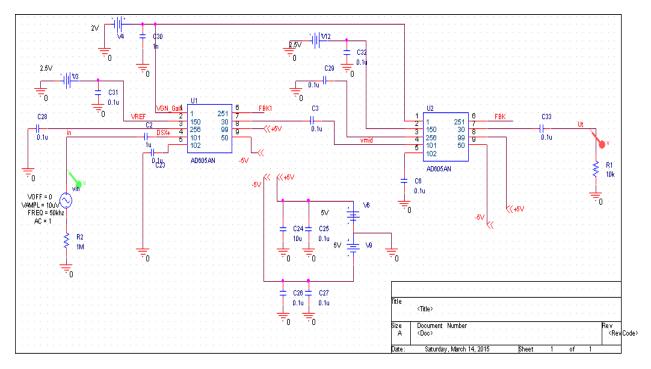

## 3.1.3.1 Variable Gain Amplifier

Variable gain amplifiers are easily available but there are some requirements which help in filtering out the unnecessary amplifiers. It is desired that amplifiers can provide a gain range from 0 to around 90 decibels(dB). The bandwidth should also be large for different gains. Among available choices amplifier like AD8338[42] from Analog Devices was a good choice. It can provide gain up to 80dB with 18MHz Bandwidth. It was not used because it offered a slightly higher Input noise.

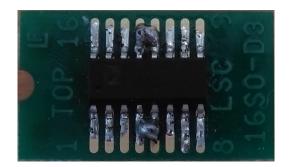

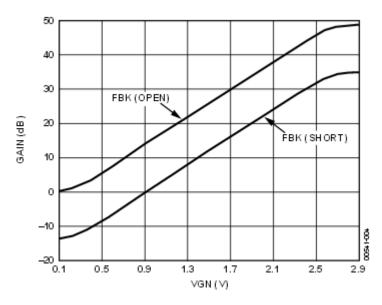

Amplifier AD605 is used in this project. AD605 is a low noise, differential-input, dual-channel, linear-in-dB Variable Gain Amplifier. It fulfills the desired characteristics of gain, noise, supply voltage etc. It comprises of two variable gain amplifiers which can be connected in series to get higher gain ranges, up to 96dB and it uses a common gain voltage( $V_{GN}$ ) for both the amplifiers to control the variable gain.

The gain scaling for this amplifier can be set between 20dB/V and 40dB/V with the help of VREF pin for better gain scaling. Providing VREF 2.5V will set the scale factor to be 20 dB/V while 1.25V will set it to 40 dB/V. Accordingly, the gain scales linearly in dB with control voltages( $V_{GN}$ ) of 0.1V to 2.9V for the 20 dB/V scale and 0.2V to 1.2V for the 40dB/V scale. The amplifier can be used with differential/single-ended inputs and the output is single-ended. The negative inputs of both the channels are connected to the ground through  $0.1\mu$ F ceramic capacitors if it is used as a single-ended amplifier.

AD605 comes in 16-lead PDIP and SOIC packages. SOIC package was used as rest of the components are also surface mounted(SM). This component was also new in Cadstar Library and its symbol and footprints were added in the library using the Ultra Librarian(UL) Software. The .bxl files were used as inputs in this software for this component.

For simulation purposes, AD605 was added as a new component(AD605AN.olb) in the library of OrCAD tool and this file is also attached in the DVD. Each unit corresponds to a single channel.

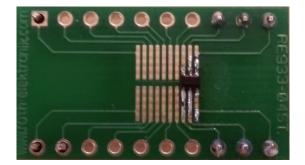

Figure 3.1: AD605 with SOIC to DIP adapter

#### **Voltage Regulator**

VREF voltage ranging between 2.5V-1.25V can be provided with the help of LM317 Voltage regulator. LM317 is a monolithic IC which is used as a positive adjustable voltage regulator. It can output a fixed output voltage from 1.2 to 37 Volts DC. The nominal output voltage is selected by means of a resistive divider, making the device exceptionally easy to use and eliminating the stocking of many fixed regulators[19]. A resistor and a potentiometer or simply two resistors are used for obtaining the required output voltage and follow the relation:

$$V_{out} = 1.25 * \left(\frac{R1 + R2}{R1}\right) + I_{ADJ}R2 \quad [52, Pg. 4]$$

(3.1)

LM317 comes in various packages but TO-220 package is used.

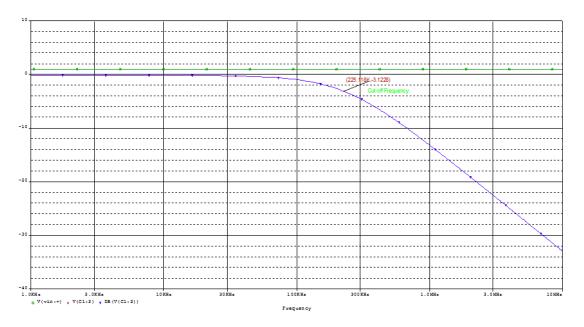

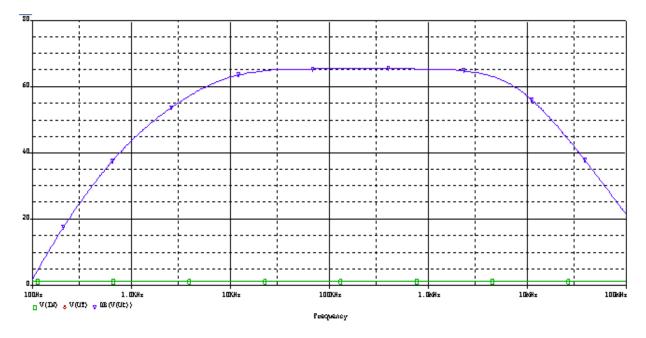

#### 3.1.3.2 Anti-aliasing Filter

Before giving the input into ADC, the signal is passed through an Anti-aliasing filter. An Antialiasing filter is a low pass filter of a particular order that has a cut-off frequency which removes the unwanted signals from the ADC input or at least attenuate them to a point that they do not degrade the circuit performance.

An ideal anti-aliasing filter passes all the appropriate input frequencies (below cut-off frequency,  $f_c$ ) and cuts of all the undesired frequencies (above  $f_c$ ). However, such a filter is practically not possible. The choice of the filter depends on the frequencies of interest and allowed attenuation in the passband. There are various types of filters like Chebyshev, Butter worth, Elliptic and Bessel filters. Each one has its own advantage such as Butter-worth offers flattest passband region among all the filters.

The incoming signal to the ADC is passed through a first-order low pass filter comprising of a resistor(R) and a capacitor(C). A first-order anti-alias filter is chosen for the simplicity of the design and because of the oversampling of the input signal i.e. using 5MHz sampling rate. Data-sheet[13, Pg 12] of chosen ADC recommends values of 25 Ohm( $\Omega$ ) and 12pF for resistor and capacitor re-

spectively but this gives cut-off frequency in hundreds of MHz.  $15\Omega$  resistor and 47nF capacitor were used to form the anti-aliasing filter.

$$\omega = 1/RC \tag{3.2}$$

where  $\omega = 2\pi f$ ;

This filter simply provides a cut-off frequency around 225.7kHz and attenuates the undesired signals. Simulation uses the same setup shown in Fig.2.9 and the circuit files are present in Attachment V.

A simple plot of the filter's operation is shown below:-

Figure 3.2: Anti-aliasing filter

A more advanced solution would be using an Active RC filter such as LTC1563-2/LTC 1563-3. These are 4th order Low-pass Filters and can easily be used for Anti-aliasing applications. These filters require only a single resistor value to set the cut-off frequency[30, Pg 1]. The cut-off frequency can be set anywhere between 256Hz and 256kHz using the following relation:-

$$R = 10k * (256kHz/f_c) \tag{3.3}$$

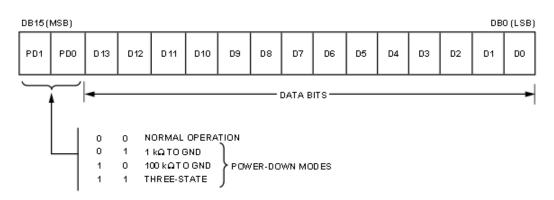

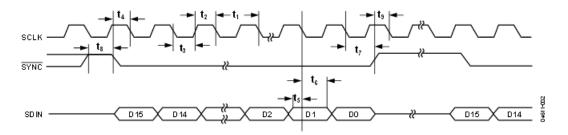

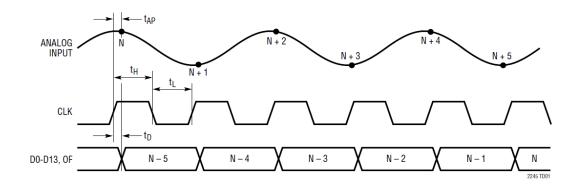

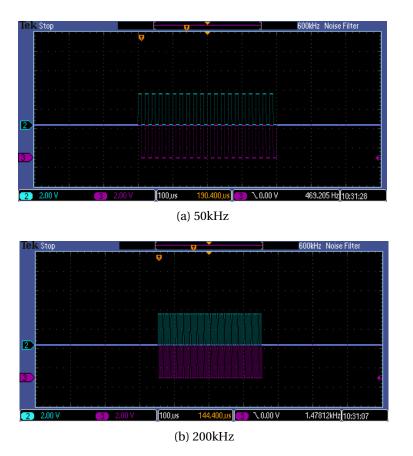

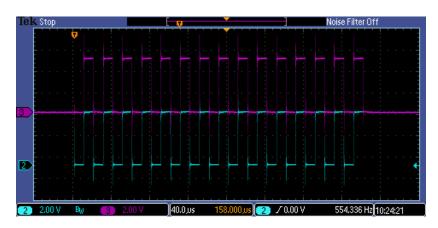

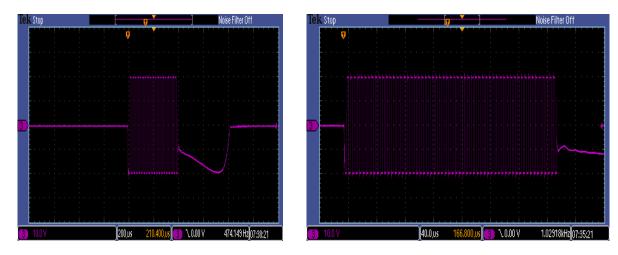

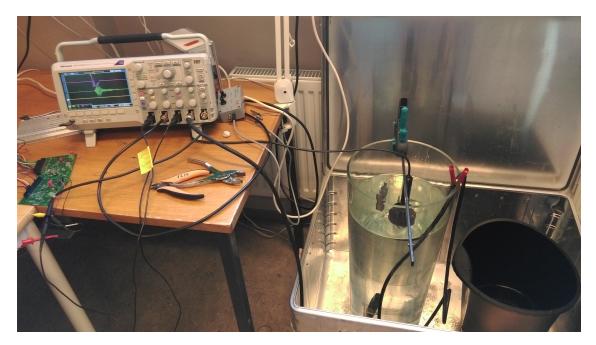

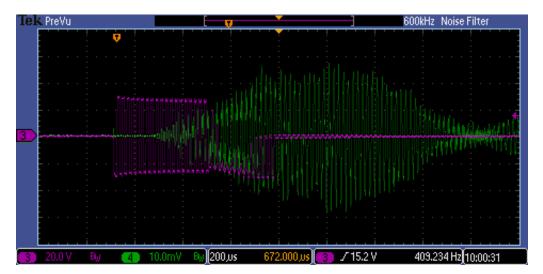

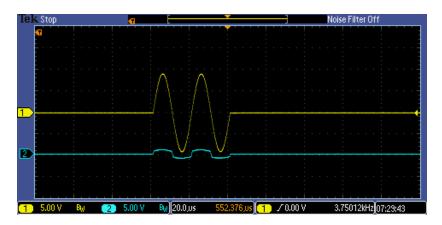

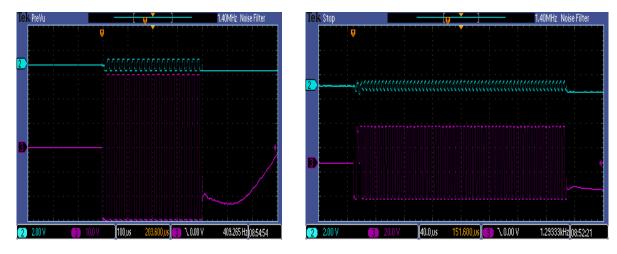

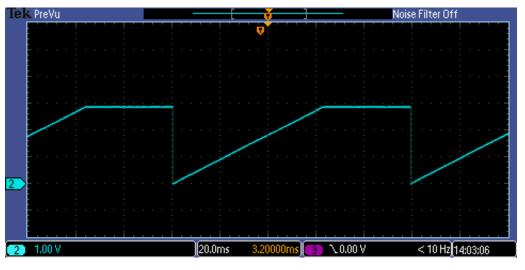

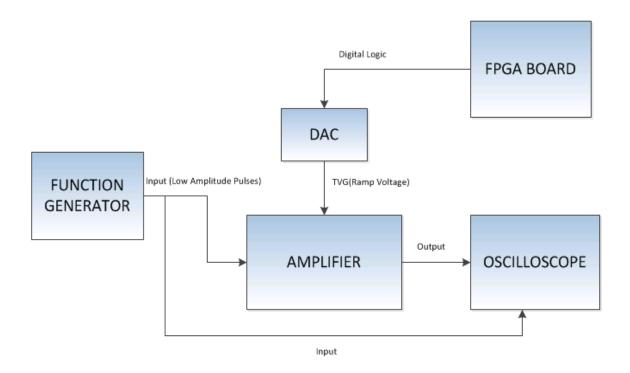

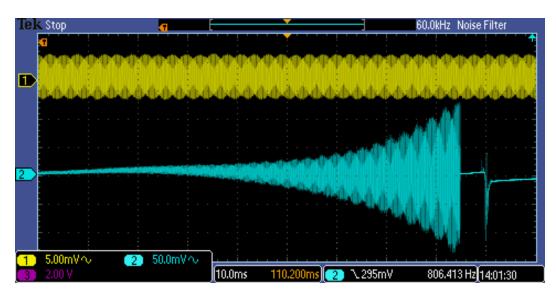

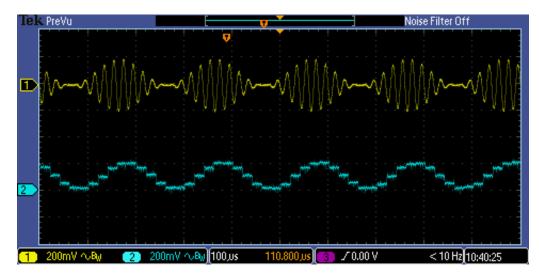

;  $f_c$  = desired Cut-off frequency