## IR-UWB RFID Circuits and Systems

Kin Keung Lee

Department of Informatics University of Oslo

September 9, 2014

### © Kin Keung Lee, 2014

Series of dissertations submitted to the Faculty of Mathematics and Natural Sciences, University of Oslo No. 1580

ISSN 1501-7710

All rights reserved. No part of this publication may be reproduced or transmitted, in any form or by any means, without permission.

Cover: Hanne Baadsgaard Utigard. Printed in Norway: AIT Oslo AS.

Produced in co-operation with Akademika Publishing.

The thesis is produced by Akademika Publishing merely in connection with the thesis defence. Kindly direct all inquiries regarding the thesis to the copyright holder or the unit which grants the doctorate.

To Iris

## **Abstract**

Radio-frequency identification (RFID) technology has been applied extensively in logistic and supply chain applications. Long-range passive RFID systems offer higher reliability and flexibility compared to conventional bar-code systems. However, limitations such as sensitivity to multipath fading and diffraction grating exist due to the narrowband technologies used. Also, industries show interest in embedding precise localization ability in such systems which is difficult to achieve using narrowband communications.

After the Federal Communications Commission released an ultra-wide bandwidth (3.1–10.6 GHz) for unlicensed use in 2002, impulse-radio (IR) ultra-wideband (UWB) communications have drawn lots of attention from both academia and industry. The large bandwidth (in other words short pulse duration) not only improves the communication quality compared to the narrowband counterparts, but also provides an excellent localization ability. This makes IR-UWB technology a potential candidate for next generation long-range passive RFID systems.

The main goal of this work is to apply UWB technology to advance the current long-range passive RFID system performance. A novel passive IR-UWB RFID system has been proposed. The potential advantages are long tag reading range with localization ability, insensitivity to surrounding environments and high security. A wireless-powered IR-UWB transmitter for the proposed system has been successfully demonstrated in a TSMC 90 nm CMOS process. Together with the coherent IR-UWB receiver implemented by the author's research group, implementations of the proposed RFID system become possible.

Moreover, the power consumption and other specifications of individual components have to be considered also in order to maximize the system performance. Research has been conducted on several functional blocks including IR-UWB pulse generator, clock generator and reference circuit. Novel topologies and solutions have been proposed and verified. Experimental results have proven competitive performance compared to other published state-of-the-art counterparts.

"A scientific man ought to have no wishes, no affections, a mere heart of stone." - Charles Robert Darwin

## Acknowledgments

There are many people who have made my Ph.D. journey enjoyable and enriching. First, I would like to express my deepest gratitude to my thesis advisor, Prof. Tor Sverre Lande, for his excellent supervision and professional guidance. His scientific expertise, visions and enthusiasm are impressive. The journey would not be completed without his encouragement.

I am grateful to my thesis co-advisor, Prof. Philipp Dominik Häfliger, for invaluable help and countless constructive feedbacks.

I gratefully appreciate the friendship, support and encouragement from both past and present members of the Nanoelectronics group: Prof. Oddvar Søråsen, Prof. Dag T. Wisland, Prof. Snorre Aunet, Prof. Svein-Erik Hamran, Prof. Yngvar Berg, Ali Zaher, Amir Hasanbegovic, Dr. Farshad Moradi, Hans Kristian Otnes Berge, Håkon Andre Hjortland, Dr. Jan Erik Ramstad, Dr. Juan Antonio Leñero Bardallo, Dr. Jørgen Andreas Michaelsen, Kristian Gjertsen Kjelgard, Leif Elias Bakken, Malihe Zarre Dooghabadi, Olav Stanly Kyrvestad, Dr. Shanthi Sudalaiyandi, Srinivasa Reddy Kuppireddi, Thanh Trung Nguyen, Dr. Tuan Anh Vu, Dr. Tuan Vu Cao, Dr. Øivind Naess, Øystein Bjørndal. Special thanks to Olav and Kristian for their input on chip fabrication and measurements, I would not be able to demonstrate my research ideas without them. Also, thanks to all my office-mates, Ali, Amir, Hans, Jørgen and Srinivasa, they are great people to bounce ideas off of.

My heartfelt thanks also go to my ex-colleagues in Novelda AS, Aage Kalsæg, Alf Olsen, Claus Limbodal, Elizabeth Wisland, Khanh Quoc Dang, Kjetil Meisal, Kristian Granhaug, Marius Mossum, Mats Risopatron Knutsen, Nikolaj Andersen, Olav Liseth, Dr. Stig Støa and Åsmund Rinde, for their friendship and encouragement.

I am grateful to Dr. Olive Murphy of Analog Devices, Dr. Per Torstein Røine of Texas Instruments, and Prof. Kyrre Harald Glette for being the evaluation committee members.

A special thank to Prof. Henrik Sjöland of Lund University for encouraging me to pursue my Ph.D. study.

The chip fabrication and conference traveling were funded in part by the Norwegian Research Council through the Norwegian Ph.D. Network on Nanotechnology for Microsystems under Contract 190086/S10.

Finally, I thank my family and my girlfriend Iris for their unconditional love, support and encouragement throughout these years. I would not have completed this dissertation without them.

## Contents

| Al | bstrac  | t       |                                                      |    |       |  | •   | V |

|----|---------|---------|------------------------------------------------------|----|-------|--|-----|---|

| A  | cknov   | vledgme | ents                                                 |    |       |  | vi  | i |

| C  | onten   | ts      |                                                      |    |       |  | i   | X |

| Li | st of . | Acrony  | rms                                                  |    |       |  | X   | i |

| Li | st of ] | Figures |                                                      |    |       |  | xii | i |

| 1  | Intr    | oductio | on                                                   |    |       |  |     | 1 |

|    | 1.1     | Motiva  | rations                                              |    |       |  |     | 1 |

|    | 1.2     | A Brie  | ef Overview of Long-Range RFID Systems               |    |       |  |     | 3 |

|    |         | 1.2.1   | Passive, Active and Semi-Passive RFID Systems        |    |       |  |     | 3 |

|    |         | 1.2.2   | System-Level Specifications                          |    |       |  |     | 4 |

|    |         |         | 1.2.2.1 Reading Range                                |    |       |  |     | 4 |

|    |         |         | 1.2.2.2 Operating Frequency                          |    |       |  |     | 5 |

|    |         | 1.2.3   | Internet-of-Things and Other Applications            |    |       |  | (   | 6 |

|    | 1.3     | An Int  | troduction to UWB Technology                         |    |       |  | (   | 6 |

|    |         | 1.3.1   | A Brief History of UWB Technology                    |    |       |  | (   | 6 |

|    |         | 1.3.2   | FCC Regulations on UWB Communications                |    |       |  |     | 7 |

|    |         |         | 1.3.2.1 Definitions of UWB Signals                   |    |       |  |     | 7 |

|    |         |         | 1.3.2.2 Emission Energy and Spectrum Mask Regulation | 18 |       |  | ;   | 8 |

|    |         | 1.3.3   | Advantages of UWB Communications                     |    | <br>• |  | ;   | 8 |

|    | 1.4     | Disser  | tation Outline                                       |    |       |  | 10  | 0 |

| 2  | Wor    | k Desci  | riptions                       | 13   |

|----|--------|----------|--------------------------------|------|

|    | 2.1    | IR-UW    | WB RFID Systems                | . 13 |

|    |        | 2.1.1    | Background                     | . 13 |

|    |        | 2.1.2    | Related Work and Contributions | . 14 |

|    | 2.2    | IR-UW    | WB PGs                         | . 15 |

|    |        | 2.2.1    | Background                     | . 15 |

|    |        | 2.2.2    | Related Work and Contributions | . 16 |

|    | 2.3    | Clock    | Generators                     | . 17 |

|    |        | 2.3.1    | Background                     | . 17 |

|    |        | 2.3.2    | Related Work and Contributions | . 18 |

|    | 2.4    | Refere   | ence Circuits                  | . 18 |

|    |        | 2.4.1    | Background                     | . 18 |

|    |        | 2.4.2    | Related Work and Contributions | . 19 |

| 3  | Sum    | ımary a  | and Future Work                | 21   |

|    | 3.1    | Summ     | nary                           | . 21 |

|    | 3.2    | Recom    | nmendations for Future Work    | . 22 |

| Bi | bliogi | raphy    |                                | 23   |

| A  | Tech   | inical P | Paper Collection               | 33   |

|    | A.1    | Paper-l  | I                              | . 33 |

|    | A.2    | Paper-   | II                             | . 39 |

|    | A.3    | Paper-   | III                            | 45   |

|    | A.4    | Paper-   | IV                             | . 51 |

|    | A.5    | Paper-   | V                              | . 57 |

|    | A.6    | Paper-   | VI                             | . 67 |

|    | A.7    | Paper-V  | VII                            | 73   |

## List of Acronyms

AoA Angle-of-Arrival

BGR BandGap Reference circuits

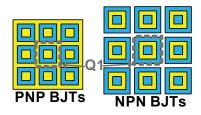

BJT Bipolar Junction Transistor

BPSK Bi-Phase Shift Key

BW BandWidth

CMOS Complementary Metal-Oxide-Semiconductor

CDMA Code-Division Multiple Access

DC Direct-Currernt DL Delay-Line

EIRP Equivalent Isotropically Radiated Power

ETSI European Telecommunications Standards Institute

ERP Effective Radiated Power FB Fractional Bandwidth

FCC Federal Communication Commission

FoM Figure-of-Merit

HFWG High-Frequency Waveform Generator

ILD Injection-Locking frequency Divider

ISM Industrial Scientific and Medical

IR Impulse Radio OOK On-Off-Key

PD Propagation Delay PG Pulse Generator ppm parts per million

PRF Pulse Repetition Frequency

QF Quality Factor RF Radio-Frequency

RFID Radio-Frequency IDentification

RTL Real Time Localization

RX Receiver

MEMS Micro-Electro-Mechanical System

MPC Multi-Pulse Combination

NB NarrowBand

SNR Signal-to-Noise Ratio SRD Short-Range Device TC Temperature Coefficient

TSMC Taiwan Semiconductor Manufacturing Company

TX Transmitter

UHF Ultra-High-Frequency

USD United States Dollar

UWB Ultra-WideBand

XO CRYStal Oscillator

# List of Figures

| 1.1 | RFID market projection from 2010 to 2014 (modified from [3])                                                                    | 1  |

|-----|---------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | An exampled long-range passive RFID system                                                                                      | 2  |

| 1.3 | Possible RFID operating frequency ranges together with the frequency bands occupied by other radio systems (modified from [15]) | 5  |

| 1.4 | A illustration of several FCC regulation parameters                                                                             | 8  |

| 1.5 | FCC part 15 indoor and outdoor masks                                                                                            | 9  |

| 3.1 | An idea of piecewise-linear curvature-compensation                                                                              | 22 |

"Two things are infinite: the universe and human stupidity; and I'm not sure about the universe." — Albert Einstein

## Chapter 1

## Introduction

### 1.1 Motivations

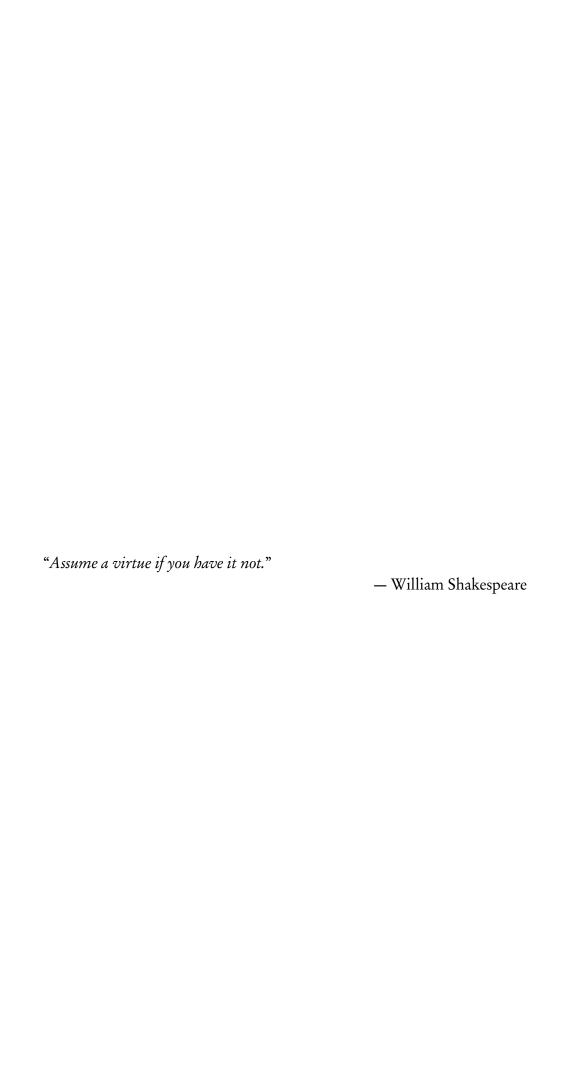

Radio-frequency identification (RFID) has been recognized as one of the most important radio innovations in the 21st century and permeates our daily life everywhere [1]. The research of RFID technology has started in 1948, but did not draw too much attention. Recently, the RFID market has experienced a tremendous growth due to improved system performance contributed by the rapid developments in integrated circuit and radio technologies [2]. A RFID market projection from 2012 to 2014 is shown in Figure 1.1. In total, around 5.9 billion tags (23% growth from 2012) were sold and the whole RFID market was worth 7.9 billion United States Dollar (USD, 13% growth from 2012) in 2013. It is expected that the

Figure 1.1: RFID market projection from 2010 to 2014 (modified from [3]).

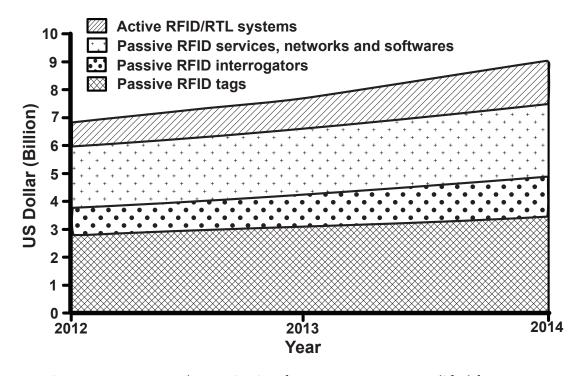

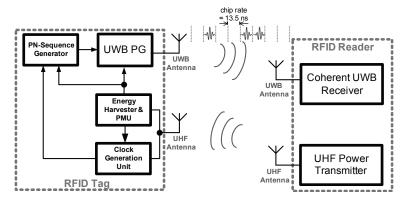

Figure 1.2: An exampled long-range passive RFID system.

RFID market will rise to 30.2 billion USD in 2024 [3], which is a huge potential market and receives significant interest from the industry.

Logistic and supply chain are the major areas of implementation for RFID technology. For example long-range passive (wireless-powered) RFID systems (with a reading range of around ten meters) have been adopted on item-tracking in large spaces like warehouses because they offer higher reliability and flexibility compared to the conventional bar-code systems with low cost (a tag can cost less than 0.1 USD nowadays). Such systems usually contain a host computer, readers and tags, which is briefly illustrated in Figure 1.2 [4]. The readers transfer energy and read/write data from/to the tags. The host computer controls and collects data from the readers depending on the targeted applications.

Although long-range passive RFID systems have been widely used in recent years, limitations are still significant because they are based on narrowband (NB) communication technologies. One of the main problems is the sensitivity to the surrounding environment since NB radios are prone to multi-path fading, diffraction grating and jamming [5]. Also, if the tags use the same frequency for energy-harvesting and communication, they may interfere with other tags and/or readers when they are too close to each others [6]. Another consideration is security (eavesdropping), data en-/decryption may not be possible due to the limited energy available on the tag side. In addition, there is interest from the industry on embedding real time localization (RTL) functions to such systems [7], however it is difficult to perform precise localization using the NB technologies [8].

After the Federal Communication Commission (FCC) of the United States released a large bandwidth (BW) for unlicensed uses in 2002 [9], impulse-radio (IR) ultra-wideband (UWB) communication has become an active research topic and provides many advantages, including high data rate and precise localization ability, over the NB counterparts. As a result, there are attempts (for example [7,10–12]) on applying the UWB technology to passive RFID applications. However, most of the purposed solutions have limited reading range (less than one meter) because of the limited energy available on the tag side and weak emission power limited by FCC.

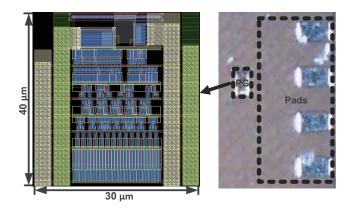

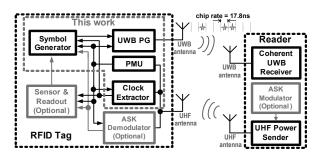

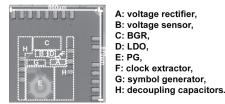

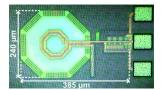

The main goal of this work is to apply the UWB technology to advance the current long-range passive RFID technology. A novel passive IR-UWB RFID system has been proposed. The potential advantages are long tag reading range (several meters) with localization ability, insensitivity to surrounding environments and high security. A wireless-powered IR-UWB transmitter (TX) for the proposed system has been successfully demonstrated in a Taiwan Semiconductor Manufacturing Company (TSMC) 90 nm complementary metal-oxide-semiconductor (CMOS) process [13]. Together with the coherent IR-UWB receiver (RX) proposed in [14], implementations of the proposed RFID system becomes possible. Moreover, the power consumption and other specifications of individual components have to be considered also in order to maximize the system performance. Novel circuit solutions are proposed and analyzed. Experimental results have showed competitive performance compared to other published state-of-the-art counterparts.

### 1.2 A Brief Overview of Long-Range RFID Systems

### 1.2.1 Passive, Active and Semi-Passive RFID Systems

The RFID systems nowadays can be divided into three main categories by the powering schemes for the tags [15, 16], brief descriptions and their operations are listed as follows:

- 1. Passive RFID systems are the most commonly used type nowadays because no battery is required on the tag side which makes them low-cost and small-size. The signals (may include clock signal) and energy are sent from the reader with a distance up to around ten meters, for example [17] and [18]. Backscatter or load modulation is usually used for communications and channel separation is usually done by time-division multiple access [15].

- 2. Active RFID systems are essentially full radio transceiver systems and the tags are battery-powered. The battery gives the possibility of embedding more functionalities and building up more reliable and longer-range (can reach 100 meters [19]) communications. The trade-offs are increased product cost and size for the tags. Another consideration is maintenance [2,20], battery-replacement may not be easy for some applications like in-wall and harsh-environment monitoring. This increases the maintenance cost and degrades the flexibility of such tags.

3. Semi-passive RFID systems are a balance between systems 1 and 2. The tags contain a battery for supplying energy to the digital control circuits only. This eliminates the need for energy-harvesting, thus the reading distance is enhanced compared to the passive solutions. Meanwhile, backscatter modulation is utilized for communication, this eliminates the power-demanding radio-frequency (RF) signal transmissions and, hence, increases the battery life compared to the active solutions.

### 1.2.2 System-Level Specifications

#### 1.2.2.1 Reading Range

One of the most important specifications of the RFID systems is the reading range between the tags and the readers. For long-range electromagnetic-coupling RFID systems<sup>1</sup>, the reading range depends on several parameters and the relationship can be briefly shown by using the well-known Friis transmission equation [21]:

$$\frac{P_R}{P_T} = G_R G_T \left(\frac{\lambda}{4\pi R}\right)^2 \tag{1.1}$$

where  $P_R$  and  $P_T$  are the power available at the receiving antenna input and the output power at the transmitting antenna respectively.  $G_R$  and  $G_T$  are the antenna gains of the receiving and transmitting antennas respectively,  $\lambda$  is the signal wavelength, and R is the distance between the antennas. Two assumptions are made here. First, the antennas are sufficiently far away from each other and operate in far-field regions. In other words, the distance between them is larger than  $\frac{2D^2}{\lambda}$ , where D is the largest dimension of either antenna. Second, only the free space path loss is considered.

It can be seen from (1.1), assuming the same RX sensitivity, the reading range can be increased by:

- 1. increasing the emission power  $P_T$ . Note that the maximum emission power depends on the signal frequency and regulations of different country.

- 2. increasing the antenna gains  $G_T$  and  $G_R$  which depend on the topology and is proportional to the antenna size.

- 3. reducing signal frequency, in order words increasing  $\lambda$ . The available frequency bands depend on regulations of different country. Also, the antenna size is proportional to  $\lambda$  assuming the same gain.

<sup>&</sup>lt;sup>1</sup>Short-range RFID systems usually utilize inductive- and capacitive-coupling for energy transfer and data transmissions.

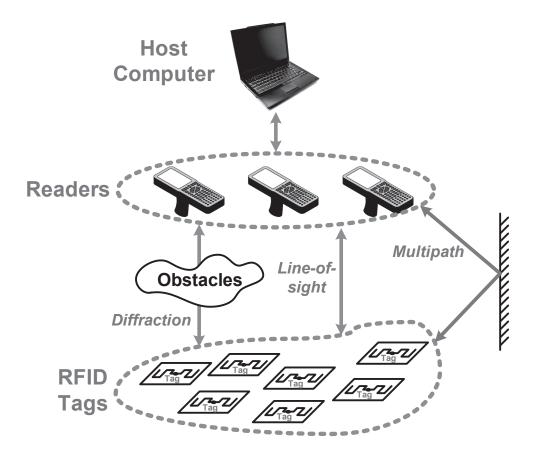

Figure 1.3: Possible RFID operating frequency ranges together with the frequency bands occupied by other radio systems (modified from [15]).

#### 1.2.2.2 Operating Frequency

One of the very first considerations on RFID system designs is the choice of the operating frequency. In addition to the worldwide available industrial scientific and medical (ISM) bands 6.78 MHz, 13.56 MHz, 27.125 MHz, 40.68 MHz, 433 MHz, 2.4 GHz, 5.8 GHz and 24.125 GHz [15], different countries or regions have released additional frequency bands which can be used for RFID applications [15]. Most of them are located at around 900 MHz, for example the ISM band (902–928 MHz) released by FCC, the short-range device (SRD, 868–870 MHz) and RFID (865–868 MHz) bands released by the European Telecommunications Standards Institute (ETSI). For simplicity, the frequency range 865–956 MHz will be referred to as "900 MHz ultra-high-frequency (UHF) band" in this dissertation. Figure 1.3 depicts the possible operating frequency bands up to 24 GHz for RFID systems together with the frequency bands occupied by other radio systems [15]. The ISM bands provide the possibility of implementing RFID systems which can be used globally, however the interference from other radio devices operating on the same ISM band can be problematic.

The maximum emission power heavily depends on the countries and frequency bands. Two remarkable frequency bands are the 900 MHz UHF and 2.4 GHz ISM bands which provides significantly higher emission power than the other bands. In the 900 MHz UHF band, the available powers are 4 W effective isotropically radiated power (EIRP) and 2 W effective radiated power (ERP)<sup>2</sup> in the United States and most European countries respectively. In the 2.4 GHz ISM band, maximum 4 W ERP/EIRP is allowed to radiate in these countries. In many other countries, regulations are either similar to those of FCC or ETSI [15, 22, 23].

From (1.1), it can be found that longer wavelengths ( $\lambda$ ) result in lower propagation losses,

<sup>&</sup>lt;sup>2</sup>For purposes of comparison, 2 W ERP is equivalent to 3.2 W EIRP [22].

hence longer reading range can be obtained with a trade-off of larger antenna size. On the other hand, the penetration<sup>3</sup> and diffraction<sup>4</sup> abilities are relatively worse for shorter wavelengths. As a balance between different parameters discussed, the 900 MHz UHF band is widely adopted for long-range passive RFID systems [23]. Some commercial examples can be found in [17] and [18]. The 2.4 GHz ISM band is also preferred because of its worldwide-availability and smaller antenna size. Nevertheless the severe interferences from other radio devices may cause more complicated communication protocols and relatively large power consumption. As a result, it is more commonly used for active RFID systems.

### 1.2.3 Internet-of-Things and Other Applications

In the future, every single object, no matter in virtual or physical form, could have their unique identifier and communicate with other objects in an internet-like environment, the co-called internet-of-things (IoT). The concept has been addressed widely in recent years [25–27] and it is believed that 30 billion devices will be wirelessly connected to the IoT by 2020 [28]. It is expected that long-range passive RFID systems will take an important role for such applications. By embedding different kinds of sensor [29] to the passive RFID tags, useful data can be transmitted with simple circuitries and low-cost wireless solutions. Some successful examples can be found in [30–32]. Nevertheless the IoT technology development is still in early stages and related implementations are not covered in this work.

Another well-developed area is the road-toll and vehicle identification systems which traditionally require lots of manpower and resources to maintain. The 5.8 GHz ISM band is mainly utilized by these applications and some countries even allow extra emission energy compared to other radio systems [15]. In addition, interest has been shown on applying long-range passive RFID tags to track moveable items and persons such as airport baggage handling and patient tracking in hospitals [7].

### 1.3 An Introduction to UWB Technology

### 1.3.1 A Brief History of UWB Technology

UWB communication is considered as a new technology, indeed it has been invented over a century. The first successful electromagnetic wave experiment done by Heinrich Hertz in 1886 was pulse-based, so was the first radio prototype introduced by Guglielmo Marconi in 1895 [33]. The development of UWB technology continued until NB TXs with amplitude modulation became flexible in about 1915. One of the main reasons for this change was the creation of the continuous-wave oscillator, which followed the invention of the vacuum

<sup>&</sup>lt;sup>3</sup>The characteristic depth of penetration is inversely proportional to  $\sqrt{\omega}$  and given as  $\delta = \sqrt{\frac{2}{\omega\mu\sigma}}$ , where  $\omega$  is the signal angular frequency,  $\mu$  and  $\sigma$  are the permeability and conductivity of the material respectively [21].

<sup>&</sup>lt;sup>4</sup>The diffraction effect can be explained by Huygens-Fresnel principle [24]. However, this involves intensive mathematics and is not discussed in this dissertation.

triode, by Alexander Meissner in 1913 [34].

After this, UWB technology was forgotten for more than four decades. In the early 1960s, sampling oscilloscopes which required sub-nano-second baseband pulses were investigated and aided the development of the UWB field. UWB technology started to be applied on radar applications in the late 1960s [35]. Since the late 1990s, UWB technology has become more commercialized, companies such as Time Domain [36] were formed around the idea of consumer UWB radios [37, 38]. The year 2002 was a milestone of UWB technology, FCC issued a ruling that UWB technology could be used for some applications including imaging and vehicular radar. An extremely wide bandwidth (3.1–10.6 GHz) was released for unlicensed uses on most applications [9]. Since then, UWB technology has drawn lots of attention from both academic and industry. Notice that the term UWB was first introduced around 1989 by the Department of Defense of the United States [37].

UWB radios nowadays can be divided into two forms in literature, orthogonal frequency-division multiplexing and IR. The former one divides the large UWB band into several sub-bands in order to use the BW more efficiently, the latter one intends to generate very short duration impulses. IR radios provide several advantages over the NB counterparts and are focused in this work. The term IR-UWB is adopted in this dissertation to differentiate between these two forms and signify a number of synonymous terms like carrier-free, time domain, and nonsinusoidal.

### 1.3.2 FCC Regulations on UWB Communications

After FCC issued their rules on UWB devices, different countries started to enforce their own standards and regulations [39]. In this work, we mainly focus on utilizing the UWB band (3.1–10.6 GHz) released by FCC since it provides the largest usable BW and, hence, greatest research interest.

#### 1.3.2.1 Definitions of UWB Signals

The following parameters are defined according to [9].

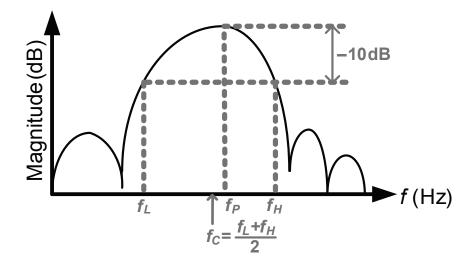

1.  $UWB \ bandwidth \ (BW_{-10dB})$  is the frequency band bounded by the points that are 10 dB below the peak of the power spectrum. The peak frequency is designated to  $f_P$ , the upper boundary is designated  $f_H$  and the lower boundary is designated  $f_L$ . This also means

$$BW_{-10dB} = f_H - f_L (1.2)$$

2. Center frequency  $(f_C)$  is the average of  $f_H$  and  $f_L$ , that is,

$$f_C = \frac{f_H + f_L}{2} \tag{1.3}$$

Figure 1.4: A illustration of several FCC regulation parameters.

### 3. Fractional bandwidth (FB) is defined as

$$FB = \frac{BW_{-10dB}}{f_C} = 2\frac{f_H - f_L}{f_H + f_L}$$

(1.4)

The situation is depicted in Figure 1.4. According to the FCC part 15 regulation [9], transmitted UWB signals need to have a FB equal to or greater than 0.2 or have a  $BW_{-10dB}$  equal to or greater than 500 MHz, regardless of the FB.

#### 1.3.2.2 Emission Energy and Spectrum Mask Regulations

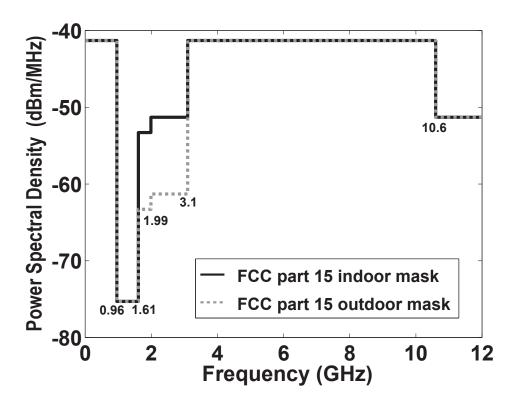

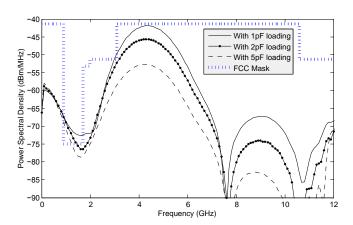

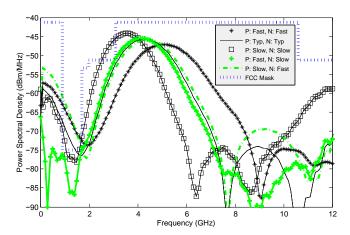

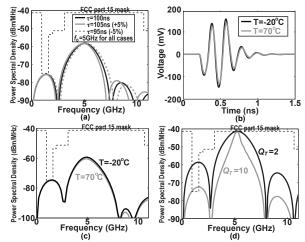

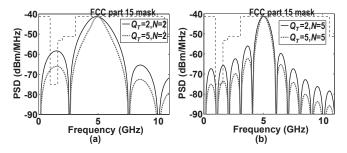

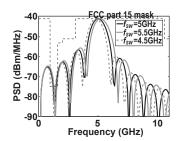

FCC limits the transmitted energy of UWB devices at different frequencies so as to avoid interference with already existing NB radio systems, this can be summarized by the spectral masks depicted in Figure 1.5. The average EIRP of transmitted UWB signals is limited to be -41.3 dBm/MHz within the UWB band and even lower outside this band. Moreover, the peak power contained within a 50 MHz BW centered on  $f_P$  has to be smaller than or equal to 0 dBm EIRP, which is not shown in Figure 1.5.

### 1.3.3 Advantages of UWB Communications

The ultra-wide BW not only provides higher date rate, but also the possibility of reducing system power consumption. It can be proved by considering Shannon's capacity equation

$$C = BW \log_2 \left( 1 + \frac{P_S}{P_N} \right) \tag{1.5}$$

where C is the maximum channel capacity,  $P_S$  and  $P_N$  are the signal and noise powers respectively. Note that the channel capacity grows linearly with BW, but only logarithmically with  $P_S$ . This also implies for the same channel capacity, we can reduce  $P_S$  non-linearly and

Figure 1.5: FCC part 15 indoor and outdoor masks.

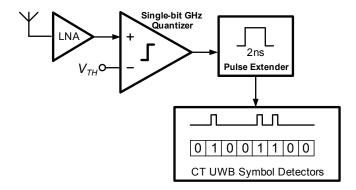

significantly by increasing BW. Furthermore, IR-UWB TXs generate very short-duration impulses which may not require upconversion [38] and clock-less IR-UWB RXs have been reported [14, 40]. IR-UWB radio systems without frequency-conversion are now possible, the circuit complexity, power consumption and chip area can be reduced compared to the conventional NB counterparts.

Another advantage is the excellent localization ability contributed by the extremely short pulse width [8,41], centimeter localization resolution has been demonstrated in [14,42,43]. In addition, the noise-like nature of UWB signals make them difficult for unintended users to detect and robust to eavesdropping [5].

The high temporal resolution of UWB signals results in low fading margins, implying robustness against multipath. The multipath components can also provide an excellent energy capturing capability, for example rake RXs can be implemented to lock into multipath echoes, collect energy and, hence, improve performance. Also some innovative approaches such as location fingerprinting based on the shape of channel impulse responses can be used [44]. Moreover, UWB signals are relatively insensitive to diffraction grating as they span a very wide frequency range. Nevertheless, the UWB band overlaps the frequency bands occupied by other NB radio systems with much higher power levels (for example 802.11a), attention should be paid to the interference issues [5].

### 1.4 Dissertation Outline

The main goal of this work is to apply the IR-UWB technology to advance the current long-range passive RFID system performance. A novel passive IR-UWB RFID system is proposed. This work focuses on the designs and implementations of the TX and related circuits. In the meantime research on RX circuit design has been conducted in the author's research group, with some results published in [14,38]. In addition, research has been conducted on individual components like IR-UWB pulse generator (PG), reference circuit and clock generator for improved performance, especially the power consumption. Reduced power consumption of individual components can improve the sensitivity and supply noise problem of the TX.

This dissertation is written on the basis of a collection of papers. Seven papers are included and listed as follows:

- [I] K. K. Lee, M. Z. Dooghabadi, H. A. Hjortland, Ø. Næss, and T. S. Lande, "A novel 6.5 pJ/pulse impulse radio pulse generator for RFID tags," in *Proc. IEEE Asia Pacific Conference on Circuits and Systems*, Dec 2010, pp. 184–187.

- [II] K. K. Lee, M. Z. Dooghabadi, H. A. Hjortland, Ø. Næss, and T. S. Lande, "A 5.2 pJ/pulse impulse radio pulse generator in 90 nm CMOS," in *Proc. IEEE International Symposium on Circuits and Systems*, May 2011, pp. 1299–1302.

- [III] K. K. Lee, H. A. Hjortland, and T. S. Lande, "IR-UWB technology on next generation RFID systems," in *Proc. NORCHIP*, Nov 2011, DOI: 10.1109/NORCHP. 2011.6126697.

- [IV] K. K. Lee and T. S. Lande, "Analysis and design of sub-μW bandgap references in nano-meter CMOS", in *Proc. IEEE International Midwest Symposium on Circuits and Systems*, Aug 2013, pp. 93–96.

- [V] K. K. Lee, T. S. Lande, and P. D. Häfliger, "A sub-μW bandgap reference circuit with an inherent curvature-compensation property," *IEEE Transactions on Circuits and Systems I: Regular Papers*, to be published, DOI: 10.1109/TCSI.2014.2340553.

- [VI] K. K. Lee and T. S. Lande, "A wireless-powered IR-UWB transmitter for long-range passive RFID tags in 90 nm CMOS," *IEEE Transactions on Circuits and Systems II: Express Briefs*, to be published, DOI: 10.1109/TCSII.2014.2350292.

- [VII] K. K. Lee and T. S. Lande, "A 2.8–7.5 pJ/pulse highly-flexible impulse-radio ultrawideband pulse-generator," preparing for publication.

The following papers are published during the Ph.D. period and contain overlapping, complementing, and additional material, but are not considered part of this dissertation.

- [VIII] K. K. Lee, C. Bryant, M. Törmänen, and H. Sjöland, "A 65-nm CMOS ultra-low-power LC quadrature VCO," in *Proc. NORCHIP*, Nov 2009, DOI: 10.1109/NORCHP.2009.5397805.

- [IX] K. K. Lee, C. Bryant, M. Törmänen, and H. Sjöland, "Design and analysis of an ultra-low-power LC quadrature VCO," *Analog Integrated Circuits and Signal Processing*, vol. 67, no. 1, pp. 49–60, Apr 2011.

- [X] K. K. Lee, Ø. Næss, and T. S. Lande, "A 3.9 pJ/pulse differential IR-UWB pulse generator in 90 nm CMOS," in *Proc. Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics*, Oct 2011, pp. 115–118.

- [XI] K. K. Lee and T. S. Lande, "Co-design of antenna, matching network and voltage rectifier in state-of-the-art CMOS," in *Proc. IEEE International Midwest Symposium on Circuits and Systems*, Aug 2012, pp. 49–52.

- [XII] K. K. Lee, K. Granhaug, and N. Andersen, "A study of low-power crystal oscillator design," in *Proc. NORCHIP*, Nov 2013, DOI: 10.1109/NORCHIP.2013.6702036.

- [XIII] M. Z. Dooghabadi, H. A. Hjortland, Ø. Næss, K. K. Lee, and T. S. Lande, "An IR-UWB transmitter for ranging systems", *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol: 60, no: 11, pp. 721–725, Nov 2013.

This dissertation is organized as follows: Chapter 2 describes the work done by the author in the papers [I–VII] and provides background of the related work in literature. Chapter 3 concludes with a brief summary of the work and a discussion of future research directions. The technical papers are enclosed in the appendix section.

## Chapter 2

## Work Descriptions

This chapter is a guideline for reading papers [I-VII]. The papers can be divided into four main topics: IR-UWB RFID systems, IR-UWB PGs, clock generators and reference circuits. They will be discussed individually in each subsection. Research background and main contributions by the author are presented.

### 2.1 IR-UWB RFID Systems

### 2.1.1 Background

Active IR-UWB RFID systems (including battery-powered IR-UWB transceivers) have been developed and showed very promising results (for example [45–50]). In [45], a communication distance of 200 meters with a maximum error of 15 cm has been achieved. The localization error has even been shown to be as low as 1 cm in [43]. Nevertheless active RFID tags (or the transceiver modules) and batteries are rather expensive (>10 USD) for logistic and supply chain applications. As a balance between the battery lifetime and system performance, a semi-passive IR-UWB RFID system has been proposed in [7] and [51]. The communication is performed by UWB backscattering modulations with a UHF signal (around 900 MHz) wake up. Nevertheless active and semi-passive solutions require battery replacement which makes them not suitable for some applications.

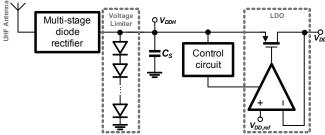

Passive IR-UWB RFID systems (or wireless-powered IR-UWB transceivers) have been reported in [10–12,52–55]. One of the main challenges of wireless-powered IR-UWB radio systems [10–12,52] is to harvest enough energy for data transmissions. The energy-consumption of state-of-the-art IR-UWB PGs is in the order of 10 pJ/pulse [56–60], which corresponds to 100  $\mu$ W with a 10 MHz pulse repetition frequency (PRF), and the efficiency of state-of-the-art far-field RF voltage rectifiers is around 20–30% [61–64]. If we assume that the rectifier efficiency is 25% and an ideal matching network is added such that its insertion loss and the reflection loss can be eliminated, the system minimum input power is 400  $\mu$ W ( $\approx$ –4 dBm) which corresponds a wireless energy transmission distance of approximately three meters by

using (1.1) (Friis transmission equation) with 900 MHz 4 W EIRP radiation and 0 dB gain transmitting/receiving antennas. The power consumption from the other functional blocks and other nonidealities further decrease the distance to less than one meter [10,52].

To increase the energy transmission distance, a multi-mode operation scheme has been adopted in [11, 12, 31] with a potential trade-off of more complicated hand-shake protocols. The idea is to introduce an energy-harvesting mode, only a voltage sensor and related circuits are enabled to minimize the system power consumption (in the order of  $\mu$ W) during this period. A storage capacitor is charged up and other circuits are enabled when enough energy is harvested. An energy transmission distance of 15.7 meters has been reported in [12]. Nevertheless the communication distance of wireless-powered RFID systems is still unsatisfied due to the limited energy available and, hence, weak emission power on the TX side [11, 12]. Notice that the storing energy is given as  $\frac{1}{2}C_SV_{DD}^2$ , where  $V_{DD}$  and  $C_S$  are the supply voltage and capacitance of the storage capacitor respectively. The storing energy could be increased by using a larger storage capacitor, however this also increases the leakage current and charging time. The long charging time may degrade the system capacity performance. In [11, 12, 31],  $C_S$  ranges from 4 to 211 nF, the storing energy is still limited.

Very interesting chip-less IR-UWB solutions<sup>1</sup> (without integrated circuits) have been proposed [32,53–55,67] to further reduce the production cost. The idea is to connect a UWB antenna to different transmission line networks, the backscattered pulses are varied correspondingly and can be used for identifications. The trade-offs are relatively shorter reading range [55] and limited functionalities due to the lack of energy sources on the tags.

#### 2.1.2 Related Work and Contributions

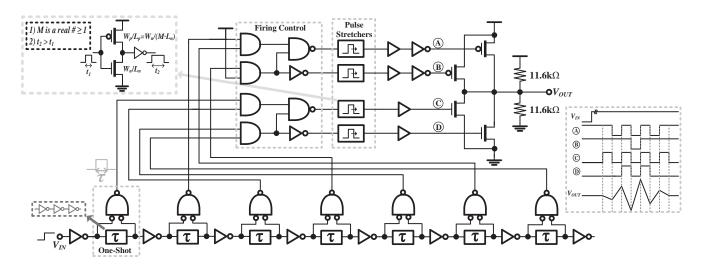

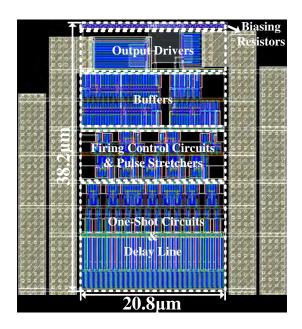

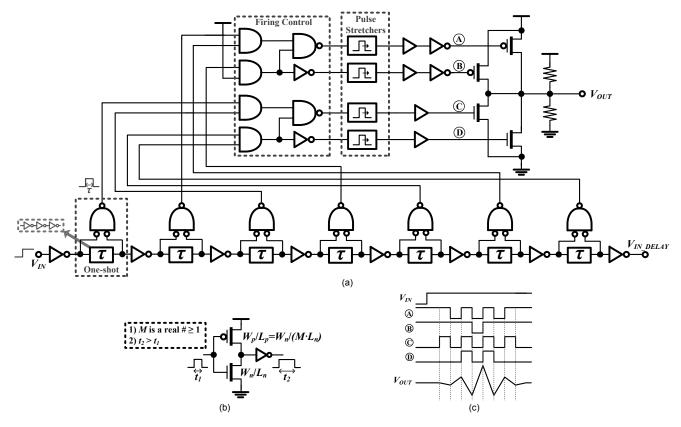

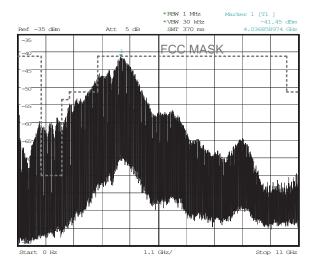

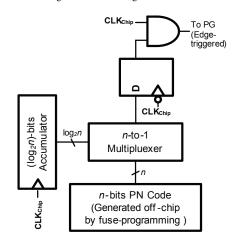

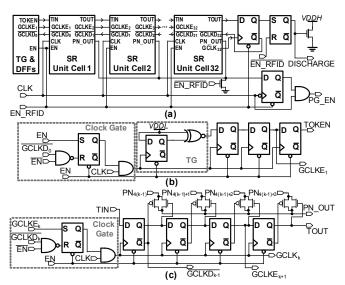

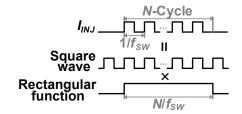

Published wireless-powered IR-UWB tags in literature [10–12,52] offer limited reading range due to the reasons aforementioned. To improve this, the multi-mode operation scheme is adopted and the tag data is transmitted repeatedly, this introduces higher processing gain and averages out the noise. As a result, the signal-to-noise ratio (SNR) and, hence, reading range are increased. Nevertheless the hand-shake protocols become complicated when there are large number of tags and amount of data in the system. This may increase the tag circuit complexity and energy consumption. To solve this, a long-range passive IR-UWB RFID system using a uni-directional communication scheme has been proposed in [III] and slightly modified in [VI]. The channel separation is given by the system asynchronous code-division multiple access (CDMA) and inherent ALOHA properties. Every tag requires different time to harvest energy due to process variation, component mismatch and distance to the readers, transmissions will be sufficiently distributed for acceptable interference, even with a large number of tags in operation.

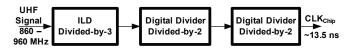

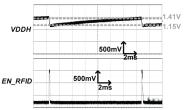

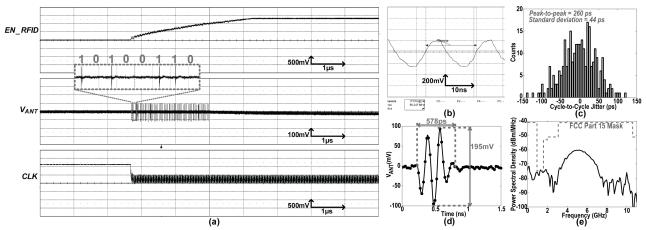

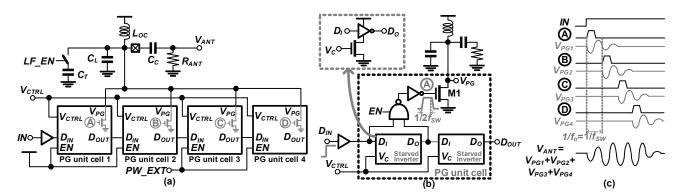

A wireless-powered CDMA IR-UWB TX for the proposed RFID system has been presented in [VI]. The TX is wireless-powered by a 900 MHz UHF signal and starts transmissions of symbols containing 128-b PN codes when enough energy is harvested. On-off-key

<sup>&</sup>lt;sup>1</sup>Chipless RFID solutions are used on NB RFID systems also, more details can be found in [65] and [66].

(OOK) modulation is adopted because of the simple structure and low energy consumption of OOK PGs, although bi-phase shift key (BPSK) modulation could provide better communication quality [68]. System co-designs of different building blocks are proposed to improve tags performance without additional power consumption overhead. A proof-of-concept prototype has been successfully implemented in the TSMC 90 nm CMOS process. Together with elaborate RX design (an exampled structure can be found in [14]), the proposed RFID system can provide precise RTL ability. Only localization techniques which do not require synchronization between readers and tags can be used to locate the tags. The angle-of-arrival (AoA) approach is chosen as an example. Considering a reader containing an antenna array with known geometry, the AoA is estimated from the differences in arrival times for the tag transmitted signal at each of the antennas. As a result, a radial line can be formed from the reader to the tag. Precise localization can be performed by using multiple readers and intersecting the resultant radial lines. Other localization techniques and trade-offs can be found in [37,68,69].

### 2.2 IR-UWB PGs

### 2.2.1 Background

One of the most important components inside IR-UWB TXs is the PG. It is usually the most power-demanding component and the communication distance is greatly related to its emission energy. At the same time the emitted signal has to meet the spectrum regulation of different country to avoid interfering with other radio systems.

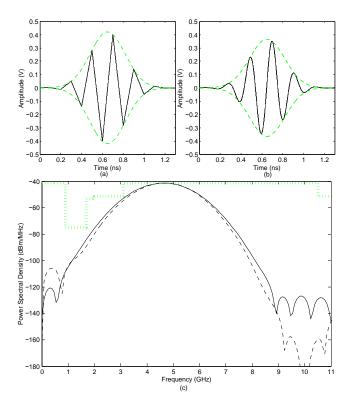

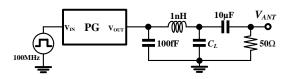

The basic idea of most published IR-UWB PGs is to use a high-frequency waveform generator (HFWG), which can be an oscillator, phase-locked loop or delay-line (DL), and shape its output signal to generate the desired envelope by mainly three approaches: spectrum mixing [46, 47, 49, 56, 70–72], filtering [11, 57, 58, 73–75] or multi-pulse combination (MPC) [59, 60, 76–79]. The spectrum mixing approach consists of a local oscillator and a mixer like conventional NB TXs, the high-frequency oscillator output is then mixed with the envelope shape [46, 47, 49, 70]. The power consumption and area are relatively large because more components are needed compared to the other two approaches. Moreover, the leakage from the oscillator to the antenna could be problematic. However, it is the one of the very few PG topologies that can generate high-quality BPSK IR-UWB signals. The mixing function could also be performed by switching the oscillator on and off [56,71,72], this eliminates the need of the mixer with a drawback of disability of generating BPSK signals.

For the filtering approach, the HFWG output signal is coupled to and filtered by a pulse shaping filter so that the resultant signal can meet the spectrum mask regulations. In additional to the circuit simplicity, another advantage is that the output parasitic capacitance, which is usually the dominating one inside the PG, can be used as part of the filter and tunedout by inductors inside the filter. In other words, the capacitive and switching losses could be reduced. However, the filtered out-of-band energy is wasted and on-chip spiral inductors

are area-demanding.

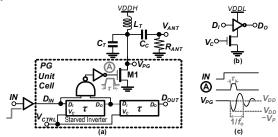

MPC IR-UWB PGs usually utilize DLs as the HFWG. Based on the propagation delay (PD) of the DL and output drivers with different strength, Gaussian-approximate waveforms can be obtained. The MPC approach is shown to be very energy-efficient (2.5 pJ/pulse has been reported in [59]) and small-size because it contains mainly digital gates. Nevertheless most of the MPC IR-UWB PGs operate at the lower frequencies of the UWB band, this is because the capacitive and switching losses due to the output parasitic capacitance increase with frequency. Also, it is not easy to control the envelope and center frequency accurately due to process variations, filtering and/or calibration may be required. Note that for some MPC IR-UWB PGs [59, 76–78], the direct-current (DC) output voltage of output drivers is biased by the transistor leakage current which is usually not accurately modeled, this may increase the design difficulty.

#### 2.2.2 Related Work and Contributions

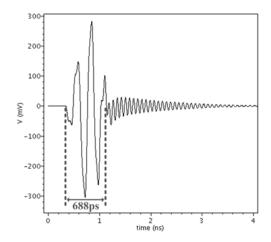

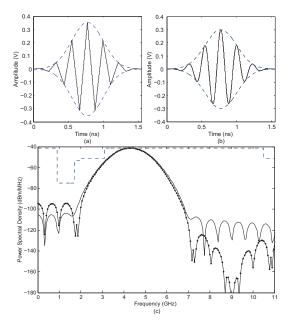

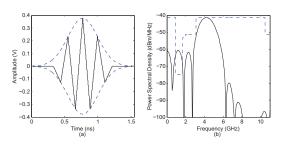

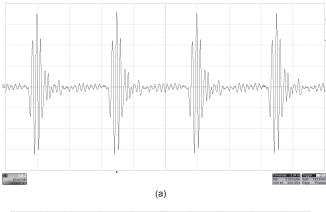

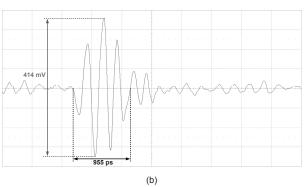

In [I], a low-power DL-based MPC OOK IR-UWB PG structure (will be referred to as PG-I) which utilizes loose-triangular waveforms to construct a Gaussian envelope has been proposed. An acceptable spectral filling is achieved with simple circuit solutions. PG-I has been successfully implemented in a TSMC 90 nm CMOS process in [II]. Because it contains mainly digital gates, low energy consumption and chip area are obtained. A resistive divider is used to bias the DC output voltage instead of the leakage current solution adopted in [59] and [76], this can control the variation of the DC output voltage better. However, the energy consumption increases when the PRF decreases because of the static current drawn by the resistive divider. To solve this, a dynamic pre-charge scheme which turns on the resistive divider a short time before transmissions has been proposed in [II]. PG-I has been adopted in an IR-UWB TX for ranging systems presented in [XIII] and [14]. The presented TX could also be applied to active and semi-passive IR-UWB RFID systems. Note that there are differences between the post-layout simulation results in [I] and measurement results in [II], this is because the envelope and center frequency of the PG output signal are sensitive to the PD variation of the DL. Other possible reasons are the inaccuracies of the layout parasitic component extraction tools and the transistor models provided by the vendor.

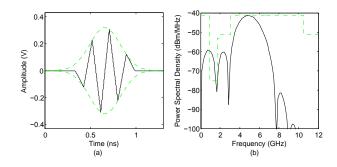

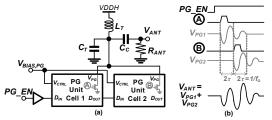

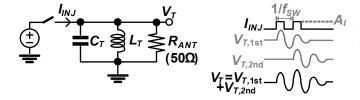

Another DL-based MPC OOK IR-UWB PG structure (will be referred to as PG-II) has been proposed in [VI]. It uses an on-chip spiral inductor to tune out the output parasitic capacitance, the driving requirement and, hence, the transistor size of the output drivers are reduced. In other words, the capacitive and switching losses are also reduced which makes PG-II energy-efficient. Also, energy is concentrated at around the resonating frequency of the LC tank because of the its bandpass property, this makes PG-II less sensitive to the mismatch and temperature variation. The inductor connects the PG output to the supply voltage at low frequencies which provides electrostatic discharge protection. PG-II has been used in the wireless-powered IR-UWB TX presented in [VI].

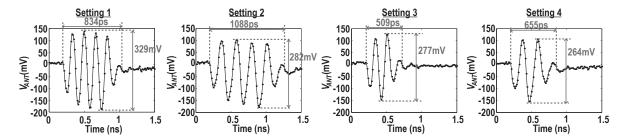

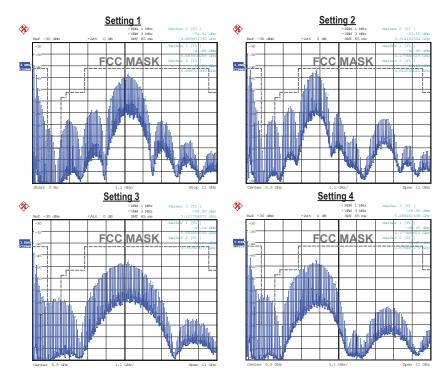

Because of the TX multi-mode operations and limited number of pad counts, some important specifications of PG-II have not been measured in [VI]. In [VII], an improved version

of PG-II with higher flexibility (will be referred to as PG-III) has been proposed. In addition, detailed measurement results, qualitative frequency-domain and transient analyses are presented. A new figure-of-merit (FoM) has been proposed to compare different IR-UWB PGs in a more precise way. Both PG-I and PG-III show competitive performance compared to other published state-of-the-art IR-UWB PGs [VII].

### 2.3 Clock Generators

### 2.3.1 Background

Crystal oscillators (XO) are used extensively in modern radio systems. It can generate very precise and stable reference clock signals because of the extremely high quality factor (QF, in the order of 100,000) of the crystal resonators [80,81]. Normal XOs can provide frequency stability in the order of 10 parts per million (ppm) over a wide temperature range, this can even be improved to 0.05 ppm with analog temperature compensation [82]. However, the maximum fundamental oscillating frequency is up to around 30 MHz only [83]. Microelectro-mechanical systems (MEMS) resonators have been proposed [84] and the maximum fundamental oscillating frequency is increased to the GHz range with a trade-off of lower QF (in the order of 1,000) [82,85]. The smaller size of the MEMS resonators [86,87] also enables the possibility of embedding the whole front-end in a single package (the so-called system-in-package solution) for improved performance. Note that the oscillator power consumption is inversely proportional to the resonator QF, on the other hand the start-up time is exponentially proportional to the resonator QF [XII]. The long start-up time may limit the usability of crystal/MEMS oscillators on IR-UWB TXs which are usually turned on and off from time to time.

Ring oscillators are possible candidates for passive RFID systems [88] because of their simplicity and energy efficiency. However, the output frequency varies with temperature, this may limit the system operating temperature range. Temperature-compensated ring oscillators have been proposed to reduce the frequency variation (can be less than 1% over a temperature range of  $100^{\circ}$ C [89–91]) with slightly increased complexity. Nevertheless the output frequency error due to process variations can be as large as  $\pm 20\%$ , post digital signal processing [92] and/or trimming may be required.

Very accurate chip-rate is usually required for CDMA systems. A possible low-power solution for wireless-powered radio systems is to lock to the input RF signals with simple circuitries. A clock recovery solution using a digital frequency-locked loop has been proposed in [93] for Electronic Product Code<sup>2</sup> generation-2 RFID tags [94]. Injection-locking solutions have been proposed in [11, 30, 95–98]. They provide lower circuit complexity, faster start-up time (including locking time) and, thus, better energy efficiency compared to the clock recovery solution. However, for most injection-locking frequency dividers (ILD) for RFID applications, the injection input generates a resistive load to the antenna which induces losses

<sup>&</sup>lt;sup>2</sup>Electronic Product Code provides well-accepted RFID standards and data structures.

#### 2.3.2 Related Work and Contributions

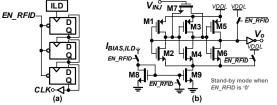

The injection-locking approach is adopted for the proposed IR-UWB RFID system because of the high energy-efficiency advantage. If the targeted output frequency is close to the ILD free-running oscillating frequency, the start-up time (including lock time) can be very short (a few clock cycles according to simulations). A novel ILD co-designed with RF voltage rectifier has been proposed in [VI]. It is based on the structure proposed in [99]. Unlike other ILDs for RFID applications [11, 30, 95], the DC voltage of the injection input is biased by either resistors or diode-connected transistors which generate resistive loads to the antenna and degrade the sensitivity, the proposed ILD co-designs with the RF voltage rectifier and introduces only a small capacitive load to the antenna. As a result, this reduces the resistive loss and the system sensitivity is improved. The proposed ILD has been successfully implemented in the TSMC 90 nm CMOS process and adopted in the wireless-powered IR-UWB TX presented in [VI].

### 2.4 Reference Circuits

### 2.4.1 Background

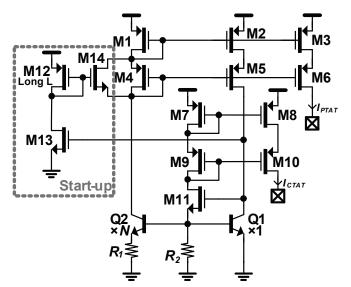

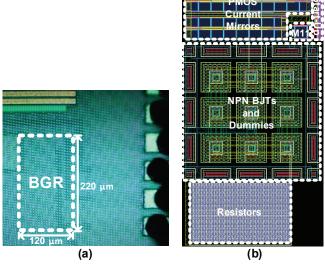

Bandgap reference circuits (BGR) generate precise reference signals which are insensitive to process, voltage and temperature variations, and have been used for decades because of their reliability. However, very low power consumption (sub- $\mu$ W or even lower) is needed for the wireless-powered applications [30, 100], large resistance is needed in order to achieve this. This can increase the chip area substansiously. As a result, only a few sub- $\mu$ W BGRs can be found in literature [30,101,102]. Some research has been conducted on CMOS-only reference circuits which generate the output voltage based on CMOS transistor threshold voltage [103–105] or its difference [106, 107]. Nevertheless, design trade-offs such as sensitivity to process variations, precision and flexibility have to be considered also.

The minimum width of resistors scales down with the continuing aggressive development of CMOS technology. Mega-ohm resistors can now be realized with a reasonable area in state-of-the-art CMOS processes, hence sub- $\mu$ W BGR power consumption is now possible. For example the high-resistance poly resistor without salicide in the TSMC 90 nm CMOS process, its resistivity can be as large as 0.16 M $\Omega$  per 100  $\mu$ m $^2$  and would increase even more favorably with more modern technology nodes. The resistor area is now less dominating, and becomes comparable to other components for BGR design.

Another important BGR design parameter is the temperature coefficient (TC). For CMOS BGRs, this non-ideality is mainly due to the high-order temperature dependence of bipolar junction transistor (BJT) base-emitter voltage [108–110]. Different temperature compensation techniques have been developed [111–122], most of them require additional components

and power consumption. A remarkable exception is [121], the BGR high-order temperature dependence is compensated by incorporating two different types of resistor whose first-order TCs are of opposite sign. Nevertheless intensive trimming may be needed to match the resistor ratios because the resistors are with different types. More curvature-compensation techniques and related discussion can be found in [123].

#### 2.4.2 Related Work and Contributions

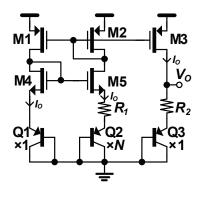

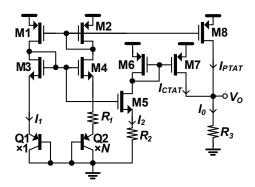

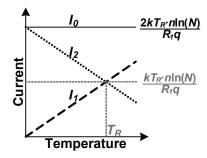

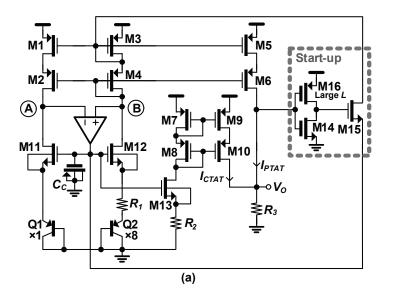

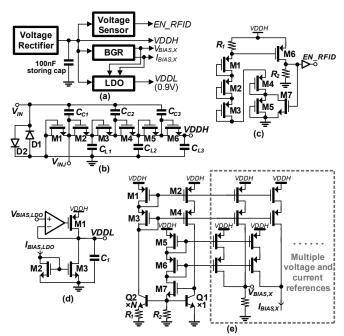

An analysis of ultra-low-power BGR designs in nm CMOS processes has been presented in [IV]. Three different widely-used BGR topologies have been studied. One of them (will be referred to as BGR-I) is very interesting with limited results reported. To get more insight, BGR-I has been implemented in the TSMC 90 nm CMOS process and verified. BGR-I has been used in the wireless-powered IR-UWB TX presented in [VI].

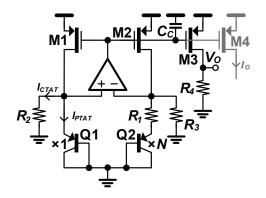

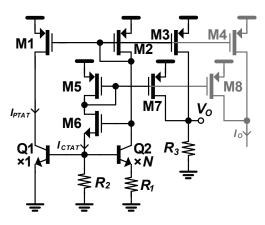

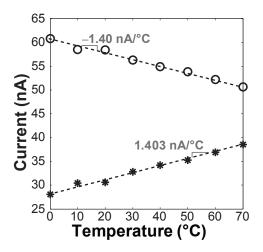

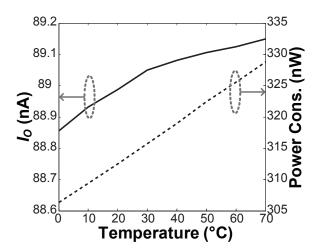

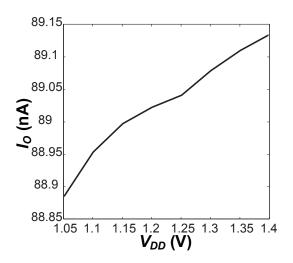

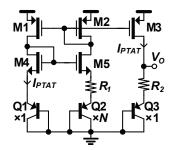

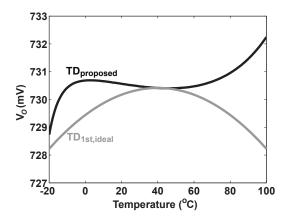

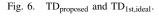

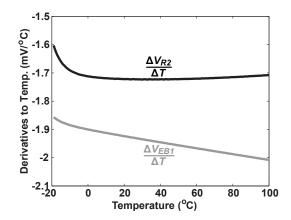

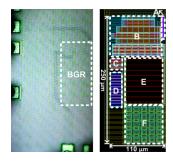

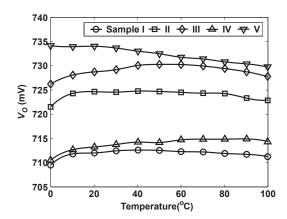

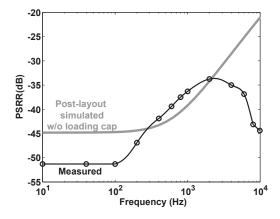

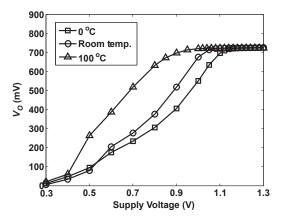

A detailed discussion between resistor-based BGRs and CMOS-only reference circuits and different design considerations of ultra-low-power BGRs in nm CMOS processes have been presented in [V]. In addition, a new current-mode BGR topology with an inherent curvature-compensation property (will be referred to as BGR-II) has been presented. The proposed curvature-compensation technique utilizes the exponential behavior of sub-threshold CMOS transistors to compensate the BJT base-emitter voltage high-order temperature dependence and improves the TC performance. The proposed curvature-compensation technique is simple and requires no additional current consumption. Also, BGR-II is capable of generating sub-1-V output voltage and has the lowest theoretical minimum current consumption among published current-mode BGRs. BGR-II has been successfully demonstrated in the TSMC 90 nm CMOS process.

"Worry does not empty tomorrow of its sorrow, it empties today of its strength."

— Corrie ten Boom

## Chapter 3

## Summary and Future Work

### 3.1 Summary

A novel long-range passive IR-UWB RFID system intended to advance the current RFID technology has been proposed in [III] and [VI]. The potential advantages are a long reading range with localization ability, insensitivity to surrounding environments and high security. In [VI], a wireless-powered CDMA IR-UWB TX intended for the proposed RFID system has been implemented in the TSMC 90 nm CMOS process and presented. Moreover, novel IR-UWB PG (PG-II), ILD and co-design schemes have been proposed to improve the TX performance with minimal power consumption overheads. The proposed RFID tag provides sufficient bandwidth for potential resolution in the centimeter range. Notice that the reader side has not been implemented due to the limited resources and time, demonstrations of the system performance require experimental verifications. Although high-precision long-range localizations have been demonstrated in [42], interference and practical limitations will probably limit localization performance in real scenarios.

In addition, several functional blocks for low-power IR-UWB radio systems have been proposed and analyzed. A OOK IR-UWB PG (PG-I) has been proposed in [I] and demonstrated in [II]. It is energy-efficient and small-size because it contains mainly digital gate. PG-I has been adopted in an IR-UWB TX for ranging systems presented in [XIII]. In [VII], a low-power highly-flexible IR-UWB PG (PG-III, which is an improved version of PG-II) has been presented. The output power, PW and center frequency are controllable. Qualitative frequency-domain and transient analyses have been presented. A new FoM has been proposed to compare different IR-UWB PGs in a more precise way. Both PG-I and PG-III show competitive performance compared to other published state-of-the-art IR-UWB PGs as shown in [VII].

In [IV], an analysis of ultra-low-power BGR designs in nm CMOS processes has been presented, a BGR topology with limited results reported in literature (BGR-I) has been fabricated to get more insight. A detailed discussion between resistor-based BGRs and CMOS-only reference circuits and different design considerations of ultra-low-power BGRs in state-of-the-art nm CMOS processes have been presented in [V]. Also, a sub- $\mu$ W BGR with an

Figure 3.1: An idea of piecewise-linear curvature-compensation.

inherent curvature-compensation property (BGR-II) has been proposed and shown competitive results with other state-of-the-art voltage reference circuits.

### 3.2 Recommendations for Future Work

#### **Full System Demonstrations**

Although individual IR-UWB TX and RX for the proposed RFID system have been proposed in this work and [14] respectively, the full system has not been demonstrated yet because of the reasons aforementioned. Additional reader and control circuits are required. Furthermore, localization techniques like AoA and time-difference-of-arrival [37,68,69,124] and control algorithms are required for RTL applications. Additional research on signal processings is needed for optimizing the system performance.

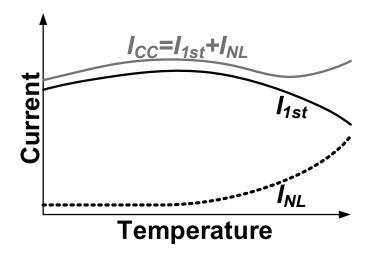

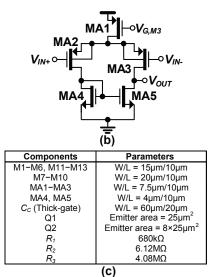

## Implementations of BGR-II with piecewise-linear curvature-compensation and/or trimming.

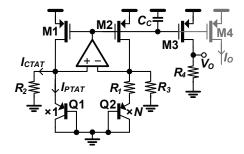

Piecewise-linear curvature-compensation technique has been widely used on current-mode BGR designs [115–119] to extend the operating temperature range and, thus, reduce the TC. The idea is shown in Figure 3.1. The output current of a first-order BGR ( $I_{1st}$ ) is summed with non-linear current ( $I_{NL}$ ) which can be generated with simple CMOS circuits, the resultant current ( $I_{CC}$ ) is second-order (or even higher-order) curvature-compensated. More details can be found in [125]. It may be possible to apply such technique to BGR-II for improved performance. In addition, the unwanted effects due to process variations can be minimized by trimming the resistor ratios [118, 121], this can improve both the TC and output variation performance which may be preferred for high-precision applications. The trade-offs are increased chip area, cost and testing time.

## Bibliography

- [1] D. C. Ranasinghe, Q. Z. Sheng, and S. Zeadally, *Unique Radio Innovation for the 21st Century: Building Scalable and Global RFID Networks*. Heidelberg: Springer, 2010.

- [2] A. Rida, L. Yang, and M.Tentzeris, *RFID-Enabled Sensor Design and Applications*. Norwood: Artech House, 2010.

- [3] R. Das and P. Harrop, RFID Forecasts, Players and Opportunities 2014–2024. IDTechEx, 2013.

- [4] C. Jechlitschek, "A survey paper on radio frequency identification (RFID) trends." [Online]. Available: http://www.cse.wustl.edu/~jain/cse574-06/ftp/rfid/

- [5] H. Arslan, Z. N. Chen, and M.-G. D. Benedetto, *Ultra Wideband Wireless Communication*. New Jersey: John Wiley & Sons, 2006.

- [6] Discussions during the *RFID Hand-On Workshop*, University of California, Los Angeles, 29 Sep 2010.

- [7] Deliverables from SELECT (an EU FP7 project), 2010–2014. [Online]. Available: http://www.selectwireless.eu

- [8] H. Lücken, Communication and Localization in UWB Sensor Network. Ph.D. dissertation, Logos Verlag Berlin, 2013.

- [9] FCC, Revision of Part 15 of the Commission's Rules Regarding Ultra-Wideband Transmission Systems, adopted Feb 2002, released Apr 2002.

- [10] [Online]. Available: http://www.tagent.com

- [11] M. Baghaei-Nejad, *Ultra Wideband Impulse Radio for Wireless Sensing and Identification*. Ph.D. Dissertation, Royal Institute of Technology, 2008.

- [12] S. Radiom, M. Baghaei-Nejad, K. Mohammadpour-Aghdam, G. A. E. Vandenbosch, L.-R. Zheng, and G. G. E. Gielen, "Far-field on-chip antennas monolithically integrated in a wireless-powered 5.8 GHz downlink/UWB uplink RFID tag in 0.18-μm standard CMOS," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 9, pp. 1746–1758, Sep 2010.

- [13] TSMC 90nm CMOS low power MS/RF 1P9M\_6X1N1U process.

- [14] S. Sudalaiyandi, H. A. Hjortland, and T. S. Lande, "A continuous-time IR-UWB RAKE receiver for coherent symbol detection," *Analog Integrated Circuits and Signal Processing*, vol. 77, no. 1, pp. 17–27, Oct 2013.

- [15] K. Finkenzeller, RFID Handbook: Fundamentals and Applications in Contactless Smart Cards, Radio Frequency Identification and Near-Field Communication, 3rd ed. West Sussex: John Wiley & Sons, 2010.

- [16] S. Preradovic, Advanced Radio Frequency Identification Design and Applications. Intech, 2011.

- [17] NXP UCODE G2XM RFID tag chip family.

- [18] Impinj Monza 4 RFID tag chip family.

- [19] SkyRFID Inc, "RFID tag maximum read distance." [Online]. Available: http://skyrfid.com/RFID\_Tag\_Read\_Ranges.php

- [20] B. Otis and J. Rabaey, *Ultra-Low Power Wireless Technologies for Sensor Network*. New York: Springer, 2007.

- [21] D. Pozar, Microwave Engineering, 3rd ed. New York: John Wiley & Sons, 2005.

- [22] GS1, "Regulatory status for using RFID in the EPC Gen 2 band (860 to 960 MHz) of the UHF spectrum," released 31 May 2013. [Online]. Available: http://www.gs1.org/docs/epcglobal/UHF\_Regulations.pdf

- [23] J.-P. Curty, M. Declercq, C. Dehollain, and N. Joehl, *Design and Optimization of Passive UHF RFID Systems*. New York: Springer, 2007.

- [24] A. F. Molisch, Wireless Communications, 2nd ed. West Sussex: John Wiley & Sons, 2011.

- [25] C.-W. Tsai, C.-F. Lai, M.-C. Chiang, and L. Yang, "Data mining for internet of things: A survey," *IEEE Communications Surveys & Tutorials*, vol. 16, no. 1, pp. 77–97, first quarter 2014.

- [26] J. Zheng, D. Simplot-Ryl, C. Bisdikian, and H. T. Mouftah, "The internet of things," *IEEE Communications Magazine*, vol. 49, no. 11, pp. 30–31, Nov 2011.

- [27] P. Corke, T. Wark, R. Jurdak, W. Hu, P. Valencia, and D. Moore, "Environmental wireless sensor networks," *Proceedings of the IEEE*, vol. 98, no. 11, pp. 1903–1917, Nov 2010.

- [28] ABI Research, "More than 30 billion devices will wirelessly connect to the internet of everything in 2020," released 9 May 2013.

- [29] J. Bryzek, "Emergence of a \$trillion MEMS sensor market," in Sensors Con, Mar 2012.

- [30] J. Yin, J. Yi, M. Law, Y. Ling, M. C. Lee, K. P. Ng, B. Gao, H. C. Luong, A. Bermak, M. Chan, W.-H. Ki, C.-Y. Tsui, and M. Yuen, "A system-on-chip EPC gen-2 passive UHF RFID tag with embedded temperature sensor," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 11, pp. 2404–2420, Nov 2010.

- [31] F. Kocer and M. P. Flynn, "A new transponder architecture with on-chip ADC for long-range telemetry applications," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 5, pp. 1142–1148, May 2006.

- [32] D. Girbau, A. Ramos, A. Lazaro, S. Rima, and R. Villarino, "Passive wireless temperature sensor based on time-coded UWB chipless RFID tags," *IEEE Transactions on Microwave Theory and Techniques*, vol. 60, no. 11, pp. 3623–3632, Nov 2012.

- [33] M. Z. Win, D. Dardari, A. F. Molisch, W. Wiesbeck, and J. Zhang, "History and applications of UWB," *Proceedings of the IEEE*, vol. 97, no. 2, pp. 198–204, Feb 2009.

- [34] A. Grebennikov, *RF and Microwave Transmitter Design*. New Jersey: John Wiley & Sons, 2011.

- [35] T. W. Barrett, "History of ultra wideband (UWB) radar & communications: Pioneers and innovators," in *Proc. Progress in Electromagnetics Symposium*, Jul 2000.

- [36] [Online]. Available: http://www.timedomain.com

- [37] M. Ghavami, L. B. Michael, and R. Kohno, *Ultra Wideband Signals and Systems in Communication Engineering*. West Sussex: John Wiley & Sons, 2004.

- [38] T. A. Vu, IR-UWB Receiver Front-End for WSN Applications. Ph.D. Dissertation, University of Oslo, 2013.

- [39] WiMedia Alliance, "Worldwide regulatory status," released Jan 2009.

- [40] H. A. Hjortland and T. S. Lande, "CTBV integrated impulse radio design for biomedical applications," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 3, no. 2, pp. 79–88, Apr 2009.

- [41] Z. Sahinoglu, S. Gezici, and I. Guvenc, *Ultra-Wideband Positioning Systems: Theoretical Limits, Ranging Algorithms, and Protocols.* Cambridge: Cambridge University Press, 2008.

- [42] Novelda AS, "The bits, pieces and ideas inside XeThru by Novelda." [Online]. Available: https://www.xethru.com/content/technology-0

- [43] M. K. Kang and T. W. Kim, "CMOS IR-UWB receiver for  $\pm 9.7$ -mm range finding in a multipath environment," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 59, no. 9, pp. 538–542, Sep 2012.

- [44] C. Steiner, Location Fingerprinting for Ultra-Wideband Systems: the Key to Efficient and Robust Localization. Ph.D. dissertation, Swiss Federal Institute of Technology in Zurich, 2010.

- [45] J. Xia, C. L. Law, Y. Zhou, and K. S. Koh, "3–5 GHz UWB impulse radio transmitter and receiver MMIC optimized for long range precision wireless sensor network," *IEEE Transactions on Microwave Theory and Techniques*, vol. 58, no. 12, pp. 4040–4051, Dec 2010.

- [46] S. Joo, W.-H. Chen, T.-Y. Choi, M.-K. Oh, J.-H. Park, J.-Y. Kim, and B. Jung, "A fully integrated 802.15.4a IR-UWB transceiver in 0.13 μm CMOS with digital RRC synthesis," in *IEEE ISSCC Dig. Tech. Papers*, Feb 2010, pp. 228–229.

- [47] Y. Zheng, M. A. Arasu, K.-W. Wong, Y. J. The, A. P. H. Suan, D. D. Tran, W. G. Yeoh, and D.-L. Kwong, "A 0.18μm CMOS 802.15.4a UWB transceiver for communication and localization," in *IEEE ISSCC Dig. Tech. Papers*, Feb 2008, pp. 118–119.

- [48] Zebra Technologies, "Dart UWB technology brochure," Rev6 (10/12).

- [49] L. Zhou, Z. Chen, C.-C. Wang, F. Tzeng, V. Jain, and P. Heydari, "A 2-Gb/s 130-nm CMOS RF-correlation-based IR-UWB transceiver front-end," *IEEE Transactions on Microwave Theory and Techniques*, vol. 59, no. 4, pp. 1117–1130, Jan 2011.

- [50] X. Y. Wang, R. K. Dokania, and A. B. Apsel, "A crystal-less self-synchronized bit-level duty-cycled IR-UWB transceiver system," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 60, no. 9, pp. 2488–2501, Sep 2013.

- [51] R. D'Errico, M. Bottazzi, F. Natali, E. Savioli, S. Bartoletti, A. Conti, D. Dardari, N. Decarli, F. Guidi, F. Dehmas, L. Ouvry, U. Alvarado, N. Hadaschik, C. Franke, Z. Mhanna, M. Sacko, Y. Wei, and A. Sibille, "An UWB-UHF semi-passive RFID System for localization and tracking applications," in *Proc. IEEE International Conference on RFID-Technologies and Applications*, Nov 2012, pp. 18–23.

- [52] M. Pelissier, J. Jantunen, B. Gomez, J. Arponen, G. Masson, S. Dia, J. Varteva, and M. Gary, "A 112 Mb/s full duplex remotely-powered impulse-UWB RFID transceiver for wireless NV-memory applications," *IEEE Journal of Solid-State Circuits*, vol. 46, no. 4, pp. 916–927, Apr 2011.

- [53] S. Hu, Y. Zhou, C. L. Law, and W. Dou, "Study of a uniplanar monopole antenna for chipless UWB-RFID localization system," *IEEE Transactions on Antennas and Propagation*, vol. 58, no. 2, pp. 271–278, Feb 2010.

- [54] P. Kalansuriya and N. Karmakar, "Time domain analysis of a backscattering frequency signature based chipless RFID tag," in *Proc. Asia-Pacific Microwave Conference*, Dec 2011, pp. 183–186.

- [55] Y. Shen, C. L. Law, S. Hu, and J. Xia, "IR-UWB-based chipless RFID system," *Annals of Telecommunications*, vol. 68, no. 7–8, pp. 375–383, Aug 2013.

- [56] T.-A. Phan, J. Lee, V. Krizhanovskii, S.-K. Han, and S.-G. Lee, "A 18-pJ/pulse OOK CMOS transmitter for multiband UWB impulse radio," *IEEE Microwave and Wireless Components Letters*, vol. 17, no. 9, pp. 688–690, Sep 2007.

- [57] S. Sim, D.-W. Kim, and S. Hong, "A CMOS UWB pulse generator for 6–10 GHz applications," *IEEE Microwave and Wireless Components Letters*, vol. 19, no. 2, pp. 83–85, Feb 2009.

- [58] S. Bourdel, Y. Bachelet, J. Gaubert, R. Vauche, O. Fourquin, N. Dehaese, and H. Barthelemy, "A 9-pJ/pulse 1.42-Vpp OOK CMOS UWB pulse generator for the 3.1–10.6-GHz FCC band," *IEEE Transactions on Microwave Theory and Techniques*, vol. 58, no. 1, pp. 65–73, Jan 2010.

- [59] L. Wang, R. Chandrasekaran, and Y. Lian, "A 3–5GHz all-digital CMOS UWB pulse generator," in *Proc. Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics*, Sep 2010, pp. 388–391.

- [60] M. J. Zhao, B. Li, and Z. H. Wu, "20-pJ/pulse 250 Mbps low-complexity CMOS UWB transmitter for 3–5 GHz applications," *IEEE Microwave and Wireless Components Letters*, vol. 23, no. 3, pp. 158–160, Mar 2013.

- [61] J. Yi, W.-H. Ki, and C.-Y. Tsui, "Analysis and design strategy of UHF micro-power CMOS rectifiers for micro-sensor and RFID applications," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 54, no. 1, pp. 153–166, Jan 2007.

- [62] K. Kotani, A. Sasaki, and T. Ito, "High-efficiency differential-drive CMOS rectifier for UHF RFIDs," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 11, pp. 3011–3018, Nov 2009.

- [63] R. E. Barnett, L. Jin, and S. Lazar, "A RF to DC voltage conversion model for multi-stage rectifiers in UHF RFID transponders," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 2, pp. 354–370, Feb 2009.

- [64] G. Papotto, F. Carrara, and G. Palmisano, "A 90-nm CMOS threshold-compensated RF energy harvester," *IEEE Journal Solid-State Circuits*, vol. 46, no. 9, pp. 1985–1997, Sep 2011.

- [65] S. Preradovic and N. C. Karmakar, *Multiresonator-Based Chipless RFID: Barcode of the Future*. New York: Springer, 2012.

- [66] S. Preradovic and N. C. Karmakar, "Design of chipless RFID tag for operation on flexible laminates," *IEEE Antennas and Wireless Propagation Letters*, vol. 9, pp. 207–210, Mar 2010.

- [67] Y. F. Weng, S. W. Cheung, T. I. Yuk, and L. Liu, "Design of chipless UWB RFID system using a CPW multi-resonator," *IEEE Antennas and Propagation Magazine*, vol. 55, no. 1, pp. 13–31, Feb 2013.

- [68] Z. Zou, Impulse Radio UWB for the Internet-of-Things: A Study on UHF/UWB Hybrid Solution. Ph.D. Dissertation, Royal Institute of Technology, 2011.

- [69] N. Patwari, J. N. Ash, S. Kyperountas, A. O. Hero, R. L. Moses, and N. S. Correal, "Locating the nodes: cooperative localization in wireless sensor networks," *IEEE Signal Processing Letters*, vol. 22, no. 4, pp. 54–69, Jul 2005.

- [70] J. Ryckaert, G. Van der Plas, V. De Heyn, C. Desset, G. Vanwijnsberghe, B. Van Poucke, and J. Craninckx, "A 0.65-to-1.4nJ/burst 3-to-10GHz UWB all-digital TX in 90nm CMOS for IEEE 802.15.4a," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 12, pp. 2860–2869, Dec 2007.

- [71] K.-K. Huang, J. K. Brown, E. Ansari, R. R. Rogel, Y. Lee, H. Kim, and D. D. Wentzloff, "An ultra-low-power 9.8 GHz crystal-less UWB transceiver with digital baseband integrated in 0.18 μm BiCMOS," *IEEE Journal on Solid-State Circuits*, vol. 48, no. 12, pp. 3178–3189, Dec 2013.

- [72] S. X. Diao, Y. J. Zheng, and C. H. Heng, "A CMOS ultra low-power and highly efficient UWB-IR transmitter for WPAN applications," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 56, no. 3, pp. 200–204, Mar 2009.

- [73] E. Muhr, R. Vauche, S. Bourdel, J. Gaubert, O. R. Sparrow, N. Dehaese, I. Benamor, and H. Barthelemy, "High output dynamic UWB pulse generator for BPSK modulations," in *Proc. IEEE International Conference on Ultra-Wideband*, Sep 2013, pp. 170–174.

- [74] M. Shen, Y.-Z. Yin, H. Jiang, T. Tian, and J. H. Mikkelsen, "A 3–10 GHz IR-UWB CMOS pulse generator with 6 mW peak power dissipation sing a slow-charge fast-discharge technique," *IEEE Microwave and Wireless Components Letters*, 2014, DOI 10.1109/LMWC.2014.2332057.

- [75] J. Jiang, K. Shao, B. Lu, H. Chen, L. Xia, Z. Hong, and Q. Chen, "A 132 Mb/s, 1bit 4224 M samples/s sub-sampling, low-complexity and energy-efficient BPSK transceiver for all-digital 3–5 GHz IR-UWB," *Analog Integrated Circuits and Signal Processing*, vol. 75, no. 3, pp. 467–482, Jun 2013.

- [76] X. Wang, B. Qin, H. Xie, L. Lin, H. Tang, Q. Fang, H. Zhao, A. Wang, H. Chen, B. Zhao, Y. Zhou, L. Yang, and G. Zhang, "FCC-EIRP-aware UWB pulse generator design approach," in *Proc. IEEE International Conference on Ultra-Wideband*, Sep 2009, pp. 592–596.

- [77] X. Wang, S. Fan, H. Tang, L. Lin, J. Liu, Q. Fang, H. Zhao, A. Wang, L.-W. Yang, and B. Zhao, "A whole-chip ESD-protected 0.14-pJ/p-mV 3.1–10.6-GHz impulse-radio UWB transmitter in 0.18-μm CMOS," *IEEE Transactions on Microwave Theory and Techniques*, vol. 59, no. 4, pp. 1109–1116, Apr 2011.

- [78] H. Hie, X. Wang, A. Wang, B. Zhao, Y. Zhou, B. Qin, H. Chen, and Z. Wang, "A varying pulse width 5th-derivative Gaussian pulse generator for UWB transceivers in CMOS," in *Proc. IEEE Radio and Wireless Symposium*, Jan 2008, pp. 171–174.

- [79] H. Hedayati and K. Entesari, "A 3.1–10.6 GHz ultra wide-band impulse radio transmitter with notch implementation for in-band interferers in 90nm CMOS," in *Proc. IEEE Radio Frequency Integrated Circuits Symposium*, Jun 2012, pp. 459–462.

- [80] E. Vittoz, Low-Power Crystal and MEMS Oscillators: The Experience of Watch Developments. Dordrecht: Springer, 2010.

- [81] D. Aebischer, H. Oguey, and V. von Kaenel, "A 2.1 MHz crystal oscillator time base with a current consumption under 500 nA," *IEEE Journal Solid-State Circuits*, vol. 32, no. 7, pp. 999–1005, Jul 1997.

- [82] A. Niknejad, EE242 Lecture Notes, University of California, Berkeley, spring 2007.

- [83] Maxim Integrated Products Inc., "Specifying quartz crystals," released 19 Nov 2001, retrieved 21 Jun 2012.

- [84] R. C. Ruby, P. Bradley, Y. Oshmyansky, A. Chien, and J. D. Larson, "Thin film bulk wave acoustic resonators (FBAR) for wireless applications," in *Proc. IEEE Ultrasonics Symposium*, Oct 2001, pp. 813–821.

- [85] Y. H. Chee, *Ultra Low Power Transmitters for Wireless Sensor Networks*. Ph.D. Dissertation, University of California, Berkeley, 2006.

- [86] SiTime, SiT5000 Datasheet Rev. 0.91, Jun 2012.

- [87] Silicon Labs, Si500S Datasheet Rev. 1.1 10/11, 2011.

- [88] M. Steyaert, A. van Roermund, and A. Baschirotto, *Analog Circuit Design: Low Voltage Low Power; Short Range Wireless Front-Ends; Power Management and DC-DC.* Dordrecht: Springer, 2011.

- [89] K. Sundaresan, P. E. Allen, and F. Ayazi, "Process and temperature compensation in a 7-MHz CMOS clock oscillator," *IEEE Journals of Solid-State Circuits*, vol. 41, no. 2, pp. 433–442, Feb 2006.

- [90] N. Cho, S.-J. Song, S. Kim, S. Kim, and H.-J. Yoo, "A 5.1-μW UHF RFID tag chip integrated with sensors for wireless environmental monitoring," in *Proc. IEEE European Solid-State Circuits Conference*, Sep 2005, pp. 279–282.

- [91] X. Zhang and A. B. Apsel, "A low-power, process- and temperature-compensated ring oscillator with addition-based current source," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 58, no. 5, pp. 868–878, May 2011.

- [92] V. Pillai, H. Heinrich, D. Dieska, P. V. Nikitin, R. Martinez, and K. V. S. Rao, "An ultra-low-power long range battery/passive RFID tag for UHF and microwave bands with a current consumption of 700 nA at 1.5 V," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 54, no. 7, pp. 1500–1512, Jul 2007.

- [93] C.-F. Chan, K.-P. Pun, K.-N. Leung, J. Guo, L.-K. L. Leung, and C.-S. Choy, "A low-power continuously-calibrated clock recovery circuit for UHF RFID EPC class-1 generation-2 transponders," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 3, pp. 587–599, Mar 2010.

- [94] EPCglobal Inc.,  $EPC^{TM}$  Radio-Frequency Identity Protocols Class-1 Generation-2 UHF RFID Protocol for Communications at 860 MHz-960 MHz Version 1.2.0, 23 Oct 2008.

- [95] L.-K. L. Leung and H. C. Luong, "A 7-μW clock generator in 0.18-μm for passive UHF RFID EPC g2 tags," in *Proc. IEEE European Solid State Circuits Conference*, Sep 2007, pp. 412–415.

- [96] L. Xia, J. Cheng, N. E. Glover, and P. Chiang, "0.56 V, -20 dBm RF-powered, multi-node wireless body area network system-on-a-chip with harvesting-efficiency tracking loop," *IEEE Journal of Solid-State Circuits*, vol. 49, no. 6, pp. 1345–1355, Jun 2014.

- [97] J. Bae, K. Song, H. Lee, H. Cho, and H.-J. Yoo, "A low-energy crystal-less double-FSK sensor node transceiver for wireless body-area network," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 11, pp. 2678–2692, Nov 2012.

- [98] J. Mao, Z. Zou, and L.-R. Zheng, "A subgigahertz UWB transmitter with wireless clock harvesting for RF-powered applications," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 61, no. 5, pp. 314–318, May 2014.

- [99] K. Yamamoto and M. Fujishima, "A 44- $\mu$ W 4.3-GHz injection-locked frequency divider with 2.3-GHz locking range," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 3, pp. 671–677, Mar 2005.

- [100] M. H. Ghaed, G. Chen, R.-U. Haque, M. Wieckowski, Y. Kim, G. Kim, Y. Lee, I. Lee, D. Fick, D. Kim, M. Seok, K. D. Wise, D. Blaauw, and D. Sylvester, "Circuits for a cubic-millimeter energy-autonomous wireless intraocular pressure monitor," *IEEE Transactions Circuits and Systems I: Regular Papers*, vol. 60, no. 12, pp. 3152–3162, Dec 2013.

- [101] Y. Osaki, T. Hirose, N. Kuroki, and M. Numa, "1.2-V supply, 100-nW, 1.09-V bandgap and 0.7-V supply, 52.5-nW, 0.55-V subbandgap reference circuits for nanowatt CMOS LSIs," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 6, pp. 1530–1538, Jun 2013.

- [102] T. Hirose, K. Ueno, N. Kuroki, and M. Numa, "A CMOS bandgap and sub-bandgap voltage reference circuits for nanowatt power LSIs," in *Proc. IEEE Asian Solid-State Circuits Conference*, Nov 2010, pp. 77–80.

- [103] G. D. Vita and G. Iannaccone, "A sub-1-V, 10 ppm/°C, nanopower voltage reference generator," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 7, pp. 1536–1542, May 2009.