Master's thesis

Halfdan Solberg Bechmann

May 2014

Voltage Floating Gate Design

### **Abstract**

This thesis covers the design, production and measurement of digital ultra-low voltage floating gate logic.

The increasing demand for low-power electronics, fueled by the expanding market for portable devices and the growth of the Internet of things, both with a desire for longer battery life, enhances the importance of low-power logic styles in modern integrated circuit design. This leads to a rising demand for low-voltage design topologies because the simplest way to reduce both the static and dynamic power consumption is to reduce the supply voltage. The cost of this however is a severe penalty to the circuit speed.

The ultra-low voltage (ULV) logic styles used in this thesis are designed to reduce gate delay and increase the circuit speed by utilizing capacitive coupling on the inputs to super-charge the gate terminal of critical transistors and thereby increase transistor current. The presented designs, simulations and measurements of the ULV logic prove the topology to be significantly faster than conventional electronics in ultra-low voltage operation.

To demonstrate the high-speed qualities of ULV logic in hardware and compare its analog properties to conventional logic, a test circuit with an inverter from each topology is designed and manufactured. The ULV inverter used is from the 7<sup>th</sup> iteration ULV topology (ULV7) and is scaled to drive the capacitive load of a test setup. The conventional inverter is scaled equivalently and placed on the same chip. After production in Taiwan by TSMC using their 90nm Nexsys<sup>®</sup> process the finished chip produces measurements that show that the theorized and simulated qualities of ULV logic are highly applicable in silicon hardware implementations.

The low propagation delay of the ULV logic makes it ideal for use in adder carry circuits. To utilize the ULV properties, new carry circuits are presented and simulated in this thesis, yielding results that prove them more energy efficient and significantly faster than conventional carry propagation circuits.

# **Preface**

This thesis is a part of the degree Master of Science in Nano- and microelectronics carried out at the Department of Informatics, Faculty of Mathematics and Natural Sciences at the University of Oslo. It contributes 60 credits to the degree.

### **Acronyms**

$V_{GS}$  Transistor Gate-Source Voltage  $V_{TH}$  Transistor Threshold Voltage

'0' Logical zero, voltage close to GND'1' Logical one, voltage close to VDD

'Z' Logical high-impedance

ALU Arithmetic Logic Unit

ASIC Application-Specific Integrated Circuit

CC Chip Carrier

Cin Carry input

CLK Clock

CMOS Complementary Metal-Oxide-Semiconductor

Cout Carry **out**put

CPA Carry Propagate Adder

CSA Carry Save Adder

DIBL Drain Induced Barrier Lowering

DRC Design Rule Checker

EAGLE PCB design tool (Easily Applicable Graphical Layout Editor)

EDP Energy-Delay Product

FBB Forward Bulk Bias

FG Floating Gate

GND Ground

GPIB General Purpose Interface Bus

Idsn Drain-Source current of NMOS transistor

IMEC Interuniversity Microelectronics Centre

Isdp Source-Drain current of PMOS transistor

JLCC J-Leaded Chip Carrier (ceramic)

$\begin{array}{ll} L_n & \quad \textbf{Length of NMOS transistor} \\ L_p & \quad \textbf{Length of PMOS transistor} \\ LVS & \quad \textbf{Layout Versus Schematic} \end{array}$

MIMCAP Metal-Insulator-Metal Capacitor

MOMCAP Metal-Oxide-Metal Capacitor

MOSCAP MOSFET without source and drain connections, used as a capacitor.

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MUX **Multiplexer**

nch\_lvt tsmcN90rf **n-ch**annel transistor with a low threshold voltage

nch\_mac tsmcN90rf **n-ch**annel transistor, Monte Carlo enabled

NMOS N-type MOSFET, MOSFET with negative charge carriers (electrons),

PCB Printed Circuit Board

PDP Power-Delay Product

PLCC Plastic Leaded Chip Carrier

PMOS P-type MOSFET, MOSFET with positive charge carriers (holes)

PTL Pass Transistor Logic

RBB Reverse Bulk Bias

RSCE Reverse Short-Channel Effect

RTMOM Rotative Metal-Oxide-Metal (capacitor type)

RTMOMCAP RTMOM Capacitor

SMD Surface-Mount Device

SMT Surface-Mount Technology

TG Transmission Gate

TSMC Taiwan Semiconductor Manufacturing Company

tsmcN90rf TSMC 90 nanometer high-frequency production process, also called Nexsys®

ULV Ultra-Low-Voltage

ULVPTL Ultra-Low-Voltage Pass-Transistor Logic

UV Ultraviolet

Vdd Supply Voltage for MOSFET circuits (Voltage **D**rain **D**rain)

$W_n$  Width of NMOS transistor  $W_p$  Width of PMOS transistor

m  $\times 10^{-3}$

$\mu$   $\times 10^{-6}$

$n \hspace{1.5cm} \times 10^{-9}$

p  $\times 10^{-12}$

f  $\times 10^{-15}$

a  $\times 10^{-18}$

$z \times 10^{-21}$

y  $\times 10^{-24}$

# **Contents**

| A  | bstract |                                                    | III  |

|----|---------|----------------------------------------------------|------|

| Pı | reface  |                                                    | V    |

| A  | cronyms |                                                    | VII  |

| Fi | gures   |                                                    | XI   |

| Ta | ables   |                                                    | XIII |

| 1  | Introdu | ction                                              | 1    |

|    |         | esis outline                                       |      |

| 2  |         | ound                                               |      |

|    | · ·     | ating Gate Logic                                   |      |

|    |         | ders                                               |      |

|    |         | p-Threshold Effects                                |      |

|    | 2.3.1   | Reverse narrow- and short-channel effects          | 7    |

|    | 2.3.2   | Body effect                                        | 9    |

|    | 2.3.3   | Subthreshold scaling summary                       | 11   |

|    | 2.4 Fig | ures of merit                                      | 12   |

|    | 2.4.1   | Propagation Delay                                  | 12   |

|    | 2.4.2   | Power                                              | 14   |

|    | 2.4.3   | Power-Delay Product                                | 15   |

|    | 2.4.4   | Energy-Delay Product                               | 16   |

|    | 2.4.5   | Standard deviation $(\sigma)$                      | 17   |

| 3  | Design  |                                                    | 18   |

|    | 3.1 Imp | blementation of an Ultra-Low-Voltage Inverter      | 18   |

|    | 3.1.1   | Intro                                              | 18   |

|    | 3.1.2   | 7 <sup>th</sup> Generation Ultra-Low Voltage Logic | 18   |

|    | 3.1.3   | Design Considerations                              | 20   |

|    | 3.1.4   | Simulations                                        | 27   |

|    | 3.1.5   | Final chip                                         | 29   |

|    | 3.1.6   | Circuit Board                                      | 30   |

|    | 3.1.7   | Test setup                                         | 32   |

|    | 3.1.8   | Measurements                                       |      |

|    | 3.1.9   | Conclusion                                         |      |

|    |         | V Static Carry Generate Circuit                    |      |

|    | 2 2 1   | Darformanca                                        | 11   |

|   | 3.3           | Capacitive Prec | charge NP domino carry                              | 45 |

|---|---------------|-----------------|-----------------------------------------------------|----|

|   | 3.4           | Ultra-Low Volt  | age Pass Transistor Logic                           | 49 |

|   | 3.4.          | 1 Single pass   | s transistors                                       | 49 |

|   | 3.4.          | 2 Ultra-Low     | Voltage Pass Transistor Multiplexer                 | 52 |

|   | 3.4.          | 3 Ultra-Low     | Voltage Pass Transistor Carry Gate                  | 55 |

| 4 | Cor           | clusion         |                                                     | 62 |

|   | 4.1           | Further Work    |                                                     | 62 |

| 5 | Bib           | liography       |                                                     | 63 |

| 6 | App           | endix           |                                                     | 65 |

|   | 6.1<br>Invert | -               | n of an Ultra-Low Voltage Robust Low-Power Static C |    |

|   | 6.2           | Scripts         |                                                     | 71 |

|   | 6.2.          | 1 Measurem      | ent setup                                           | 71 |

|   | 6.2.          | 2 Reading ar    | nd plotting data                                    | 76 |

|   |               |                 |                                                     |    |

# **Figures**

| Figure 2.1.1: Schematic: Floating gate (FG) on an NMOS transistor.                                | 2    |

|---------------------------------------------------------------------------------------------------|------|

| Figure 2.1.2: Schematic: Floating gate with recharge transistor ( <i>Rp</i> )                     | 3    |

| Figure 2.1.3: Floating gate in precharge mode                                                     | 3    |

| Figure 2.1.4: Floating gate in evaluation mode.                                                   | 3    |

| Figure 2.1.5: Schematic: Basic ULV floating gate inverter.                                        | 3    |

| Figure 2.2.1: 3-Bit CPA                                                                           |      |

| Figure 2.3.1: Simulation: Drive strength of near minimum size transistors at 200mV                | 7    |

| Figure 2.3.2:Simulation: Drive strength of near minimum size transistors at 1.2V                  | 8    |

| Figure 2.3.3: Simulation: Transistor strength for varying body bias (Vdd = 200mV)                 | 9    |

| Figure 2.3.4: Deep n-well illustration.                                                           | .10  |

| Figure 2.4.1: Standard CMOS carry circuit.                                                        |      |

| Figure 2.4.2: Simulation: Carry propagation through a standard CMOS carry chain at 1.2V           | .13  |

| Figure 2.4.3: Delay per bit of a standard CMOS inverter.                                          |      |

| Figure 2.4.4: Simulation: Power consumption of a standard CMOS carry circuit.                     | . 14 |

| Figure 2.4.5: Illustration of PDP.                                                                |      |

| Figure 2.4.6: Simulation: PDP of a standard CMOS carry circuit                                    |      |

| Figure 2.4.7: Simulation: EDP of a standard CMOS carry circuit.                                   |      |

| Figure 2.4.8: Standard deviation diagram.                                                         |      |

| Figure 3.1.1: Schematic: ULV7 N-type inverter.                                                    |      |

| Figure 3.1.2: Schematic: ULV7 P-type inverter.                                                    |      |

| Figure 3.1.3: High-Speed Layout.                                                                  |      |

| Figure 3.1.4: High-Yield Layout                                                                   |      |

| Figure 3.1.5: Conventional CMOS inverter.                                                         |      |

| Figure 3.1.6: Implemented ULV7 inverter.                                                          |      |

| Figure 3.1.7: Traditional CMOS inverter layout.                                                   |      |

| Figure 3.1.8: ULV7 inverter layout                                                                |      |

| Figure 3.1.9: Full Layout.                                                                        |      |

| Figure 3.1.10: Layout overview                                                                    |      |

| Figure 3.1.11: Simulation of schematics and layout of the conventional CMOS inverter              |      |

| Figure 3.1.12: Simulation of schematics and layout of the ULV7 inverter.                          | .28  |

| Figure 3.1.13: Simulation: Sweep of Vdd on the CMOS inverter layout, compared to the              | .28  |

|                                                                                                   |      |

| Figure 3.1.14: Final chip bonded in JLCC84 package.                                               |      |

| Figure 3.1.15: Die close-up, the capacitor and M9 Vdd paths are visible in the red square         |      |

| Figure 3.1.16: PCB: Top electric layer.                                                           |      |

| Figure 3.1.17: PCB: Bottom electric layer.                                                        |      |

| Figure 3.1.18: PCB: Top paste, silk and via layers.  Figure 3.1.19: Top side of the finished PCB. |      |

| Figure 3.1.20: Bottom side of the finished PCB.                                                   |      |

| Figure 3.1.21: Soldered PCB with chip carrier mounted.                                            |      |

| Figure 3.1.22: Test setup                                                                         |      |

| Figure 3.1.23: ULV7 inverter, schematic simulation, layout simulation and measured results        |      |

| Figure 3.1.24: Schematic and layout simulation, and measured results of the conventional          |      |

| CMOS inverter.                                                                                    | 33   |

| Figure 3.1.25: Schematic: N-type ULV7 inverter.                                                   |      |

| Figure 3.1.26: Schematic: Implemented N-type ULV7 inverter.                                       |      |

| Figure 3.1.27: Measured: ULV7 output (170mV offset on CLK at 300mV and 400kHz)                    |      |

| rigure 3.1.27. micabarea. Olivi output (170m v ombet on elix at 300m v and 400km2)                |      |

| Figure 3.1.28: Measured: ULV7 output (150mV offset on CLK at 200mV and 40kHz)            | 35 |

|------------------------------------------------------------------------------------------|----|

| Figure 3.1.29: Measured: Transient response of the inverters at 200mV.                   | 36 |

| Figure 3.1.30: Delay of traditional logic and ULV7 with CLK offset                       | 37 |

| Figure 3.1.31: Delay of ULV7 inverter relative to a traditional inverter                 | 37 |

| Figure 3.1.32: Measured: Delay of ULV7 inverter relative to conventional CMOS (no offset | t  |

| applied)                                                                                 | 38 |

| Figure 3.1.33: Transient measurements at 50mV.                                           |    |

| Figure 3.1.34: Standard deviation of the two inverters.                                  | 39 |

| Figure 3.1.35: Measured: $\sigma$ of ULV7 relative $\sigma$ of traditional CMOS          | 40 |

| Figure 3.2.1: Schematic: ULV Static carry generate circuit [15]                          | 41 |

| Figure 3.2.2: Schematic: Series connection of SULVC circuits                             | 42 |

| Figure 3.2.3: Simulation: SULVC propagating '1'.                                         | 43 |

| Figure 3.2.4: Simulation: SULVC propagating '0'.                                         | 43 |

| Figure 3.3.1: Schematic: ULV5 carry N-type circuit.                                      | 45 |

| Figure 3.3.2: Schematic: ULV5 carry P-type circuit.                                      | 45 |

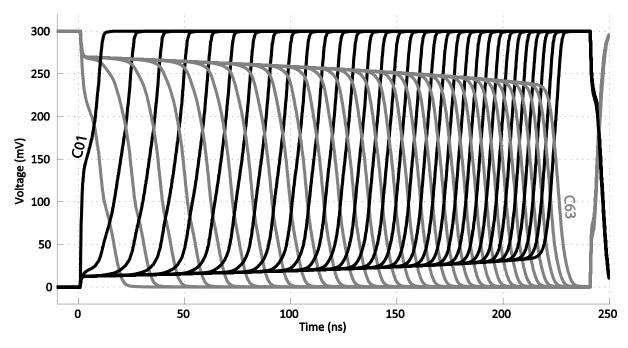

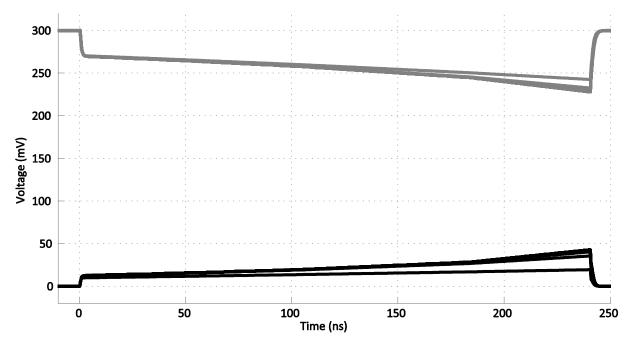

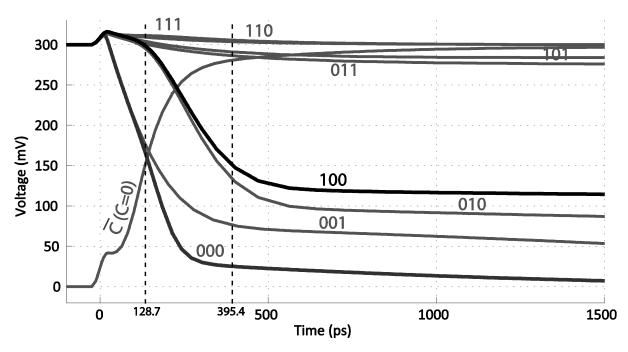

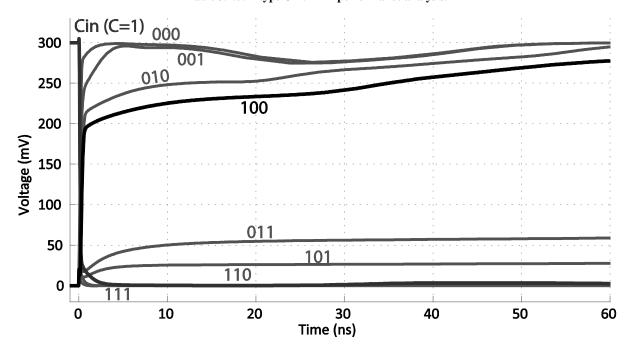

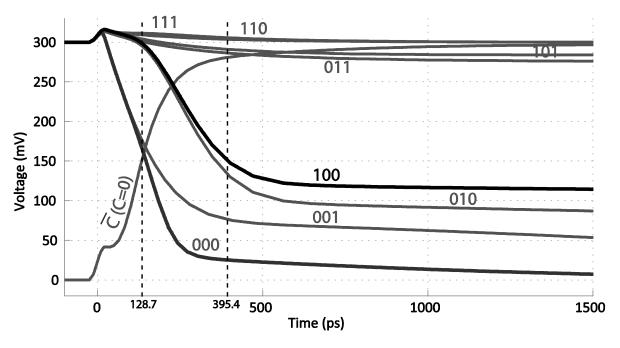

| Figure 3.3.3: Simulation: 64 bit ULV5 n-p domino carry chain, propagating '0'            | 46 |

| Figure 3.3.4: Simulation: 64 bit ULV5 n-p domino carry chain, "propagating" '1'          | 47 |

| Figure 3.4.1: NMOS as PTL gate.                                                          | 49 |

| Figure 3.4.2: PMOS as PTL gate.                                                          | 49 |

| Figure 3.4.3: Schematic: ULV N-type pass transistor                                      | 49 |

| Figure 3.4.4: Schematic: ULV P-type pass transistor                                      | 49 |

| Figure 3.4.5: Simple n- and p-type ULV pass transistors, falling A (Ideal inputs)        | 50 |

| Figure 3.4.6: Simple n- and p-type ULV pass transistors, rising A (Ideal inputs)         | 51 |

| Figure 3.4.7: Schematic: PTL Transmission Gate                                           | 51 |

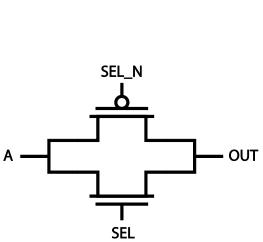

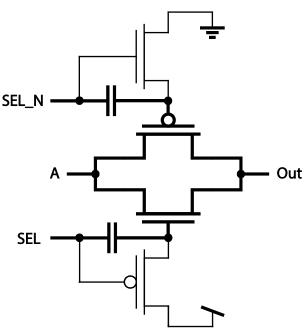

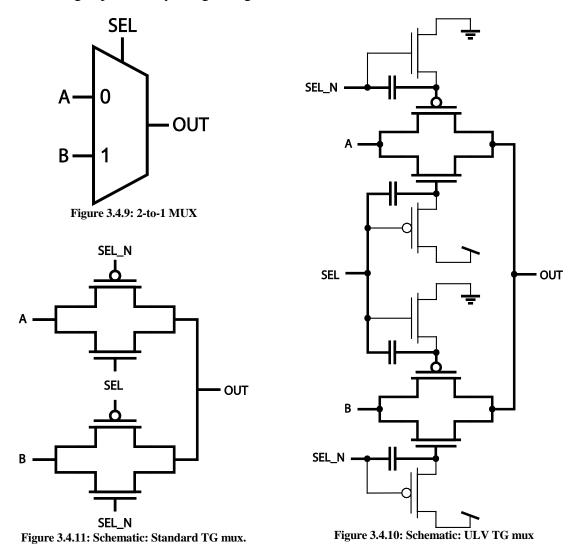

| Figure 3.4.8: Schematic: ULV PTL Transmission Gate                                       | 51 |

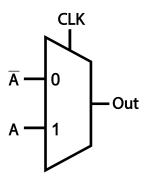

| Figure 3.4.9: 2-to-1 MUX                                                                 | 52 |

| Figure 3.4.10: Schematic: ULV TG mux                                                     |    |

| Figure 3.4.11: Schematic: Standard TG mux.                                               | 52 |

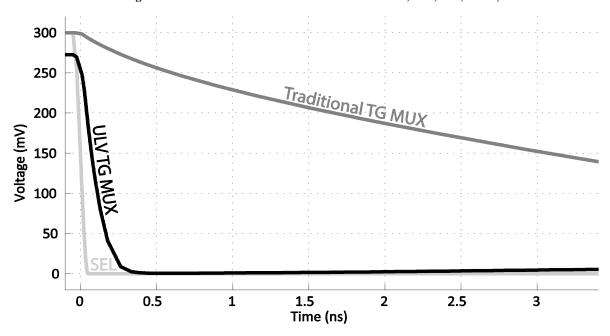

| Figure 3.4.12: Simulation: Standard and ULV TG MUX; A=0, B=1, SEL= ↑                     | 53 |

| Figure 3.4.13: Simulation: Standard and ULV TG MUX; A=0, B=1, SEL= ↓                     | 53 |

| Figure 3.4.14: MUX based level-to-edge converter.                                        |    |

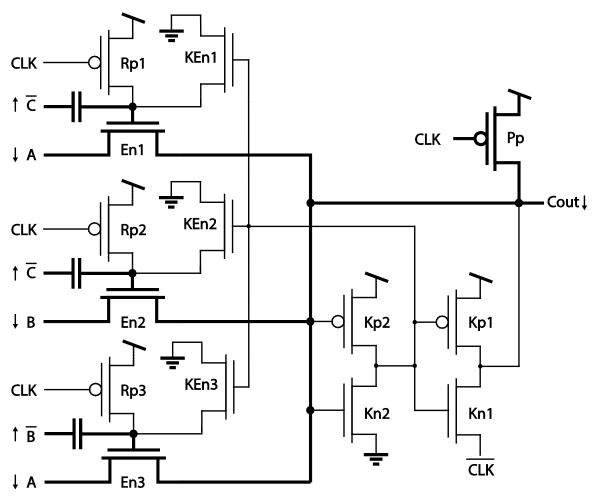

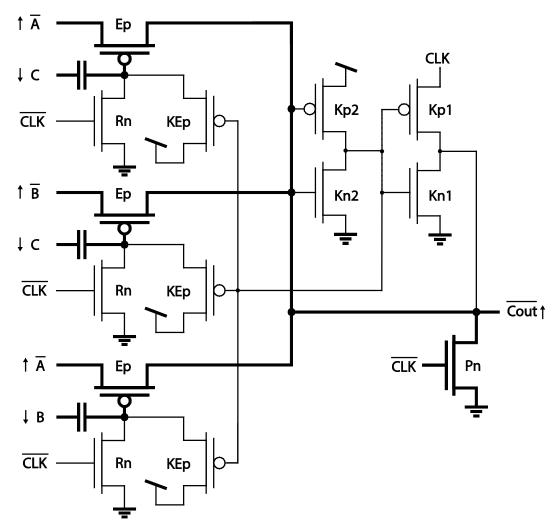

| Figure 3.4.15: Schematic: N-type ULV PTL Carry circuit.                                  |    |

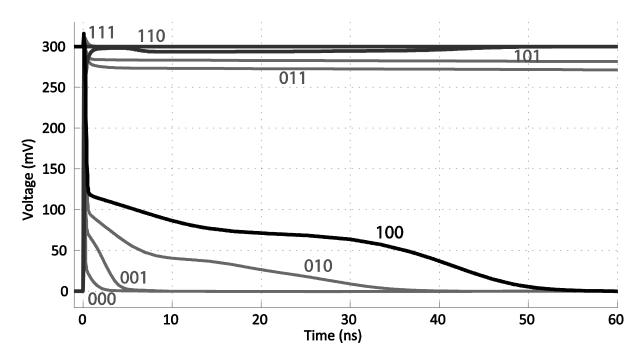

| Figure 3.4.16: Transient evaluation phase simulation of the N-type ULV PTL carry circuit |    |

| Figure 3.4.17: Close-up of the beginning of the evaluation phase from Figure 3.4.16      |    |

| Figure 3.4.18: Schematic: P-type ULV PTL carry.                                          |    |

| Figure 3.4.19: Transient evaluation phase simulation of the P-type ULV PTL carry circuit |    |

| Figure 3.4.20: Close-up of the beginning of the evaluation phase from Figure 3.4.19      |    |

# **Tables**

| Table 2.2.1: Full-adder truth table                                                  | 5           |

|--------------------------------------------------------------------------------------|-------------|

| Table 2.3.1: Simulation: Effect of sub-threshold scaling on transistor drive strengt | h at 200mV. |

|                                                                                      | 11          |

| Table 2.4.1: Conventional CMOS Carry Propagation Delay.                              | 13          |

| Table 2.4.2: Conventional CMOS Carry Power Consumption                               | 14          |

| Table 2.4.3: Conventional CMOS Carry PDP.                                            | 15          |

| Table 2.4.4: Conventional CMOS Carry EDP.                                            | 16          |

| Table 3.1.1: Signal phases of the ULV7 inverter.                                     | 19          |

| Table 3.1.2: Chip transistor sizing.                                                 | 23          |

| Table 3.1.3: RTMOM Capacitor details                                                 | 24          |

| Table 3.1.4: Comparison of the ULV7 and conventional inverter.                       | 40          |

| Table 3.2.1: Truth table for the parallel part of the ULVSC                          | 41          |

| Table 3.2.2: Comparison chart for SULVC.                                             | 44          |

| Table 3.3.1: Precharge NP domino capacitive divider carry logic                      | 46          |

| Table 3.3.2: CPULVC performance analysis                                             | 47          |

| Table 3.4.1: Truth table for a single PTL gate.                                      | 49          |

| Table 3.4.2: Propagation delay for minimum sized PTL and ULVPTL (V                   | /dd=300mV,  |

| Load=1fF)                                                                            | 51          |

| Table 3.4.3: MUX propagation delay at 300mV, (A=0, B=1)                              | 53          |

| Table 3.4.4: Truth table and generated signals for the N-type ULV PTL Carry          | 56          |

| Table 3.4.5: ULV PTL N-type carry performance analysis.                              | 58          |

| Table 3.4.6: P-type ULV PTL performance analysis                                     | 60          |

| Table 3.4.7: ULV PTL P-type carry performance analysis.                              | 61          |

### 1 Introduction

The expanding market for portable devices and the rapid growth of the internet of things creates an increasing demand for electronics powered by lightweight batteries and alternative energy sources. This leads to higher low-power data processing requirements increasing the importance of low-power logic styles in modern integrated circuit (IC) design. The simplest way to reduce the power consumption of a system is to reduce the supply voltage which drastically reduces both the static and dynamic power dissipation at the cost of a higher gate delay and a slower circuit. The increasing use of energy harvesting systems to power lightweight devices also introduces a demand for circuits that are not only low-power but also need to run on an low supply voltage in order to avoid the power overhead of dc-dc converters. The continuous reduction of transistor sizes also causes increased leakage through subthreshold currents and gate-oxide tunneling [1] that can only be reduced by lowering the supply voltage.

To increase the speed while maintaining a low supply voltage, a floating gate logic style can be utilized to increase the transistor current and device speed by super charging the gate of the evaluation transistor but still maintain the low supply voltage needed to tackle sub-threshold leakage and keep the power consumption low.

#### 1.1 Thesis outline

The focus of this thesis will be on the design of the type of ultra-low voltage (ULV) floating gate logic mentioned above.

In the next chapter, the thesis will start off by explaining the theoretical background for the work conducted. This includes Floating Gate Logic, Adders, Sub-Threshold Effects and the Figures of merit used to analyze the circuits.

The thesis will then continue to the design of a test circuit to compare the ULV logic style to conventional logic in implemented hardware and see the correlation with simulation results. A layout of this design is made in section 3.1.3 and produced by Taiwan Semiconductor Manufacturing Company (TSMC) using their 90nm Nexsys® process. A Printed Circuit Board (PCB) is also made, this in section 3.1.6 to allow for chip measurements in section 3.1.8.

The thesis also contains design and simulations of circuits implemented in ULV logic. This includes simulations of a ULV static carry generate circuit from [2], design and simulations of a new carry topology based on ULV5 logic and the design and simulation of a multiplexer and a new carry circuit based on ULV PTL logic [3].

## 2 Background

In this chapter, an introduction to the concepts needed in the design of ultra-low-voltage electronics will be given. The first concept explained is floating gate logic. The idea of a floating, or a semi-floating gate is the cornerstone of the ULV logic styles, and what makes this logic especially fast at low voltages. Because of these high-speed properties, the ULV logic styles are ideal for serial circuits with a high logic depth enabling more complex operations in the same clock period. One example of this circuit type is the adder, which is the next concept explained and it is a circuit where a moderately complex operation needs to be done on one bit after another in a serial manner making the total processing time directly proportional to the gate delay and the number of bits and the circuit.

The third section will focus on the effects of lowering the supply voltage below the transistor threshold voltage. These effects will be simulated to get an understanding of their effect on the devices from the production process used in this thesis.

To compare the new circuits to each other and to conventional electronics, some figures of merit are necessary. The figures of merit used will be explained in the last section of this chapter.

### 2.1 Floating Gate Logic

The idea of a floating gate is the cornerstone of the ULV logic styles and is the main reason for its high speed in low-voltage operation.

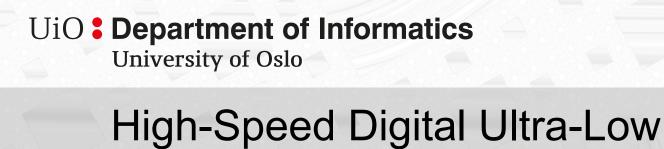

Floating gate logic is a logic style that uses a capacitor on the gate of an evaluation transistor. An illustration of this is shown in the figure below.

Figure 2.1.1: Schematic: Floating gate (FG) on an NMOS transistor.

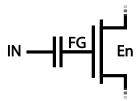

The floating gate capacitor makes the input isolated from the DC voltage level on the gate of the transistor and allows the designer to set the operating point for the transistor while keeping most of the input voltage swing. The amplitude of this swing depends on the input capacitor size relative to parasitic capacitances like gate-source and gate-drain capacitance. Experiments with setting the floating gate operation point using UV light have been successfully executed in [4] (FGUVMOS) using a  $0.8\mu m$  production process, but in newer processes with smaller transistors like the 90nm process used in this thesis, the gate leakage is too large to keep the charge on the floating gate for the entire circuit lifetime. To overcome this leakage problem and to avoid the postproduction UV light procedure, a transistor that charges the floating gate to a predefined value can be added as shown in Figure 2.1.2. This transistor is called a recharge transistor (Rp).

Figure 2.1.2: Schematic: Floating gate with recharge transistor (Rp).

This new *Rp* transistor introduces a clocked element to the circuit, making it synchronous and introducing a precharge phase in the circuit operation. This circuit will have a precharge phase when the *CLK* signal is '0' turning the precharge transistor *Rp* on and setting the floating gate to *Voffset*+ as shown in Figure 2.1.3. When *CLK* switches to '1' the circuit enters the evaluation phase and the *Rp* transistor is off as shown in Figure 2.1.4 resulting in a floating gate on the *En* transistor with an operation point set by *Voffset*+.

Figure 2.1.3: Floating gate in precharge mode.

Figure 2.1.4: Floating gate in evaluation mode.

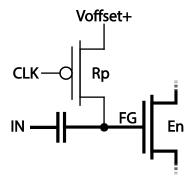

One of the simplest ways to utilize the floating gate concept is demonstrated in the Ultra-Low-voltage logic style (ULV) as shown in Figure 2.1.5 and presented in [5].

Figure 2.1.5: Schematic: Basic ULV floating gate inverter.

The ULV inverter exploits the capacitive coupling between the input and the floating gate to achieve a gate voltage that is higher than the circuit supply voltage resulting in a significantly higher current, especially at low voltages due to the drain-source currents exponential dependence on the gate-source voltage in ultra-low-voltage operation. A higher output current will charge the load and parasitic capacitances faster and result in a smaller propagation delay and a faster circuit.

#### 2.2 Adders

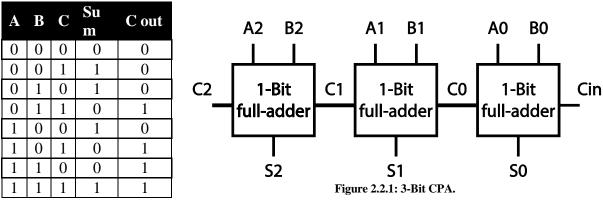

An adder, in this context, is a circuit that adds two binary numbers. The basic building block of an adder is the 1-bit full-adder which is a circuit that adds two bits and a carry input to produce a sum and an output carry according to the truth table in Table 2.2.1.

Table 2.2.1: Full-adder truth table.

From this building block we can create two types of adders, Carry Save adders (CSA) and Carry Propagate adders (CPA), which can be implemented in a number of ways using different optimization algorithms like in [6] and [7].

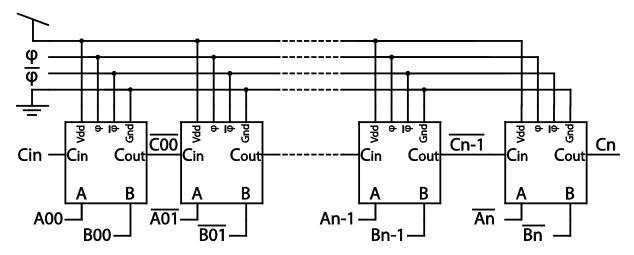

A CPA can be created by placing a number of full-adders in a series configuration with the carry input connected to carry output of the previous circuit as shown in Figure 2.2.1. In a CPA circuit the most important parameter is the carry propagation delay  $(t_P)$  because the carry signal needs to propagate through all the full-adders in the chain resulting in a total time of  $t_P \cdot n$  for an n-bit adder to produce the correct result. Using an optimization algorithm like the Kogge-Stone [7] reduces the total time to  $t_P \cdot log_2 n$  but it is still proportional to the propagation delay.

A CSA is essentially an array of full-adders in parallel; it receives three n-bit numbers and produces two n-bit arrays, one is the output carry and one is the sum. The CSA uses a total time of  $t_P$  independant of the number of bits due to its high level of parallelism.

When adding many operands a CSA is often used in a tree structure to reduce the number of operands. In a Wallace-tree configuration [8] for example, an n-operand addition is reduced to a two operand addition in  $t_P \cdot log_2 n$  reduction layers with only a single gate delay per layer, reducing the total time to  $t_P \cdot log_2 n$  from  $t_P \cdot log^2 n$  using only CPAs. In the final step of any reduction tree, a CPA will always be needed to add the final array of carry bits to the sum. The final CPA will use one gate delay per bit and because the number of bits is usually larger than the number of operands, this is the most important part to optimize, making the CPA speed critical.

An arithmetic logic unit (ALU) can consist of multipliers, dividers, square root extractors, adders and other arithmetic logic. In most of these, a CPA is the bottleneck of the algorithm.

Multipliers, dividers and square root extractors all employ algorithms that depend on reduction trees to sum their partial products. Even though the number partial products can be reduced by using high-radix algorithms, the bottleneck will still be the CPA of the reduction tree which cannot be trimmed away with algorithmic changes. This shows the importance of high-speed CPA carry propagation.

#### 2.3 Sub-Threshold Effects

The ULV logic style operates at ultra-low voltages, which means that near-threshold and subthreshold transistor conditions apply. This makes the sub-threshold transistor effects necessary to consider in order to properly adjust the transistor strengths and to understand why the circuits are not behaving the same way as in higher voltage design.

In conventional CMOS design the transistors are considered to be "off" when the gate voltage  $(V_{GS})$  is below the threshold voltage  $(V_{TH})$ . This is because the sub-threshold, or "off"-current current, is insignificant in comparison to the "on"-current. When the supply voltage (Vdd) is lower than  $(V_{TH})$ , the subthreshold current dominates, resulting in equation 2.3.1 from [9].

$$I_{DS} = I_0 \frac{W}{L} e^{(V_{GS} - V_{TH})/n \cdot v_t} \left( 1 - e^{-V_{DS}/v_t} \right)$$

(2.3.1)

Where  $I_0$  is the technology-dependent sub-threshold current,  $v_t$  is the temperature dependent thermal voltage and n is the process dependent sub-threshold factor. The  $V_{TH}$  parameter is the transistor threshold voltage which is affected by both the drain-source voltage  $(V_{DS})$  through drain-induced barrier lowering (DIBL) [9] and the bulk-source voltage  $(V_{BS})$  through the body-effect as shown in equation 2.3.2 [10].

$$V_{TH} = V_{TH0} - \lambda_{DS} V_{DS} - \lambda_{BS} V_{BS} \tag{2.3.2}$$

Where  $\lambda_{DS}$  is the DIBL coefficient and  $\lambda_{BS}$  is the body-effect coefficient.

Drain induced barrier lowering (DIBL) is used to describe the effects of the drain voltage on the threshold voltage and transistor current [11]. The body effect is used to describe effect of the bulk biasing voltage on the transistor threshold voltage.

From equation 2.3.1 we can see that the transistor current is exponentially proportional to both the gate-source voltage and the threshold voltage, making the threshold voltage an effective parameter for tuning the transistor strength when  $V_{GS}$  is limited.

The effects of these threshold voltage tuning techniques in the 90nm process used in this thesis are explored in this section, first the reverse narrow- and short-channel effects, then the body biasing effects and a summary comparing and combining these techniques.

.

<sup>&</sup>lt;sup>1</sup> A difference is in the order of  $I_{on}/I_{off} > 10^4$

### 2.3.1 Reverse narrow- and short-channel effects

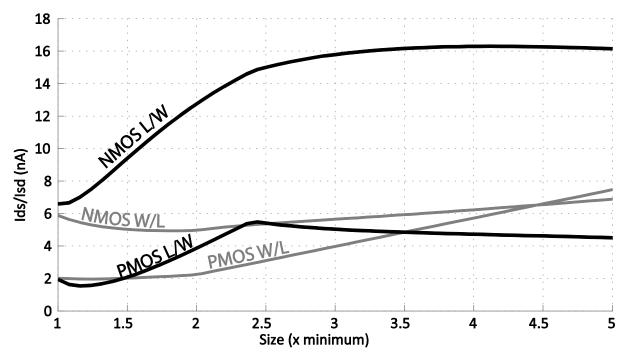

To explore the reverse narrow channel effect and the reverse short channel effect in the TSMC 90nm Nexsys<sup>®</sup> process, the current through an NMOS and a PMOS transistor is simulated for a range of transistor sizes and plotted as a function of minimum length and minimum width in Figure 2.3.1 for ULV operation, and in Figure 2.3.2 for traditional voltage level operation.

Figure 2.3.1: Simulation: Drive strength of near minimum size transistors at 200mV.

When transistors operate in the sub-threshold region the usual design rules based on above threshold operation shown in Figure 2.3.2 get less relevant. As shown in Figure 2.3.1 the transistor strength for small transistors will increase with the device length until it is about 4 times minimum for the NMOS transistor and 2.5 times for the PMOS transistor due to the reverse short channel effect [9]. This indicates that increasing the transistor length is a good way to increase the transistor drive strength. Increasing the transistor length can therefore be used to strengthen the pull-up- or pull-down-network of a circuit. The PMOS strength at 2.5x minimum length is close to matching the strength of a minimum sized NMOS transistor and shows that increasing the length of the PMOS can be used for e.g. balancing the rise- and fall-time of an inverter.

The transistor current is not necessarily translatable to circuit speed if the load capacitance of the circuit is also affected by the applied changes. Because the gate capacitance of the transistor is directly proportional to the length, strengthening the transistor by increasing the length leads to a parallel rise in gate capacitance. Increasing the speed of a system by increasing all transistor lengths is therefore only a viable solution if the gradient of the current as a function of length is larger than 1, meaning that the transistor strength increases more than the load capacitance. Figure 2.3.3 shows that the gradient of the simulated transistors is approximately 1. This means that increasing the transistor length is only beneficial for circuits where not all transistors need to be strengthened to reduce the worst case delay and for circuits where the affected transistor gate parasitics are not the dominating the input and/or output capacitances.

Figure 2.3.2: Simulation: Drive strength of near minimum size transistors at 1.2V.

Changing the transistor width proves less useful than in above-threshold design and even reduces the transistor strength for small  $\frac{W}{L}$  -values. This is caused by the reverse narrow channel effect [9] and shows that increasing the transistor width can be counter productive and is an ineffective way to increase drive strength compared to increasing the length for small transistors.

### 2.3.2 Body effect

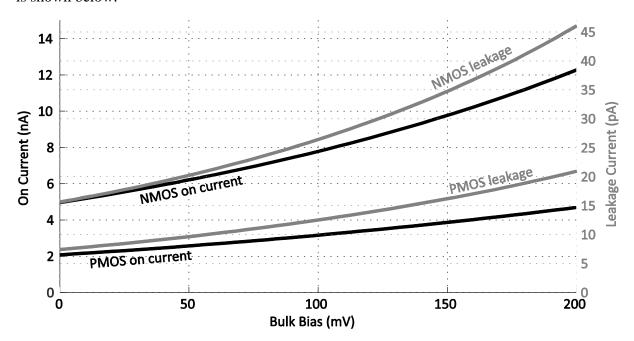

The body effect is a reduction of the effective threshold voltage that occurs when the body of the transistor is not biased with the same voltage level as the source terminal. In above-threshold design a reverse bulk bias (RBB) is always applied, mainly to avoid latchup generating a bipolar junction transistor and frying the circuit, but also because of leakage and area penalties.

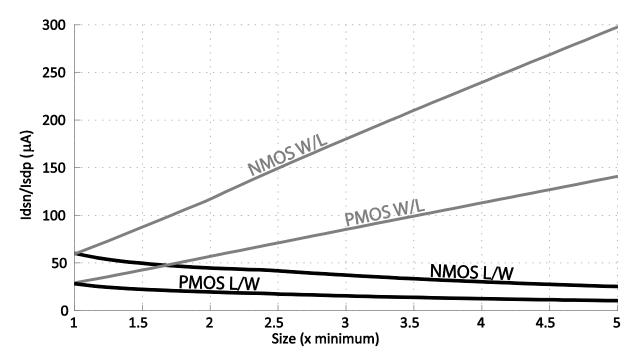

When the supply voltage is lower than the diode drop<sup>1</sup> a forward body bias can be applied without causing latchup. The effect of the body biasing voltage ( $V_{BS}$ ) on the threshold voltage ( $V_{TH}$ ) can be seen in equation 2.3.2 on page 6 and the effect on the resulting transistor strength is shown below.

Figure 2.3.3: Simulation: Transistor strength for varying body bias (Vdd = 200mV).

Figure 2.3.3 shows the increased current caused by a higher body bias voltage for the nch\_mac and pch\_mac transistors in the TSMCN90RF process library at 200mV. Both the NMOS and the PMOS is 2.4 times stronger with a forward body bias (FBB) than with a reverse body bias applied.

The simulation results also show that the relative increase of leakage current is larger than the relative increase of the on-current when forward biasing the circuit. The leakage current through the NMOS transistor is 3 times higher with FBB applied than with RBB applied, meaning that the relative increase of the leakage current is 23% higher than the relative increase of on-current. For the PMOS transistor the relative leakage increase is in the same range with 20%. This results in a 20% lower  $I_{on}/I_{off}$  ratio when forward biasing is applied compared to reverse biasing.

A floating transistor bulk is also an option can be used by not connecting the bulk to any set voltage potential. According to simulations this is equivalent to a bias of Vdd/2 under DC

-

<sup>&</sup>lt;sup>1</sup> Between 0.6V and 0.7V for a silicon semiconductor p-n junction

conditions but can increase the on-current by up to 5% for transient signals with a full transition on the input due to parasitic capacitive coupling between the gate and bulk.

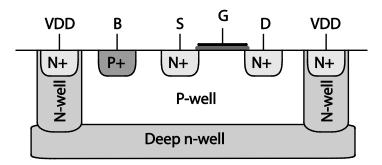

To apply a bias voltage to the body of an NMOS transistor which is effectively the substrate of the chip, it needs to be placed in a deep n-well. This is done to isolate the body of the transistor from the rest of the ground connected substrate. An illustration of this isolation is given in Figure 2.3.4.

Figure 2.3.4: Deep n-well illustration.

As we can see from this figure, the deep n-well adds an area overhead to the transistor. This is further increased by strict spacing rules needed for the manufacturing of the deep n-well, resulting in a high area penalty.

The PMOS transistor already has an isolated n-well and therefore does not need any extra modification for bulk biasing. This makes FBB an effective way to strengthen PMOS devices without the same increase in area.

Advantages Disadvantages

- Increases transistor strength.

- Deep N-well area penalty for NMOS.

- Increased leakage / reduced  $I_{on}/I_{off}$  ratio

### 2.3.3 Subthreshold scaling summary

In the previous sections several ways to increase the transistor strength in subthreshold operation are presented and simulated. These show that even though many of the conventional scaling techniques are ineffective and some even counterproductive at low voltages there are still ways to increase the transistor strength, even at subthreshold and near-threshold supply voltage levels.

In Table 2.3.1 a list of the presented subthreshold scaling techniques and their effects on the transistor "on"-current and the  $I_{on}/I_{off}$  ratio is presented. This table shows that the transistor strength can be significantly increased by combining the three scaling techniques described. It also shows that they have a larger effect on low threshold devices. The  $I_{on}/I_{off}$  ratio benefits most from increasing the length and using low-threshold transistors. By doubling the length alone this ratio can be increased by 36% while doubling the on-current, but together they can achieve an  $I_{on}/I_{off}$  ratio increase of 80% with 3 times the current of the minimum sized standard  $V_{TH}$  device. All three techniques can also be used at the same time to make the transistor as strong as possible. This is shown in Table 2.3.1 where a low-threshold transistor with a length of twice the minimum and full forward biasing yields an on-current 6 times higher than the standard-threshold, minimum sized and reverse biased device.

To sum up these findings the best way to increase the transistor strength is to use low-threshold transistors and further tune the strength by adjusting the channel length and keep the transistors reverse biased, at least for NMOS transistors. The advantages of using low-threshold transistors and increasing the length are both obvious in the table below and in the previous discussion, but when it comes to bulk biasing there are two reasons for this conclusion. One is the reduced ratio between the "on"-current  $(I_{on})$  and leakage current  $(I_{off})$  because static power consumption increases more than the dynamic, making it a less energy efficient circuit. The other is the area overhead this introduces for NMOS devices by requiring a deep n-well for bulk isolation.

Table 2.3.1 shows the effects of subthreshold scaling techniques on the transistor current that can be used to reduce the effects of process variations and increase circuit speed. As explained in section 2.3.1 the gate capacitance of the transistors with a 2×min length is twice that of the minimum length transistors which may have an effect on the delay reduction achieved by the increased current, depending on the application. For circuits where the gates are connected in series with an output capacitance dominated by the parasitic capacitance of gates with the same scaling, forward biased low threshold transistors will achieve the highest speed, but with the penalties to area and energy efficiency previously mentioned

| Type    | Bias | Length   | $I_{off}$ | $I_{on}$ | $I_{off}$ |         | $I_{on}$ |        |

|---------|------|----------|-----------|----------|-----------|---------|----------|--------|

| nch_mac | Rev  | 1 x min. | 26.22pA   | 251.3x   | 1         | 6.59nA  | ı        | -      |

| nch_mac | Rev  | 2 x min. | 37.43pA   | 340.6x   | +36 %     | 12.75nA | 1.9x     | +93 %  |

| nch_mac | Fwd  | 1 x min. | 65.62pA   | 217.0x   | -14 %     | 14.24nA | 2.2x     | +116 % |

| nch_mac | Fwd  | 2 x min. | 99.77pA   | 270.3x   | +8 %      | 26.97nA | 4.1x     | +309 % |

| nch_lvt | Rev  | 1 x min. | 32.50pA   | 340.6x   | +36 %     | 11.07nA | 1.7x     | +68 %  |

| nch_lvt | Rev  | 2 x min. | 41.49pA   | 451.9x   | +80 %     | 18.75nA | 2.8x     | +185 % |

| nch_lvt | Fwd  | 1 x min. | 84.83pA   | 271.5x   | +8 %      | 23.03nA | 3.5x     | +249 % |

| nch_lvt | Fwd  | 2 x min. | 115.20pA  | 340.1x   | +35 %     | 39.18nA | 5.9x     | +495 % |

Table 2.3.1: Simulation: Effect of sub-threshold scaling on transistor drive strength at 200mV.

### 2.4 Figures of merit

To analyze the performance of the circuits created in this thesis it is beneficial to have some figures of merit to be able to compare them to other logic styles and circuit topologies. The circuits created will be compared to standard CMOS circuits in order to give an idea about the value and quality of the circuits presented.

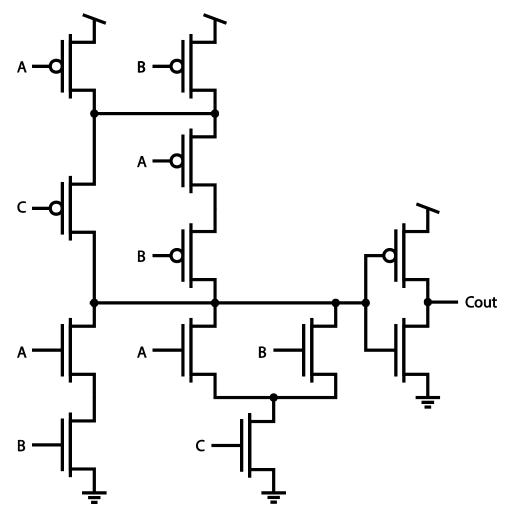

The conventional CMOS carry circuit shown in Figure 2.4.1 will serve as a benchmark for the carry circuits that will be proposed later in the thesis.

The figures of merit presented are; propagation delay, power, PDP and EDP.

Figure 2.4.1: Standard CMOS carry circuit.

### 2.4.1 Propagation Delay

The propagation delay of a circuit is an important factor that determines the speed and maximum operating frequency of an electronic system.

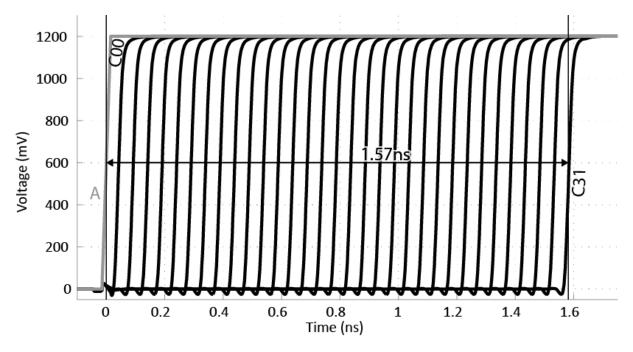

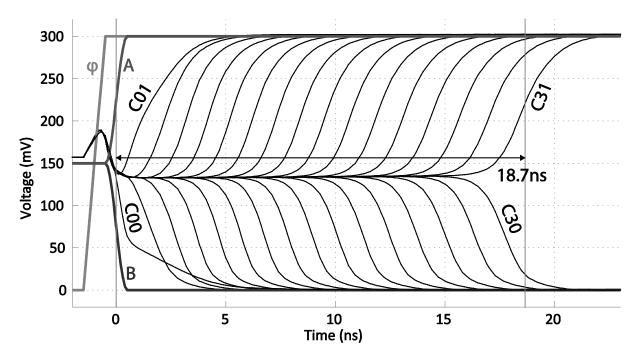

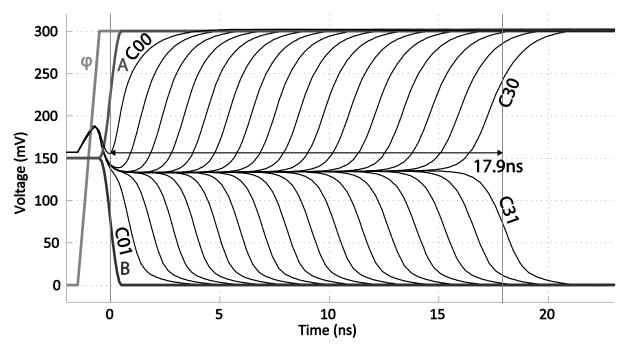

The carry propagation and delay of the conventional CMOS carry circuit can be seen in Figure 2.4.2 and shows that the carry propagation of the circuit is uniform and has a good noise margin. The delay of the 32-bit carry chain with a 1.2V supply voltage is 1.57ns, on average a 48ps propagation delay for each carry bit.

Figure 2.4.2: Simulation: Carry propagation through a standard CMOS carry chain at 1.2V.

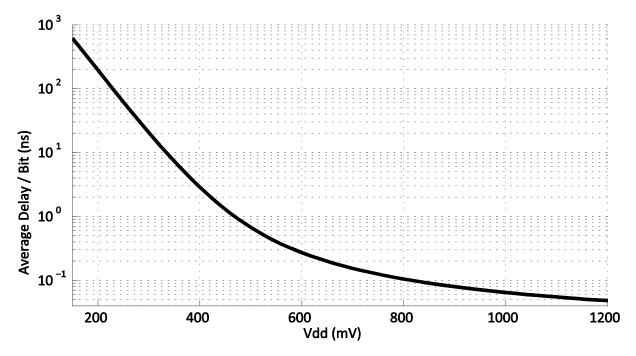

Because the propagation delay is exponentially dependent on the supply voltage (Vdd), the increase in delay is significant when Vdd is lowered, especially near the threshold voltage. The relationship between the supply voltage and the propagation delay is shown in Figure 2.4.3 where the delay per bit can be seen decreasing by orders of magnitude when the supply voltage is lowered to near-threshold values.

Figure 2.4.3: Delay per bit of a standard CMOS inverter.

|       | Best | @ 200mV | @ 1.2V  |

|-------|------|---------|---------|

| Delay | max. | 194.9ns | 48.01ps |

Table 2.4.1: Conventional CMOS Carry Propagation Delay.

#### 2.4.2 Power

The power consumption is an important factor to consider when designing a circuit, especially in applications with a limited supply of energy like in battery operated devices or a limited maximum power consumption like in devices relying on energy harvesting but can also be a factor in terms of heat development.

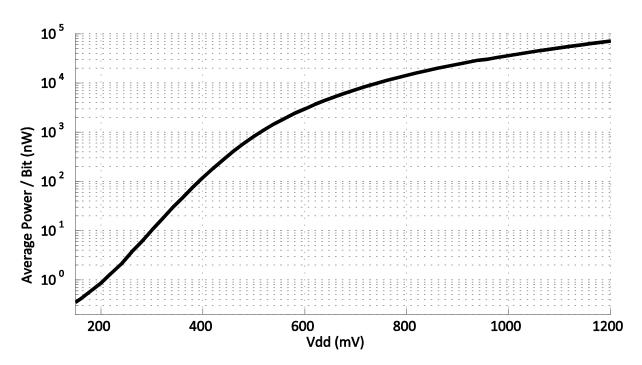

The power consumption of a circuit is strongly dependent on the supply voltage. Reduced power consumption is therefore one of the main reasons for lowering Vdd. The relationship between the supply voltage and the power consumption is shown for the conventional CMOS carry circuit in Figure 2.4.4 where the power consumed at 1.2V is almost five orders of magnitude<sup>1</sup> higher than that consumed at 0.2V. The power consumption at these voltages is shown in Table 2.4.1.

|       | Best | @ 200mV | @ 1.2V  |  |

|-------|------|---------|---------|--|

| Power | min. | 862.8pW | 71.27µW |  |

|       |      |         |         |  |

Table 2.4.2: Conventional CMOS Carry Power Consumption.

Figure 2.4.4: Simulation: Power consumption of a standard CMOS carry circuit.

\_

$<sup>^{1}</sup>$  0.826 × 10<sup>5</sup>

### 2.4.3 Power-Delay Product

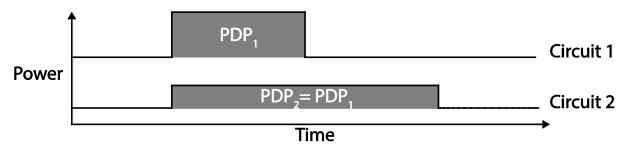

The power-delay product (PDP) is simply the average power consumption times the delay of a circuit and represents the average energy consumed per switching event, it is therefore also known as the switching energy. The PDP says something about how much energy is consumed to perform an operation and is therefore a good figure of merit to determine circuit performance in terms of energy efficiency. In Figure 2.4.5 it is shown that circuit 1 and circuit 2 will spend the same amount of energy to perform the same calculation because circuit 2 uses half as much power as circuit 1 but spends twice the time on it, resulting in the same PDP and showing that the two circuits are equally energy efficient.

Figure 2.4.5: Illustration of PDP.

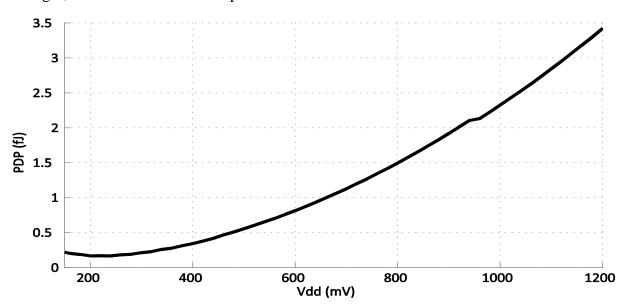

For this reason PDP can be used to compare energy efficiency for different circuit topologies with different power and speed characteristics. The PDP varies with the voltage supply and this relationship is shown in Figure 2.4.6. The optimal supply-voltage for the conventional CMOS carry circuit according to the PDP analysis is at 240mV, just below the transistor threshold voltage<sup>1</sup>, with a PDP of 0.166fJ as presented in Table 2.4.2.

Figure 2.4.6: Simulation: PDP of a standard CMOS carry circuit.

|     | Best     | @ 200mV  | @ 1.2V  |

|-----|----------|----------|---------|

| PDP | 0.1659fJ | 0.1681fJ | 3.411fJ |

Table 2.4.3: Conventional CMOS Carry PDP.

-

$<sup>^{1}</sup>$  V<sub>TH</sub> = 267mV according to the TSMCN90RF spice models.

### 2.4.4 Energy-Delay Product

The energy-delay product is a metric representing the achieved speed of the circuit relative to the energy consumed and is calculated by multiplying the switching energy (PDP) the propagation delay.

In terms of PDP, the two circuits in Figure 2.4.5 perform equally well, but in reality circuit 1 would be the obvious choice for most applications because a faster circuit leaves more flexibility in terms of data throughput, system response time and algorithm complexity.

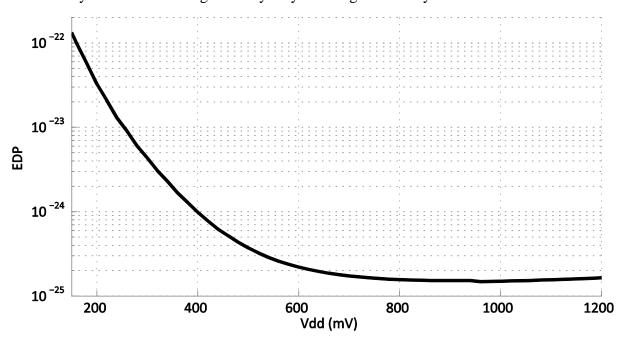

In contrast to the PDP of the Figure 2.4.5 circuits, the EDP of Circuit 1 is twice that of circuit 2 because it finishes the operation twice as fast using the same amount of energy. The more speed-oriented but still energy aware nature of the EDP is the reason it is a widely accepted metric for comparing performance of digital circuits. For the conventional CMOS carry circuit, the EDP is highly dependent of the supply voltage, and as shown in Figure 2.4.7 the PDP increases by four orders of magnitude by only reducing the Vdd by 80%.

Figure 2.4.7: Simulation: EDP of a standard CMOS carry circuit.

The optimal supply voltage for the standard CMOS carry circuit according to the simulation results in Figure 2.4.7 is 0.96V where it achieves an EDP of just 0.1486yJs.

|     | Best      | @ 200mV  | @ 1.2V   |

|-----|-----------|----------|----------|

| EDP | 0.1486yJs | 32.77yJs | 0.643yJs |

|     | ~         |          |          |

Table 2.4.4: Conventional CMOS Carry EDP.

### 2.4.5 Standard deviation ( $\sigma$ )

Standard deviation, commonly represented by  $\sigma$ , is a figure representing variation, which in IC design is caused by process variations.

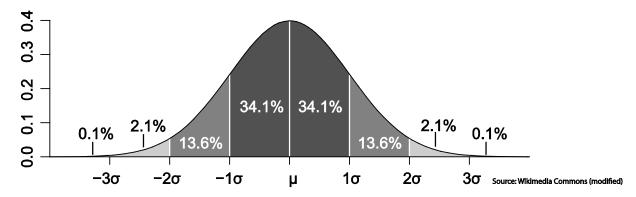

The standard deviation represents how much the result will deviate from the mean value with a certain probability, and can in turn be used in IC design to show the probability of the circuit performing within the required boundaries. This probability is referred to as yield and shows the number of circuits that need to be thrown away in an average production run. As shown in Figure 2.4.8, one  $\sigma$  represents the deviation from the mean ( $\mu$ ) where 68.2% of the results will be, and for two  $\sigma$ , 2×13.6% can be added giving a yield of 95.4% and so forth. Put in another way, if one  $\sigma$  can be tolerated, 68.2% of the circuits will fulfill the requirements.

Figure 2.4.8: Standard deviation diagram.

This is why a low standard deviation is desirable and will result in a higher production yield by being able to accept a higher number of standard deviations and/or increase the precision and performance of the circuit.

For discrete random variables from  $x_i$  to  $x_N$ , which is most relevant for the results in this theses the formula for the standard deviation is:

$$\sigma = \sqrt{\frac{1}{N} \sum_{i=1}^{N} (x_i - \mu)^2}, where \ \mu = \frac{1}{N} \sum_{i=1}^{N} x_i = mean(x)$$

In this thesis standard deviation will not be a significant focus, but will be used to analyze chip measurements.

## 3 Design

This chapter will cover the design, production and measurement of ULV circuits. The tools used for design and simulation of both the schematic and the layout of the circuits are from the Cadence<sup>®</sup> Custom IC Design kit where Virtuoso<sup>®</sup> and Spectre<sup>®</sup> are used together with the TSMCN90RF device model library for the 90nm TSMC<sup>®</sup> Nexsys<sup>®</sup> process.

### 3.1 Implementation of an Ultra-Low-Voltage Inverter

#### 3.1.1 Intro

A lot of simulations have been performed on ULV logic in papers, master theses and PhD dissertations, but few implementations and little work has been done in the manufacturing these circuits. So to show that the features of ULV logic also apply in hardware, an implementation of ULV logic in a 90 nanometer process will be manufactured in this thesis.

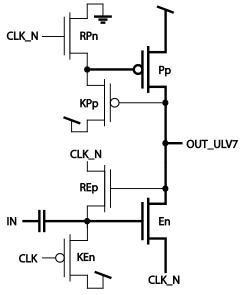

The logic style chosen for implementation is the 7<sup>th</sup> iteration of the ULV logic (ULV7) because it is the latest, most robust and one of the fastest ULV topologies published this far. The chosen circuit is the ULV7 N-type inverter, scaled to handle the load of a measurement setup. This is because a minimum scaled circuit would need buffers to drive the outputs that would mask the analog properties of the circuit with those of the buffer used. A traditional CMOS inverter with equivalent scaling will also be implemented on the same chip as a reference and a benchmark for the circuit performance.

A paper on the chip production is also written [12] and accepted for publishing at the IEEE International Nanoelectronics Conference (IEEE INEC2014). See appendix, section 5.1.

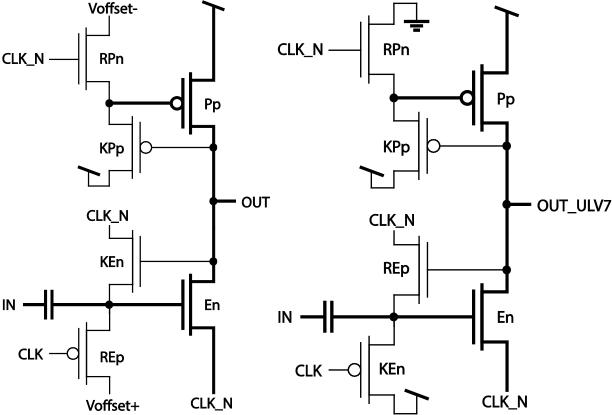

# 3.1.2 7th Generation Ultra-Low Voltage Logic

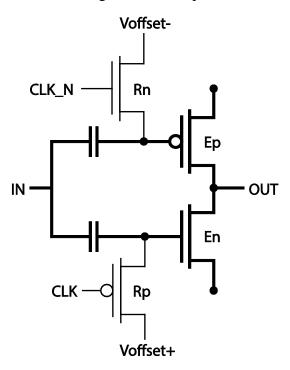

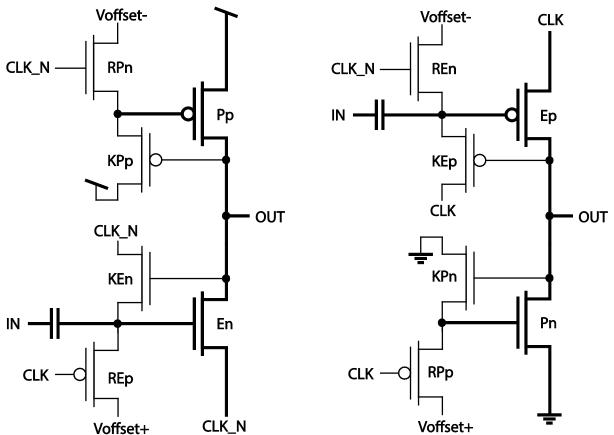

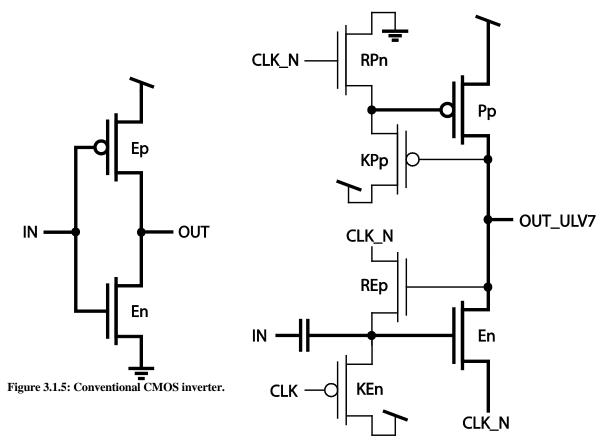

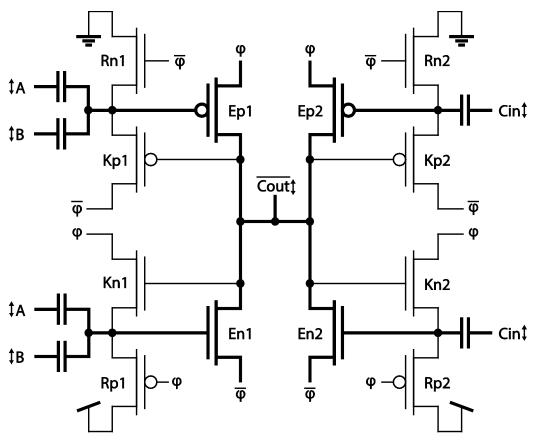

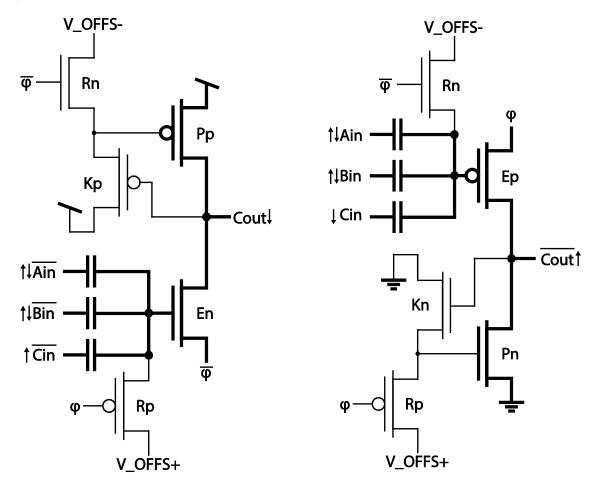

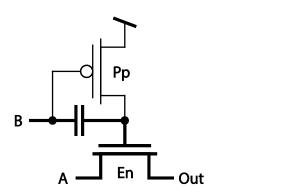

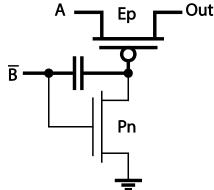

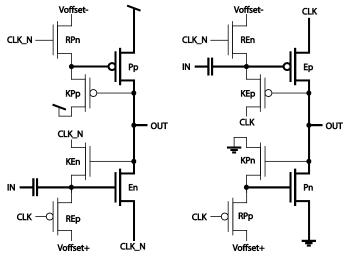

The ULV7 logic style chosen for this chip has been called robust low-power CMOS precharge logic in previous papers like [13] and is based on the ULV5 [14] logic style. Like other domino logic it has a precharge phase and an evaluation phase. In the precharge phase the output is charged to '1' for the N-type circuit and to '0' for the P-type circuit, but when the evaluation phase arrives, the circuits will either switch or not switch depending on the input(s) and logic. For an N-type circuit with a precharge value of '1' the output logic is decided by a pull-down network (PDN). The complimentary P-type circuit logic is decided by a pull-up network (PUN).

The two phases of operation for these circuits are defined as the precharge phase when CLK = '0' and  $CLK_N =$  '1', and as the evaluation phase when CLK = '1' and  $CLK_N =$  '0'. The following is an elaboration on the roles of the transistors and signals for the N-type inverter in both of these phases:

**Precharge phase:** When the ULV7 N-type inverter shown in Figure 3.1.1 enters the precharge phase, the floating gate of the evaluation transistor (*En*) is charged to *Voffset*+ through *REp*, and the gate of the precharge transistor (*Pp*) is charged to *Voffset*- through *RPn*. *Voffset*+ and *Voffset*- are usually set to Vdd and ground respectively but can also have other values to reduce or increase the speed and power consumption. This means that both *En* and *Pp* are semi-conducting and slowly charging the output to '1' during the precharge phase.

**Evaluation phase:** During the evaluation phase the *RPn* and *REp* transistors are turned off, allowing the *Pp* and *En* gates to float so that an arriving rising edge will cause the *En* floating gate to be super-charged and drive the output to '0' from *CLK\_N*. The low output will then turn *KPp* on and pull the *Pp* gate to '1' effectively securing the output to '0'. On the other hand if the input stays at '0' the weak *KEn* transistor will be on and slowly lower the *En* floating gate voltage. This means that the *KEn* strength needs to be designed to make sure that the precharge value is held and that the circuit accepts inputs through the entire evaluation phase.

The P-type circuit works based on the same principle but in a complimentary manner to the N-type, with the floating gate on the Ep PMOS transistor as shown in Figure 3.1.2, making the NMOS the precharge transistor (Pn).

| ULV7 Inverter sig | N-type |          | P-type |     |     |     |

|-------------------|--------|----------|--------|-----|-----|-----|

| Signal            | CLK    | $CLK\_N$ | IN     | OUT | IN  | OUT |

| Precharge phase   | 0      | 1        | 0      | 1   | 1   | 0   |

| Evaluation phase  | 1      | 0        | 0/↑    | 1/↓ | 1/↓ | 0/↑ |

Table 3.1.1: Signal phases of the ULV7 inverter.

Figure 3.1.1: Schematic: ULV7 N-type inverter.

Figure 3.1.2: Schematic: ULV7 P-type inverter.

### 3.1.3 Design Considerations

When designing an electronic circuit in a nanoscale process it is necessary to be aware that a single minimum size transistor is not strong enough to drive the capacitive load of an output pad. For this reason, a strategy to allow measurements of the circuit needs to be chosen. The two viable solutions available are to either scale the circuit to be able to handle the capacitive output load or add a buffer for each output. For larger digital systems where only the digital properties are tested, buffers are the best choice because they allow for a smaller circuit area for the implemented logic and can still deliver the correct output. The downside to using buffers is that they can only verify or refute that the logical value of the output is correct. Any analog properties like speed and noise margin measured on these outputs will be those of the buffer and not the implemented logic, so for this test circuit the scaling solution is chosen because, even though it is a digital circuit, it is the analog properties that are interesting at this research stage.

To scale the circuit properly, the output capacitance needs to be estimated before a test bench is made and simulations are run. The output capacitances that are considered will consist of probe pads, bonding wire, chip carrier leads, socket, PCB and oscilloscope measuring probes. The total estimated output capacitance will therefore be based on the following assumptions:

Pad frame + bonding + CC leads ~1pF Socket + PCB 3-4pF Measuring probes 15pF Sum 20pF

These assumptions are used to create a test bench for each of the inverters with an output load capacitance of 20pF.

In addition to being scaled to drive the output load, the transistors will be scaled to give a reasonably fair comparison between the two inverters that resembles minimum size conditions.

Nominal pre-layout schematic simulations indicate that the ULV7 inverter is approximately 65 times<sup>1</sup> faster than the conventional CMOS inverter. Further elaborations on simulation results are presented in section 3.1.4.

-

<sup>&</sup>lt;sup>1</sup> 300mV: 1.01us/15.5ns = 66x 200mV: 9.1us/154.7ns= 63x

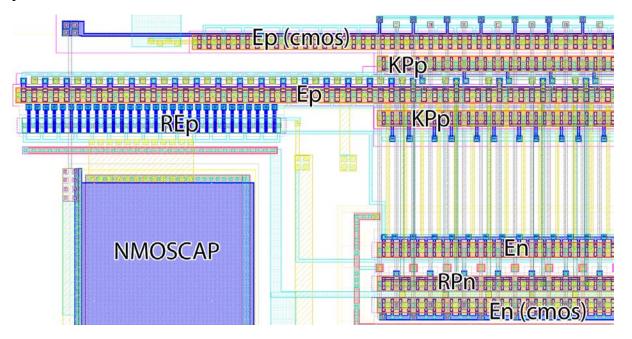

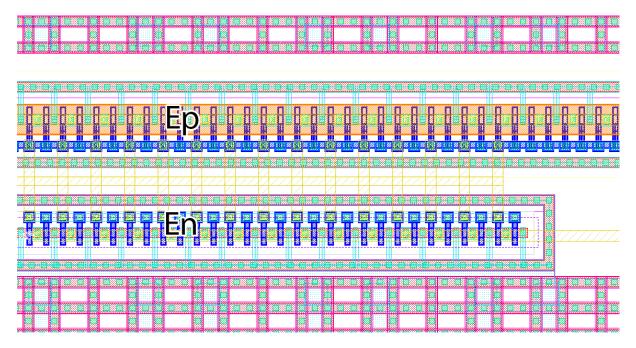

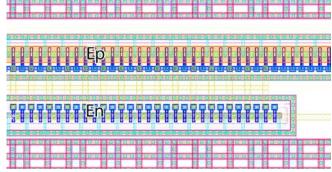

#### 3.1.3.1 High-Speed Layout

The goal of this version of the layout is to achieve high speed per area for both inverters and is therefore designed using the ultra-low voltage strength enhancement techniques explained in section 2.3.

To increase the transition speed, the current through critical transistors needs to be increased in order to charge the load and parasitic capacitances faster. Achieving a higher current through the device can be done by lowering the effective threshold voltage of the transistor [10]. For this purpose the low-threshold transistors, nch\_lvt from the TSMC® Nexsys® process were used, this alone reduces the threshold voltage by 7% and increases the drive strength by 68% compared to the standard nch\_mac transistors from the same process. The effective threshold voltage was further reduced by applying a forward bias to the bulk of the transistor. Together with the lvt device this resulted in a 249% drive strength increase. Forward biasing the PMOS devices is done by connecting the n-well to ground; the NMOS devices on the other hand require the transistors to be enclosed by a deep n-well for insulation to allow increasing the substrate voltage around the transistor while keeping the rest of the substrate grounded. The deep N-well can be seen around the *En*, *RPn* and the *En* (*cmos*) transistors in Figure 3.1.3

The last low-voltage trick applied in this version to increase the drive strength for critical transistors was increasing the transistor length to exploit the reverse short channel effect, lowering the effective threshold voltage even further and increasing the drain-source current to achieve the correct strength ratio. The increased finger length is visible on the *Ep* and *Ep* (*cmos*) transistors in Figure 3.1.3.

To save area, a metal-oxide-semiconductor capacitor (MOSCAP) was chosen as the input capacitor for the ULV inverter because of its high capacitance density despite its poor accuracy. This is done because the capacitor is used as a blocking capacitor and its value is not a critical parameter for this circuit.

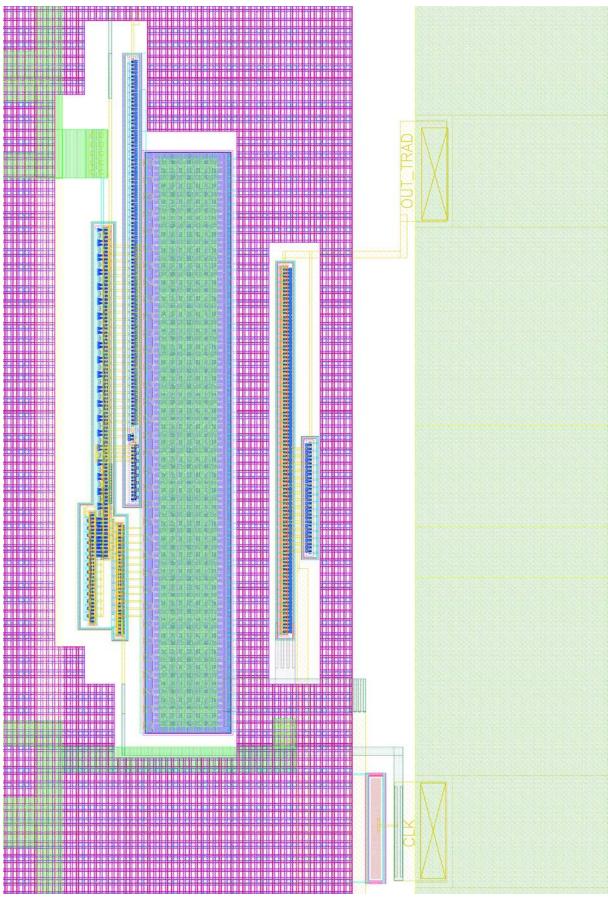

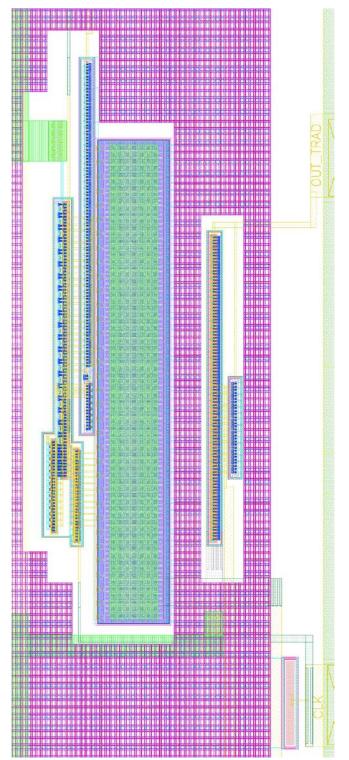

Figure 3.1.3: High-Speed Layout.

-

<sup>&</sup>lt;sup>1</sup> Spice model Vth of nch 1vt:0.2489V, standard nch mac:0.2668V. 1-(0.2489/0.2668)=6.7%.

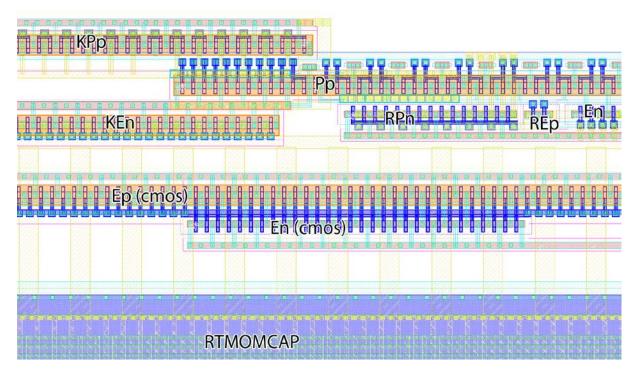

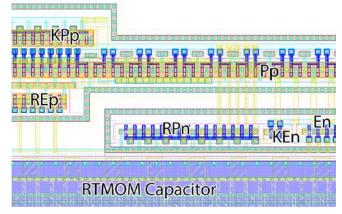

#### 3.1.3.2 High-Yield Layout

This version of the layout targets a high production yield to increase the probability of achieving measurable results and still keep a fair and accurate comparison between the two inverters.

The high-speed layout version was created using subthreshold strength enhancement design techniques to make both the ULV7 inverter and the traditional inverter as fast as possible. In this version, the transistor strengths are only adjusted with the number of transistor fingers. This causes a larger layout area but also supports a higher production yield and allows for a wider range of supply voltages. The increased area is not an issue for this design as long as it does not violate area the constraints for the project which provides plenty of space. All transistors have also been reverse-biased to avoid the need for a deep n-well and to reduce the static leakage of the circuits.

For the coupling capacitor on the evaluation transistor floating gate in this version of the layout, a rotative metal-oxide-metal (RTMOM) capacitor was chosen instead of a MOSCAP because it can be placed in the metal layers above the transistors and thereby reduce the effective area consumed by the capacitor, they also provide a higher accuracy for the capacitive value. As mentioned before the accuracy of the capacitor is not critical for the correct operation of the circuit but large variations can affect the speed. The capacitor is placed next to the transistors to make the layout more lucid. The important parts of the layout are shown in Figure 3.1.4.

Although a smaller effective substrate area is consumed by the RTMOMCAP due to its placement in the metal layers, its physical size is larger than that of a MOSCAP of the same capacitance, and in addition to a larger capacitance needed due to the larger number of transistor fingers, the overall capacitor area in this layout version is several times larger than in the high-speed layout version.

Figure 3.1.4: High-Yield Layout.

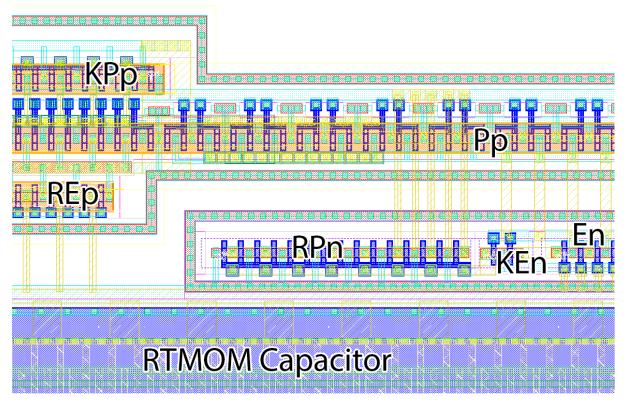

### 3.1.3.3 Final Layout

Because the goal of creating the chip is to compare the ULV7 logic style to the conventional CMOS logic style and not to achieve the highest possible speed reachable in the given process, the final layout is based on the high-yield layout. The biggest changes to this version is that the inverters are moved apart and separated with substrate ground connections seen as the blue, red and purple grid in Figure 3.1.10 or the pink area in Figure 3.1.9. This has been done to isolate the circuits from each other and to reduce crosstalk and leakage between the two.

Figure 3.1.6: Implemented ULV7 inverter.

Transistors that are connected to die pads need to be shielded using guard rings to protect against static electricity and voltage spikes, because all the transistors in this design are connected to an input or an output, they are all protected with guard rings.

The final sizing of the transistors is shown in Table 3.1.2 and is a result of optimizing the circuit operation for layout simulations. There are two things that stand out in this table, one is the *KEn* transistor with a size of only 2 fingers and the other is the large ULV7 *En* transistor. The reason for the small size of the *KEn* transistor is that this transistor drains the floating node during the evaluation phase as long as the output is '1' making it degrade the circuit performance after a certain amount of time, so a smaller transistor means a longer operational evaluation phase and a larger transistor means a more static '1'. The sizing of the ULV7 *En* transistor is optimized for speed based on layout simulations that allow the *En* transistor to be larger than the *Pp* and still produce a strong '1' and a low-delay output transition.

|             | ULV7 |    |     |     |     |     | CM   | OS   |

|-------------|------|----|-----|-----|-----|-----|------|------|

| Transistor: | En   | Pp | KPp | RPn | REp | KEn | NMOS | PMOS |

| Fingers:    | 100  | 90 | 30  | 15  | 30  | 2   | 30   | 100  |

Table 3.1.2: Chip transistor sizing.

The optimal transistor sizing obtained when running schematic simulations were closer to the sizes intuitively expected, but the layout simulation optimizations were chosen as the more reliable source because more variables, parasitics and layout specific choices are considered.

The Standard inverter has a PMOS-to-NMOS size ratio of 3 to 1 because the NMOS is approximately 3 times stronger than the PMOS in the ultra-low voltage region as shown in section 2.3.1. A segment of the conventional CMOS layout displaying the NMOS (En) and PMOS (Ep) transistors with guard rings and the substrate ground connection mesh for isolation is shown in Figure 3.1.7.

Because of the small *KEn* transistor, a discharge diode is added to the *CLK* input to satisfy the TSMC antenna rules requiring a certain area of oxide diffusion per area of metal connected. This can be seen next to the *CLK* pad connection in Figure 3.1.10 on page 26. The size of this diode is purely based on approximations and intuition because the connected pad frame is a TSMC trade secret, making the amount of connected metal hidden. Final design rule checks (DRC) and layout versus schematic (LVS) checks were run with the pad frame by TSMC before production to allow correcting errors arising from the added metal.

To reduce the area impact of the capacitor, a rotative metal-oxide-metal (RTMOM) capacitor like in the high-yield layout is chosen because it can be placed in the metal layers above the substrate and logic. The RTMOM capacitor has a simulated capacitance of 890fF and is placed next to the transistors in the layout for improved lucidity as shown in Figure 3.1.10. The full capacitor specifications are presented in the table below.

| Model  |            | Capacitance | Fingers |         |       |      | Metal layers |     |  |

|--------|------------|-------------|---------|---------|-------|------|--------------|-----|--|

| Name   | IMEC#      | Simulated   | Width   | Spacing | Horiz | Vert | Bottom       | Top |  |

| CRTMOM | 2668561832 | 890.403fF   | 140nm   | 140nm   | 200   | 20   | 1            | 7   |  |

**Table 3.1.3: RTMOM Capacitor details**

Figure 3.1.7: Traditional CMOS inverter layout.

The segment of the ULV7 layout in Figure 3.1.8 shows the placement of the transistors and the guard rings combined for the NMOS and PMOS transistors respectively. A layout overview and size comparison of the inverters and their placement is shown in Figure 3.1.10 on page 26.

Some capacitance is also added on the Vdd connections to reduce supply voltage noise, seen as the green grid on each side of the circuit in Figure 3.1.9.

Figure 3.1.8: ULV7 inverter layout.

Figure 3.1.9: Full Layout.

Figure 3.1.10: Layout overview

### 3.1.4 Simulations

The circuits were simulated on both schematic and layout level. The same test bench is used for both inverters with the only difference being the model of the design; where one is extracted from the circuit schematic and the other from the layout, yet the nominal simulations show significant differences between the two. The expected result would be a slight reduction in performance due to parasitic capacitance, resistance and inductance but this is not the case here because the performance is significantly increased in the layout with a larger difference than expected. The most reasonable explanation is that the transistor models used are not properly installed and/or not properly tested for Ultra-low voltage operation with a large number of fingers.

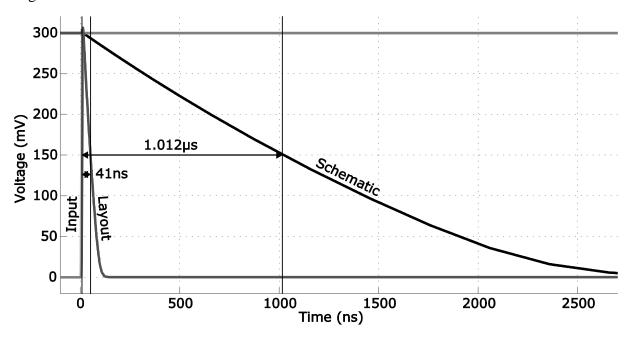

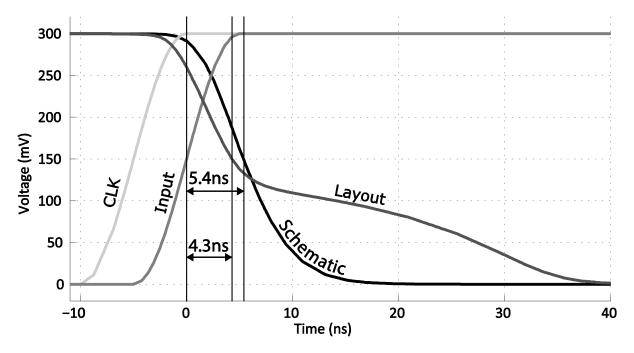

Figure 3.1.11: Simulation of schematics and layout of the conventional CMOS inverter.

The differences between layout and schematics simulation for the ULV7 inverter are a lot smaller than for the traditional CMOS inverter layout. This could be an indication of a lower threshold voltage for the layout version of the transistors because the ULV7 circuit is less susceptible to these changes. The differences can be seen in Figure 3.1.11 and Figure 3.1.12; they show that the delay of the traditional CMOS inverter is 96% lower than the schematic of the same circuit. The layout simulation of the ULV7 inverter is affected in a different way and introduces the distortion of the output signal seen in Figure 3.1.12, resulting in a higher fall time.

Throughout the design process, the layout simulations are chosen as the more trustworthy verification source because it considers more parameters, so the circuits are designed to work optimally in layout conditions.

Figure 3.1.12: Simulation of schematics and layout of the ULV7 inverter.

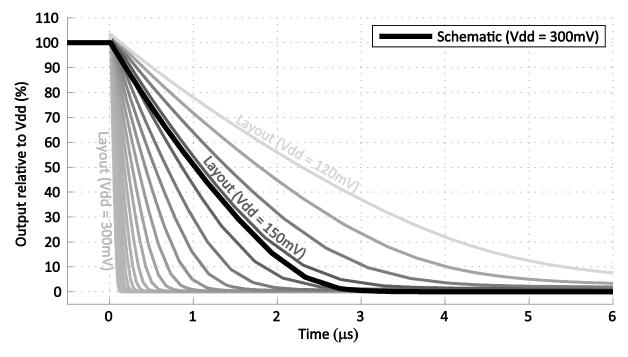

It might seem as though the threshold voltage of the layout transistor model for many-fingered transistors is lower than the schematic model because of the increased speed of the traditional inverter and what seems like a large leakage from the floating gate introducing distortion of the layout ULV7 inverter. For the traditional inverter the transient response of the layout seems to be closer to the schematic when half the supply voltage is used, as shown in Figure 3.1.13.

Figure 3.1.13: Simulation: Sweep of Vdd on the CMOS inverter layout, compared to the schematic.

As these differences are most likely due to Cadence installation errors and not design, they will not be discussed further.

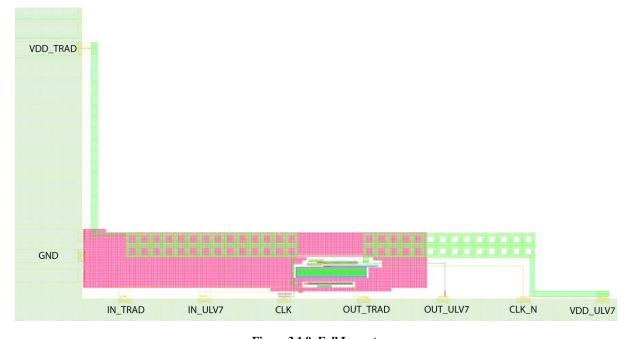

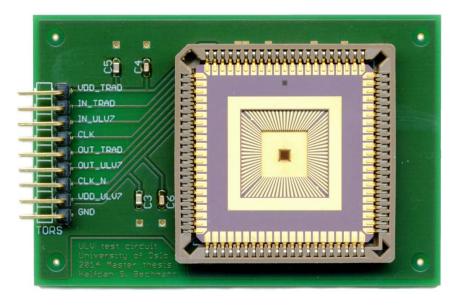

# 3.1.5 Final chip

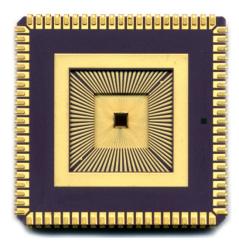

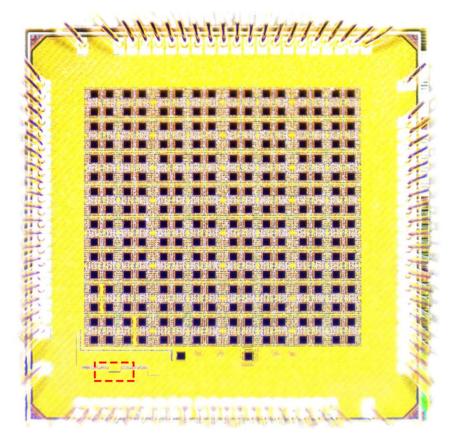

After production the chip was bonded and packaged at the TSMC foundry in Taiwan. The package used is a J-lead ceramic chip carrier with 84 leads (JLCC84). It has 21 leads on each of its four sides, and is bonded using gold wires. The finished and bonded package is shown in Figure 3.1.14.

The RTMOM capacitor and the M9 Vdd paths can be seen in the red square in the lower left corner of the die close-up in Figure 3.1.15 and the rest of the chip area belongs to a different project.

Figure 3.1.14: Final chip bonded in JLCC84 package.

Figure 3.1.15: Die close-up, the capacitor and M9 Vdd paths are visible in the red square.

### 3.1.6 Circuit Board

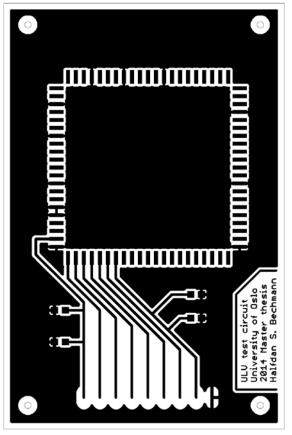

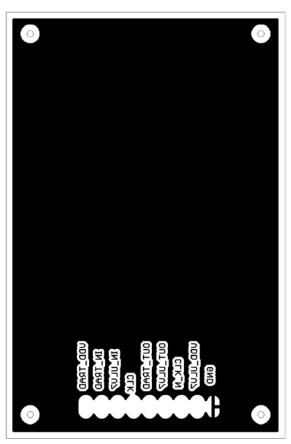

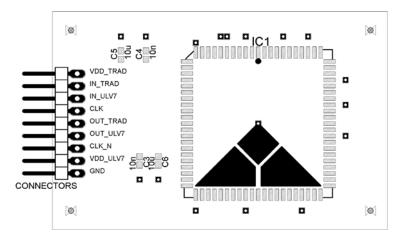

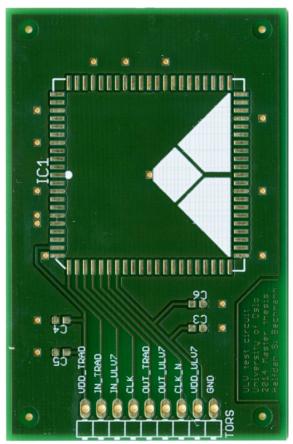

To do measurements on the chip, a printed circuit board (PCB) is needed to connect the leads of the chip carrier to the right probes and wires. For this purpose a PCB was designed using EAGLE and manufactured in China by Elprint. It is a small and simple double-sided design with one capacitor of 10uF and one of 10nF added to each supply voltage path to reduce noise. These can be seen in Figure 3.1.18 as C2, C3, C4 and C5. The top side copper layer is shown in Figure 3.1.16 and the bottom side copper layer which is all connected to ground can be seen in Figure 3.1.17. A series of pins need to be connected to ground to disable the other project on the chip. All the ground connected pins have vias placed next to them; the vias and component placement is shown in Figure 3.1.18.

Because the JLCC84 package is the ceramic equivalent of the PLCC84 package, a PLCC84 socket is used to make changing the chip easier when measuring several chips to analyze variations in the production process.

Figure 3.1.16: PCB: Top electric layer.

Figure 3.1.17: PCB: Bottom electric layer.

Figure 3.1.18: PCB: Top paste, silk and via layers.

Both surface-mount technology (SMT) and thru-hole technology (THT) is used on this PCB because SMT is quick and easy for larger quantities of components and pads when the proper equipment is in place and THT is necessary for the chosen header connectors. The surface mounted devices (SMDs) were soldered on by applying solder paste manually to the required pads and using a reflow oven for the curing process, but the thru-hole pin header was soldered on manually. The top and bottom of the finished PCB are shown below and the soldered PCB with the chip carrier mounted is shown in Figure 3.1.21.

Figure 3.1.19: Top side of the finished PCB.

Figure 3.1.20: Bottom side of the finished PCB.

Figure 3.1.21: Soldered PCB with chip carrier mounted.

### 3.1.7 Test setup

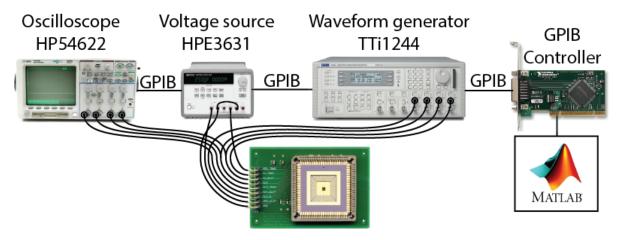

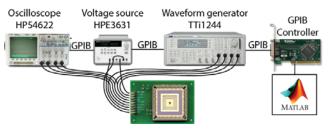

To measure the analog properties of the circuits, a proper test setup is needed. To be able to do scripted measurements and run parameter sweeps it is important that all the instruments can be controlled remotely. One of the simplest protocols for this is the general purpose interface bus (GPIB), which is found on most high-end instruments, is the protocol that will be used for remote instrument control in this setup. When it comes to the circuit inputs, the ULV7 inverter needs 3 input signals in addition to the ground and supply voltage, and the inverter needs one. This creates a demand for four different channels which is available on the TGA1244 from Thurlby Thandar Instruments (TTi). The TGA1244 will therefore be used to generate the needed inputs. A remote controlled voltage source is also needed and the Agilent HPE3631 is chosen for this purpose. Lastly, an oscilloscope with at least 4 channels is needed to measure both inputs and outputs, or all three inputs and the output of the ULV7 inverter. The Agilent HP54622 is chosen as the oscilloscope for the setup.

An illustration of the full test setup is presented in Figure 3.1.22 and examples of the measurement scripts run are provided in the appendix (section 5.2.1).

Figure 3.1.22: Test setup

### 3.1.8 Measurements

### 3.1.8.1 Simulation comparison

In this section the measured results will be compared to the previous simulations to get an idea of the simulation accuracy of the tools and models used.

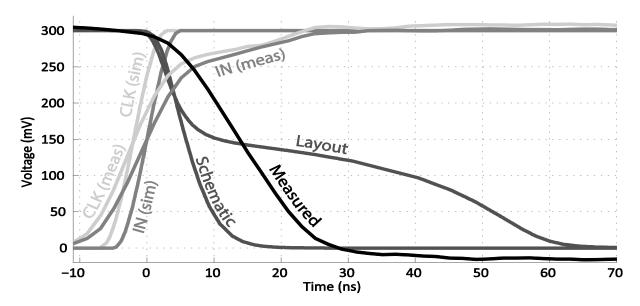

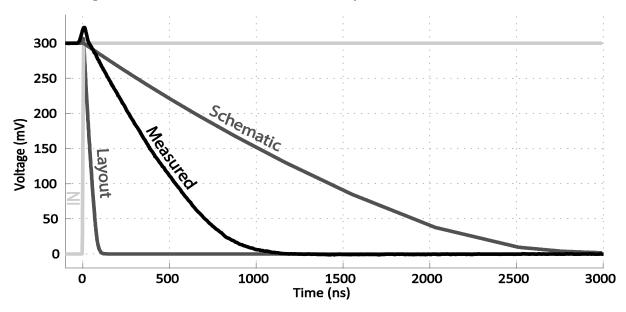

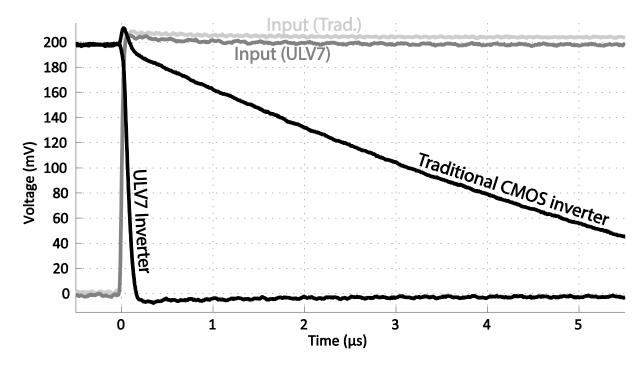

The final measurements seem to be closer to the schematic simulations than the layout simulations. This is shown in Figure 3.1.23 and Figure 3.1.24 and might indicate that the layout models are not properly adjusted or calibrated for the large transistor sizes and low voltages used in this design. Because the transistors were scaled under the assumption that the layout simulations were the most accurate; the strength of the evaluation transistor in the ULV7 inverter has been set too high. This introduces the need for a post-production strength reduction of the *En* transistor, which is performed in the next section.

Figure 3.1.23: ULV7 inverter, schematic simulation, layout simulation and measured results.

Figure 3.1.24: Schematic and layout simulation, and measured results of the conventional CMOS inverter.

The measurements have been compared to the simulations and the nominal schematic simulations both have a delay that deviates from the average measurements by approximately a factor two. This deviation is within  $2 \times \sigma$  for the schematic Monte Carlo simulations, making the schematic results acceptable. The layout simulations from this setup on the other hand should be disregarded because the average of the measured results deviate from the nominal simulations by more than  $5 \times \sigma$  in addition to introducing distortions.

### 3.1.8.2 Postproduction adjustments

When the chip came back from production and measurements were performed the *En* transistor in Figure 3.1.26 was found to be too strong resulting in an erroneous output value as shown in Figure 3.1.27 and Figure 3.1.28. To perform a post-production strength reduction, the precharge level of the *En* floating gate needs to be lowered.

Because *V\_OFFS*+ in Figure 3.1.25 is hard-wired to Vdd in the implemented circuit as shown in Figure 3.1.26 due to a limited number of pads weakening the *En* transistor requires some creativity. One way to lower the precharge level is to apply a positive offset to the *CLK* signal, reducing the *REp* current and thereby the time it takes to charge the floating gate. The offset needed is therefore influenced by both the clock frequency and the supply voltage, so by adjusting both correctly the precharge of the floating gate can be stopped before the gate is fully recharged resulting in a lower operation point and a weaker transistor.

Valid results using this method was not achieved for supply voltages lower than 190mV because the measurements at these voltages require a long precharge period, where the current through *REp* could not be reduced enough using reasonable offset voltage levels. For voltages of 190mV and above the postproduction adjustments were successful.

Figure 3.1.25: Schematic: N-type ULV7 inverter.

Figure 3.1.26: Schematic: Implemented N-type ULV7 inverter.

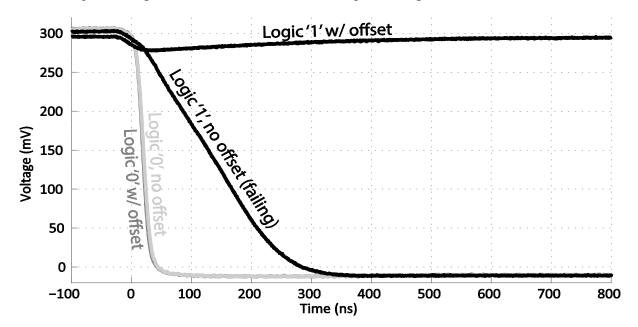

At 300mV an offset of 170 mV results in a stable logic '1' output and the inverter delay is actually reduced by 6% most likely due to less charge leaking trough REp at the start of the evaluation phase. To achieve a stable logic '1' with a 200mV supply voltage, a 120mV offset is needed. The delay using this offset is 19% higher than without the offset due to the lower floating gate voltage. The difference between the '1' with and without the offset applied is shown in Figure 3.1.27 for the 300mV measurements and in Figure 3.1.28 for the measurements run at 200mV. The input signal is not shown but keeps its precharge value of '0' for the Logic '1' output and switches to '1' for the Logic '0' output.

Figure 3.1.27: Measured: ULV7 output (170mV offset on CLK at 300mV and 400kHz).

Figure 3.1.28: Measured: ULV7 output (150mV offset on CLK at 200mV and 40kHz).

<sup>2</sup> Delay measured at 300mV: w/o offset: 36.ns, w/ offset: 43ns, 43/36-1=0.1944

-

<sup>&</sup>lt;sup>1</sup> Delay measured at 200mV: w/o offset: 19.8ns, w/ offset: 18.6, 1-18.6/19.8=0.0606

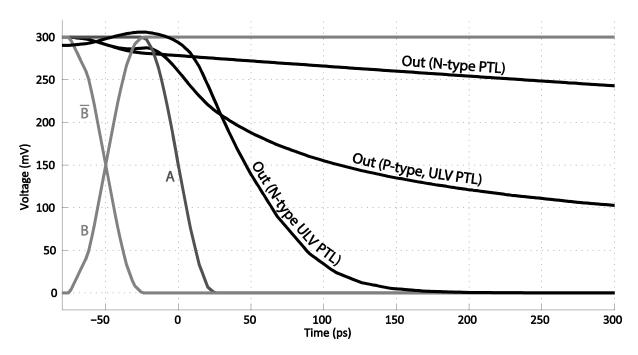

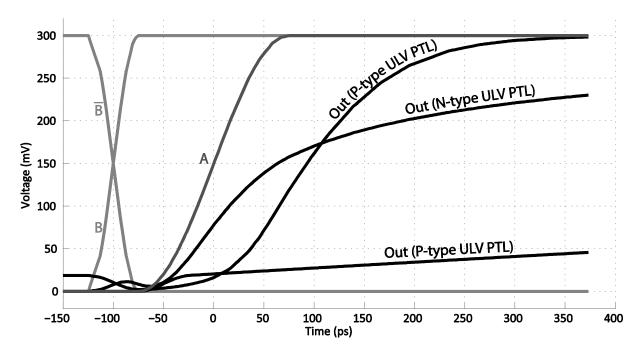

#### 3.1.8.3 Results

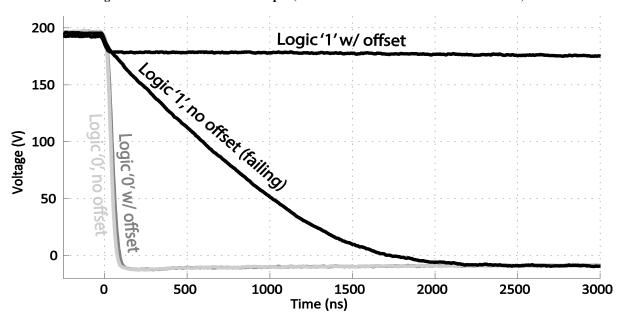

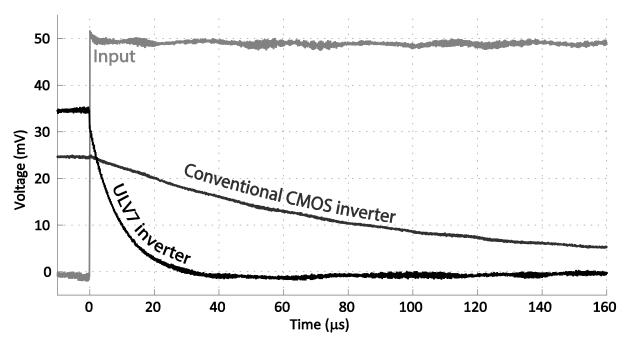

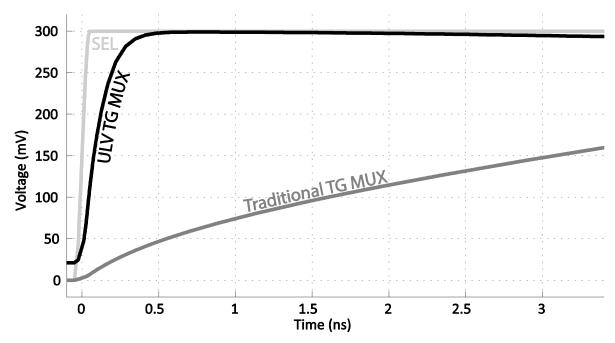

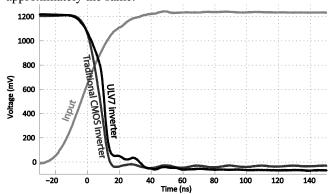

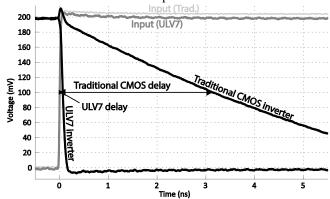

The transient measurements of the inverters shown in Figure 3.1.29 clearly show the difference in delay between the two. Here shown with a supply voltage of 200mV. The capacitive coupling between the input and output is also less apparent. The input of the traditional inverter is significantly steeper than what is realistic for this circuit. This is done because of limitations in the frequency generator not allowing phase-lock synchronization of custom waveforms. This is achievable for square-waves, which is why these are used for clocks and inputs for both circuits with a 10MHz Bessel filter applied to increase the rise- and fall-time. Because of these limitations, the measurements portray the traditional CMOS circuit as slightly faster than it should, which causes the differences between the two measured inverters to be slightly understated.

Figure 3.1.29: Measured: Transient response of the inverters at 200mV.

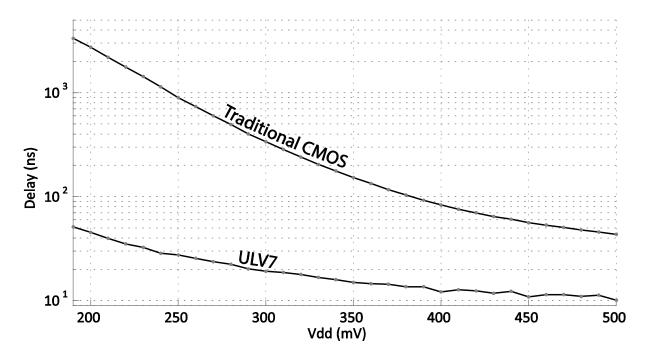

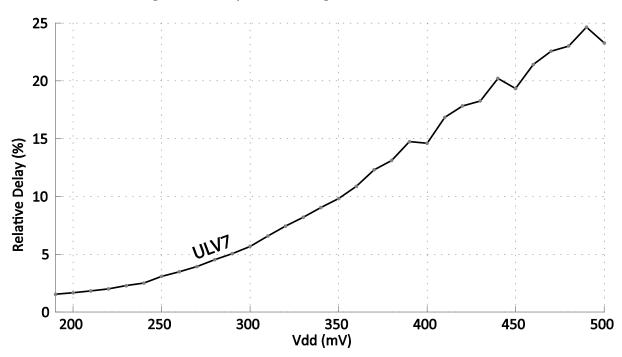

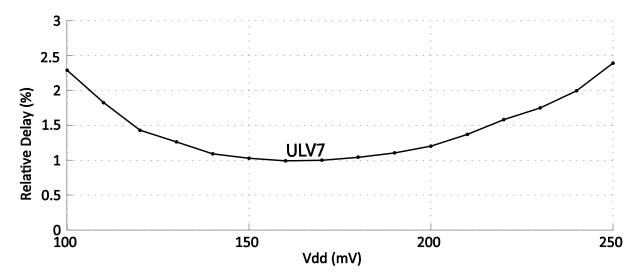

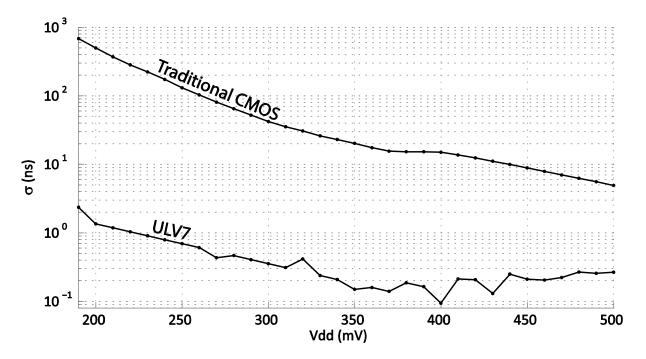

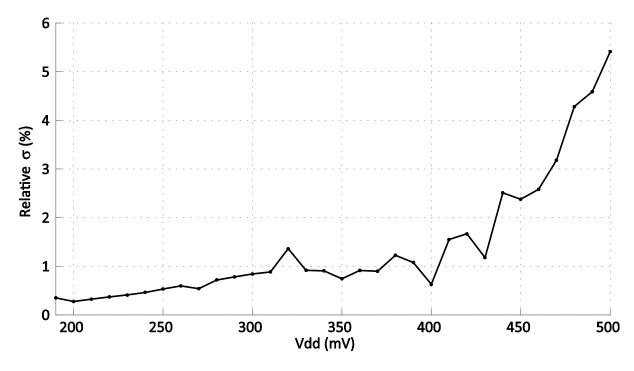

The delay for both inverters is highly dependent on the supply voltage, but the ULV7 circuit is less affected by voltage changes than the standard inverter is.